- 您现在的位置:买卖IC网 > PDF目录16855 > EVAL-ADF4158EB1Z (Analog Devices Inc)BOARD EVALUATION FOR ADF4158 PDF资料下载

参数资料

| 型号: | EVAL-ADF4158EB1Z |

| 厂商: | Analog Devices Inc |

| 文件页数: | 32/36页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION FOR ADF4158 |

| 标准包装: | 1 |

| 主要目的: | 计时,频率合成器 |

| 嵌入式: | 否 |

| 已用 IC / 零件: | ADF4158 |

| 主要属性: | 单路分数-N PLL |

| 已供物品: | 板 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页当前第32页第33页第34页第35页第36页

Data Sheet

ADF4158

Rev. G | Page 5 of 36

C Version1

Parameter

Min

Typ

Max

Unit

Test Conditions/Comments

NOISE CHARACTERISTICS

Normalized Phase Noise Floor

(PNSYNTH)4

216

dBc/Hz

PLL loop bandwidth = 500 kHz;

measured at 100 kHz offset

Normalized 1/f Noise (PN1_f)5

110

dBc/Hz

100 kHz offset; normalized to 1 GHz

Phase Noise Performance6

At VCO output

5805 MHz Output7

93

dBc/Hz

At 5 kHz offset, 32 MHz PFD frequency

1 Operating temperature for C version: 40°C to +125°C.

2 AC coupling ensures AVDD/2 bias.

3 Guaranteed by design. Sample tested to ensure compliance.

4 The synthesizer phase noise floor is estimated by measuring the in-band phase noise at the output of the VCO and subtracting 20 log(N) (where N is the N divider

value) and 10 log(fPFD). PNSYNTH = PNTOT 10 log(fPFD) 20 log(N).

5 The PLL phase noise is composed of 1/f (flicker) noise plus the normalized PLL noise floor. The formula for calculating the 1/f noise contribution at an RF frequency, fRF,

and at a frequency offset f is given by PN = PN1_f + 10 log(10 kHz/f) + 20 log(fRF/1 GHz). Both the normalized phase noise floor and flicker noise are modeled in ADIsimPLL.

6 The phase noise is measured with the EVAL-ADF4158EB1Z and the Agilent E5052A phase noise system.

7 fREFIN = 128 MHz; fPFD = 32 MHz; offset frequency = 5 kHz; RFOUT = 5805 MHz; INT = 181; FRAC = 13631488; loop bandwidth = 100 kHz.

TIMING SPECIFICATIONS

AVDD = DVDD = SDVDD = 2.7 V to 3.3 V; VP = AVDD to 5.5 V; AGND = DGND = SDGND = 0 V; TA = TMIN to TMAX, dBm referred to 50 Ω,

unless otherwise noted.

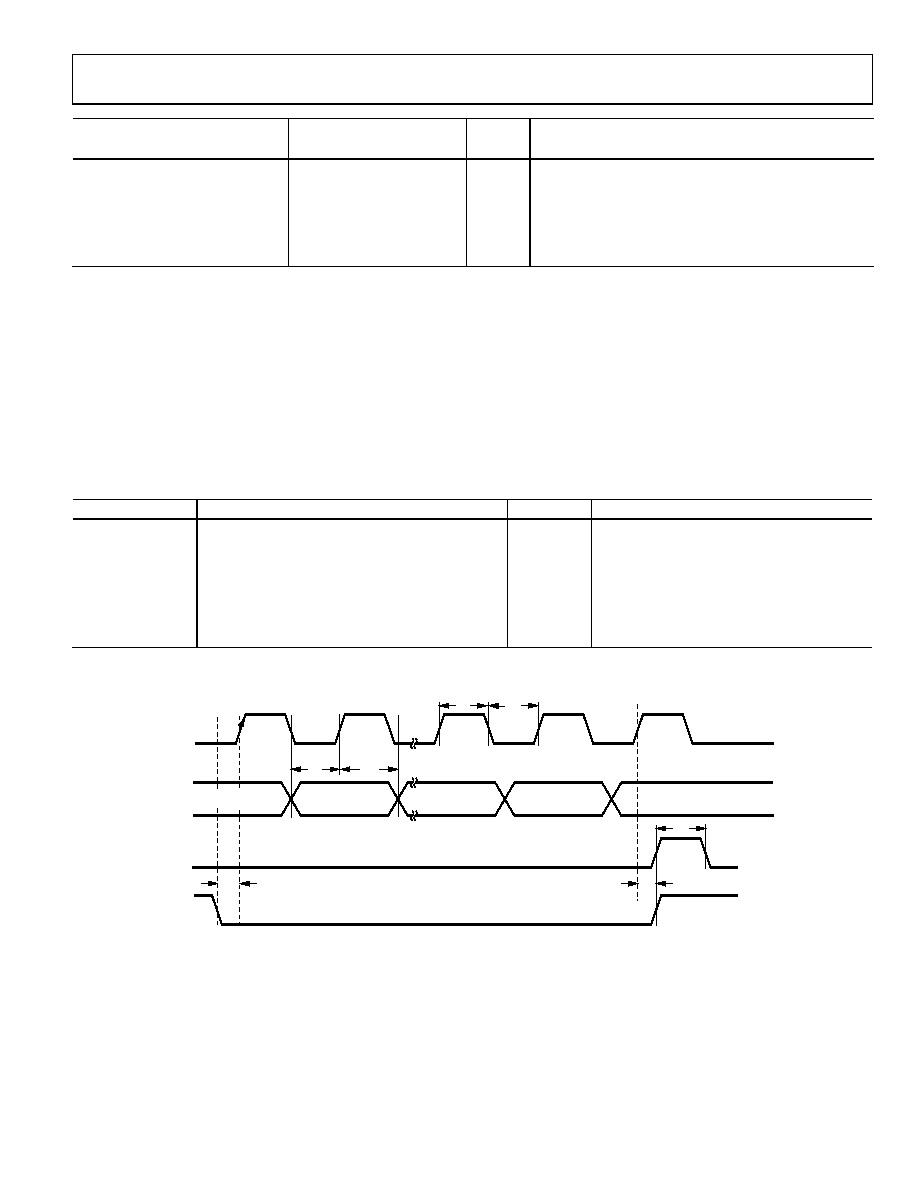

Table 2. Write Timing

Parameter

Limit at TMIN to TMAX (C Version)

Unit

Test Conditions/Comments

t1

20

ns min

LE setup time

t2

10

ns min

DATA to CLK setup time

t3

10

ns min

DATA to CLK hold time

t4

25

ns min

CLK high duration

t5

25

ns min

CLK low duration

t6

10

ns min

CLK to LE setup time

t7

20

ns min

LE pulse width

Write Timing Diagram

CLK

DATA

LE

DB31 (MSB)

DB30

DB1

(CONTROL BIT C2)

DB2

(CONTROL BIT C3)

DB0 (LSB)

(CONTROL BIT C1)

t1

t2

t3

t7

t6

t4

t5

08

72

8-

02

6

Figure 2. Write Timing Diagram

相关PDF资料 |

PDF描述 |

|---|---|

| RNF-100-1/8-BK-STK | HEATSHRINK RNF-100 1/8"X4' BLK |

| M3CCA-1418R | IDC CABLE - MKC14A/MC14M/MKC14A |

| M3AAA-1418R | IDC CABLE - MSC14A/MC14M/MSC14A |

| H1AXH-3036G | IDC CABLE - HSC30H/AE30G/X |

| A3AAH-1036G | IDC CABLE - ASC10H/AE10G/ASC10H |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-ADF4193EBZ1 | 功能描述:BOARD EVALUATION EB1 FOR ADF4193 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

| EVAL-ADF4193EBZ2 | 功能描述:BOARD EVALUATION EB2 FOR ADF4193 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

| EVAL-ADF4206-7EB1 | 制造商:Analog Devices 功能描述:EVALUATION BOARD FOR DUAL RF PLL FREQUENCY SYNTHESIZERS 制造商:Analog Devices 功能描述:DUAL RF PLL FREQ SYNTHESIZERS - Bulk |

| EVAL-ADF4208EB1 | 制造商:Analog Devices 功能描述:Evaluation Board For Dual RF PLL Frequency Synthesizers 制造商:Analog Devices 功能描述:DUAL RF PLL FREQ SYNTHESIZERS - Bulk |

| EVAL-ADF4212EB1 | 制造商:Analog Devices 功能描述:EVALUATION BOARD I.C. - Bulk |

发布紧急采购,3分钟左右您将得到回复。