- 您现在的位置:买卖IC网 > PDF目录371807 > HFA3861AIN96 (INTERSIL CORP) Circular Connector; No. of Contacts:21; Series:MS27473; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:22; Circular Contact Gender:Socket; Circular Shell Style:Straight Plug; Insert Arrangement:22-21 RoHS Compliant: No PDF资料下载

参数资料

| 型号: | HFA3861AIN96 |

| 厂商: | INTERSIL CORP |

| 元件分类: | 无绳电话/电话 |

| 英文描述: | Circular Connector; No. of Contacts:21; Series:MS27473; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:22; Circular Contact Gender:Socket; Circular Shell Style:Straight Plug; Insert Arrangement:22-21 RoHS Compliant: No |

| 中文描述: | TELECOM, CELLULAR, BASEBAND CIRCUIT, PQFP64 |

| 封装: | 10 X 10 MM, PLASTIC, MS-026ACD, TQFP-64 |

| 文件页数: | 25/37页 |

| 文件大小: | 440K |

| 代理商: | HFA3861AIN96 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页当前第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页

25

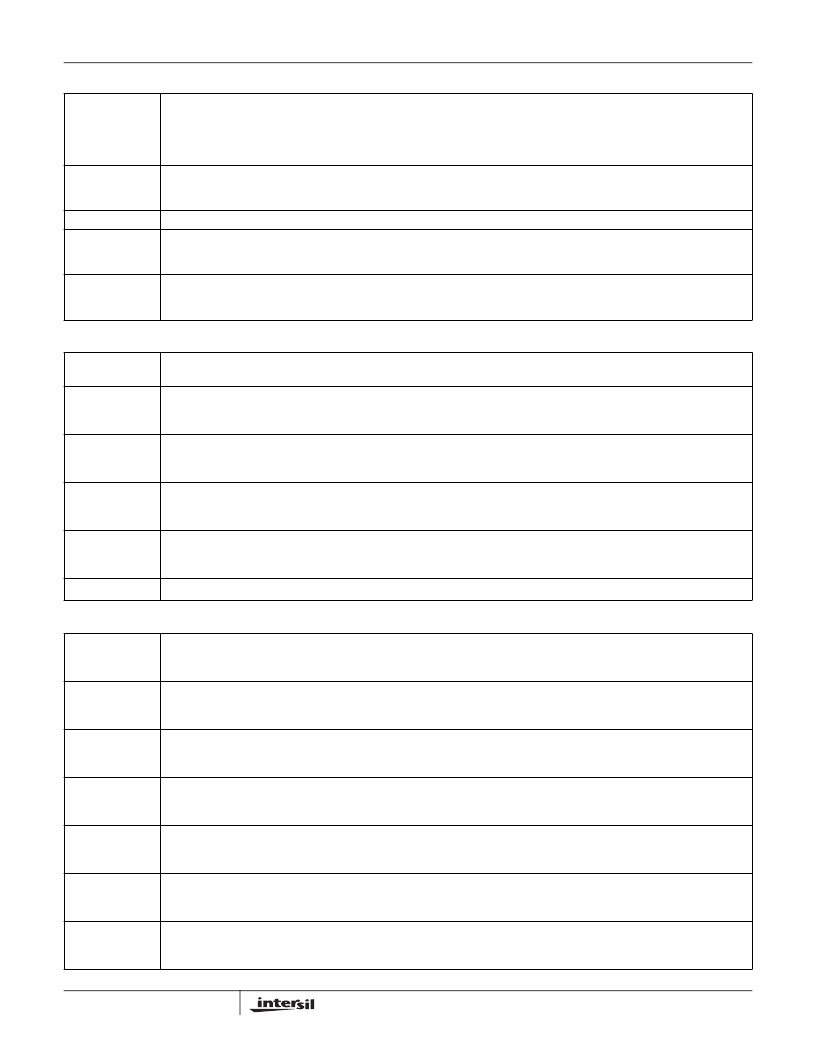

Bits 5:4

SFD Time-out values

00 = 56

μ

s

01 = 64

μ

s

10 = 128

μ

s

11 = 144

μ

s

Bit 3

MD_RDY control

0 = After CRC16

1 = After SFD

Bit 2

Force F. O. E. in all antenna diversity timelines.

Bit 1

Antenna choice for Receiver when single antenna acquisition is selected

0 = Antenna select pin low

1 = Antenna select pin high

Bit 0

Single or dual antenna acquire

0 = dual antenna for diversity acquisition

1 = single antenna

CONFIGURATION REGISTER 10 ADDRESS (14h) R/W RX CONFIGURE (Continued)

CONFIGURATION REGISTER 11 ADDRESS (16h) R/W RX-TX CONFIGURE

Bit 7

Continuous internal RX 22 and 44MHz clocks; (Only Reset active will stop) overrides CR10 bit 6. This bit should be loaded to

a “1” then to a “0” during initial register loading to ensure receiver initialization.

Bit 6

A/D input coupling

0 = DC

1 = AC (external bias network required)

Bit 5

TX filter / CMF weight select

0 = US

1 = Japan

Bit 4

Ping Pong Differential Encode enable

0 = disabled Ping Pong Differential encoding

1 = normal Ping Pong Differential encoding

Bit 3

CCA mode

0 = normal CCA. CCA will immediately respond to changes in ED, CS1, and SQ1 as configured

1 = Sampled CCA. CCA will update once per slot (20

μ

s), will be valid at 19.8

μ

s or 15.8

μ

s as determined by CR9 bit 7.

Bits 2:0

Precursor value in CIR estimate

CONFIGURATION REGISTER 12 ADDRESS (18h) R/W A/D TEST MODES 1

Bit 7

All DAC and A/D clock source control

0 = normal internal clocks

1 = clock via SDI pin

Bit 6

TX DAC clock

0 = enable

1 = disable

Bit 5

RX DAC clock

0 = enable

1 = disable

Bit 4

I DAC clock

0 = enable

1 = disable

Bit 3

Q DAC clock

0 = enable

1 = disable

Bit 2

RF A/D clock

0 = enable

1 = disable

Bit 1

I A/D clock

0 = enable

1 = disable

HFA3861A

相关PDF资料 |

PDF描述 |

|---|---|

| HFA3861AIN | 288 MACROCELL 3.3 VOLT ISP CPLD |

| HFA3863IN | Direct Sequence Spread Spectrum Baseband Processor |

| HFA3863IN96 | Direct Sequence Spread Spectrum Baseband Processor |

| HFA3863 | Direct Sequence Spread Spectrum Baseband Processor(直接序列扩谱基带处理器) |

| HFA3983IV96 | 2.4GHz Power Amplifier and Detector |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HFA3861B | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband Processor |

| HFA3861BIN | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband Processor |

| HFA3861BIN96 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband Processor |

| HFA3861IV | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband Processor |

| HFA3861IV96 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband Processor |

发布紧急采购,3分钟左右您将得到回复。