- 您现在的位置:买卖IC网 > PDF目录371807 > HFA3861AIN96 (INTERSIL CORP) Circular Connector; No. of Contacts:21; Series:MS27473; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:22; Circular Contact Gender:Socket; Circular Shell Style:Straight Plug; Insert Arrangement:22-21 RoHS Compliant: No PDF资料下载

参数资料

| 型号: | HFA3861AIN96 |

| 厂商: | INTERSIL CORP |

| 元件分类: | 无绳电话/电话 |

| 英文描述: | Circular Connector; No. of Contacts:21; Series:MS27473; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:22; Circular Contact Gender:Socket; Circular Shell Style:Straight Plug; Insert Arrangement:22-21 RoHS Compliant: No |

| 中文描述: | TELECOM, CELLULAR, BASEBAND CIRCUIT, PQFP64 |

| 封装: | 10 X 10 MM, PLASTIC, MS-026ACD, TQFP-64 |

| 文件页数: | 29/37页 |

| 文件大小: | 440K |

| 代理商: | HFA3861AIN96 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页当前第29页第30页第31页第32页第33页第34页第35页第36页第37页

29

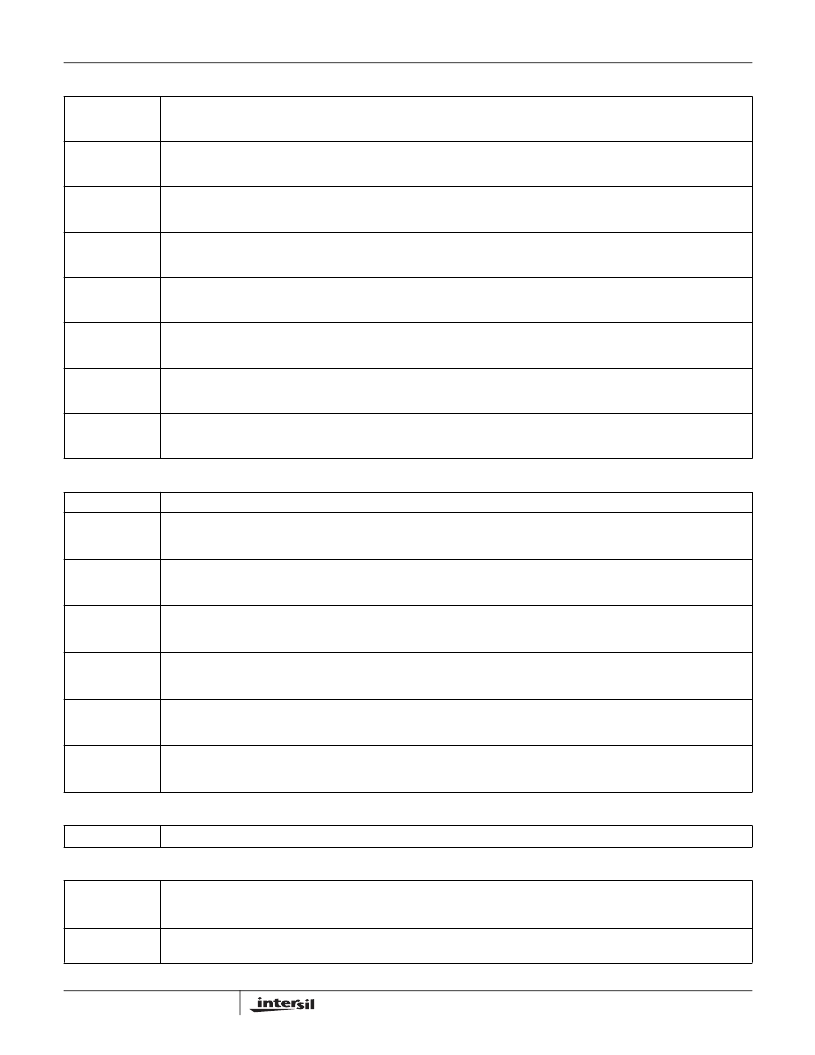

CONFIGURATION REGISTER 32 ADDRESS (40h) R/W TEST MODES 1

Bit 7

Selection bit for DAC input test mode 7

0 = Barker

1 = Low rate I/Q samples

Bit 6

force high rate mode

0 = normal

1 = force high rate mode

Bit 5

TX 44 clock enable

0 = Normal

1 = enabled

Bit 4

Tristate test bus and enable inputs

0 = Normal

1 = enable inputs on test bus

Bit 3

Disable spread sequence for 1 and 2Mbps

0 = Normal

1 = disabled

Bit 2

Disable scrambler

0 = normal scrambler operation

1 = scrambler disabled (taps set to 0)

Bit 1

PN generator enable (RX 44MHz clock)

0 = not enabled

1 = enabled. Bit must first be written to a ‘0’ before a ‘1’ to initialize logic.

Bit 0

PN generator enable (RX 22MHz clock)

0 = not enabled

1 = enabled. Bit must first be written to a ‘0’ before a ‘1’ to initialize logic.

CONFIGURATION REGISTER ADDRESS 33 (42h) R/W TEST MODES 2

Bits 7:6

Unused, set to 0

Bit 5

DC offset control

0 = enable DC offset compensation

1 = disable DC offset compensation

Bit 4

Bypass I/Q A/Ds.

0 = disable bypass

1 = 4 MSBs of I/Q data are input on test bus. TESTin 3:0 is [5:2], TESTin 7:4 is Q[5:2], LSBs are zeroed.

Bit 3

disable time adjust

0 = normal

1 = disabled

Bit 2

Internal digital loop back mode (SDI pin becomes LOCK input to acquisition block)

0 = normal chip operation loop back disabled

1 = loop back enabled, A/D and D/A converters bypassed, chip will not respond to external signals

Bit 1

enable PN to lower test bus address (2-0)

0 = normal

1 = PN to test bus address

Bit 0

enable PN to upper test bus address (7-3)

0 = normal

1 = PN to test bus address

CONFIGURATION REGISTER ADDRESS 34 (44h) R/W TEST BUS ADDRESS

Bits 7:0

address bits for various tests. See Tech Brief #TBD for a description of the factory test modes

CONFIGURATION REGISTER ADDRESS 35 (46h) R/W CMF COEFFICIENT CONTROL THRESHOLD

Bit 7

Threshold control

0 = threshold is relative to noise floor

1 = threshold is absolute.

Bit 6:0

Threshold. For 100% calculated weights, set to 80h and set CR19[7:4] to 02h. For 100% default weights, set to 7fh and set

CR19[7:4] to 00h.

HFA3861A

相关PDF资料 |

PDF描述 |

|---|---|

| HFA3861AIN | 288 MACROCELL 3.3 VOLT ISP CPLD |

| HFA3863IN | Direct Sequence Spread Spectrum Baseband Processor |

| HFA3863IN96 | Direct Sequence Spread Spectrum Baseband Processor |

| HFA3863 | Direct Sequence Spread Spectrum Baseband Processor(直接序列扩谱基带处理器) |

| HFA3983IV96 | 2.4GHz Power Amplifier and Detector |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HFA3861B | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband Processor |

| HFA3861BIN | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband Processor |

| HFA3861BIN96 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband Processor |

| HFA3861IV | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband Processor |

| HFA3861IV96 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband Processor |

发布紧急采购,3分钟左右您将得到回复。