- 您现在的位置:买卖IC网 > Datasheet目录983 > HI5762EVAL2 (Intersil)EVALUATION MOD FOR HI5762 AMP Datasheet资料下载

参数资料

| 型号: | HI5762EVAL2 |

| 厂商: | Intersil |

| 文件页数: | 2/17页 |

| 文件大小: | 0K |

| 描述: | EVALUATION MOD FOR HI5762 AMP |

| 标准包装: | 1 |

| ADC 的数量: | 2 |

| 位数: | 10 |

| 采样率(每秒): | 60M |

| 数据接口: | 并联 |

| 输入范围: | 1 Vpp |

| 在以下条件下的电源(标准): | 650mW @ 60MSPS |

| 工作温度: | -40°C ~ 85°C |

| 已用 IC / 零件: | HI5762 |

| 已供物品: | 板 |

�� �

�

�

�Application� Note� 9811�

�Evaluation� Board� Layout� and� Power�

�Supplies�

�The� HI5762� evaluation� board� is� a� four� layer� board� with� a�

�layout� optimized� for� the� best� performance� of� the� ADC.�

�Included� in� the� application� note� are� electrical� schematics� of�

�the� evaluation� board,� a� component� parts� list,� a� component�

�placement� layout� drawing� and� reproductions� of� the� various�

�board� layers� used� in� the� board� stack-up.� The� user� should�

�feel� free� to� copy� the� layout� in� their� application.� Refer� to� the�

�component� layout� and� the� evaluation� board� electrical�

�schematic� for� the� following� discussions.�

�The� HI5762� monolithic� A/D� converter� has� been� designed�

�with� separate� analog� and� digital� supply� and� ground� pins� to�

�keep� digital� noise� out� of� the� analog� signal� path.� The�

�evaluation� board� provides� separate� low� impedance� analog�

�and� digital� ground� planes� on� layer� 2.� Since� the� analog� and�

�digital� ground� planes� are� connected� together� at� a� single�

�point� where� the� power� supplies� enter� the� board,� DO� NOT� tie�

�them� together� back� at� the� power� supplies.�

�The� analog� and� digital� power� planes� are� also� kept� separate�

�on� the� evaluation� board� and� should� be� driven� by� clean� linear�

�regulated� supplies.� The� external� power� supplies� are� hooked�

�up� with� the� twisted� pair� wires� soldered� to� the� plated� through�

�holes� marked� +5VAIN,� +5VAIN1,� -5VAIN,� +5VDIN,�

�+5VD1IN,� +5VD2IN,� AGND� and� DGND.� The� +5VDIN,�

�+5VD1IN� and� +5VD2IN� are� digital� supplies� and� are� returned�

�to� DGND.� The� +5VAIN,� +5VAIN1� and� -5VAIN� are� the� analog�

�supplies� and� are� returned� to� AGND.� Table� 1� lists� the�

�operational� supply� voltages,� typical� current� consumption� and�

�the� evaluation� board� circuit� function� being� powered.� Single�

�supply� operation� of� the� converter� is� possible� but� the� overall�

�performance� of� the� converter� may� degrade.�

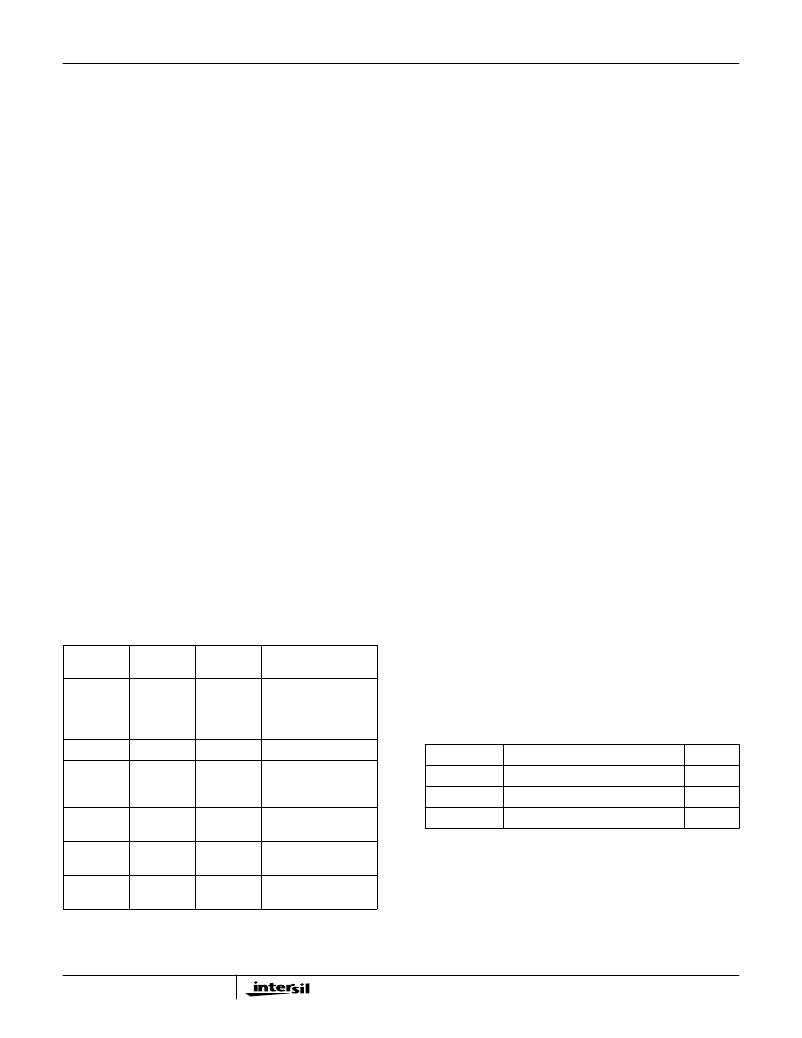

�TABLE� 1.� HI5762EVAL2� EVALUATION� BOARD� POWER�

�SUPPLIES�

�Sample� Clock� Driver,� Timing� and� I/O�

�In� order� to� ensure� rated� performance� of� the� HI5762,� the� duty�

�cycle� of� the� sample� clock� should� be� held� at� 50%� ±� 5%.� It� must�

�also� have� low� phase� noise� and� operate� at� standard� TTL� levels.�

�A� CMOS� inverter� (U7)� used� as� a� voltage� comparator� is�

�provided� on� the� evaluation� board� to� generate� the� sampling�

�clock� for� the� HI5762� when� a� sinewave� (<� 2V� p-p� )� or�

�squarewave� clock� is� applied� to� the� CLK� input� (J3)� of� the�

�evaluation� board.� A� potentiometer� (VR2)� is� provided� to� allow�

�the� user� to� adjust� the� duty� cycle� of� the� sampling� clock� to�

�obtain� the� best� performance� from� the� ADC� and� to� allow� the�

�user� to� investigate� the� effects� of� expected� duty� cycle�

�variations� on� the� performance� of� the� converter.� The� HI5762�

�clock� input� trigger� level� is� approximately� 1.5V.� Therefore,� the�

�duty� cycle� of� the� sampling� clock� should� be� measured� at� this�

�1.5V� trigger� level.� U7-2� provides� a� convenient� point� to�

�monitor� the� sample� clock� duty� cycle� and� make� any� required�

�adjustments.�

�Figure� 2� shows� the� sample� clock� and� digital� data� timing�

�relationship� for� the� evaluation� board.� The� data�

�corresponding� to� a� particular� sample� will� be� available� at� the�

�digital� data� outputs� of� the� HI5762� after� the� data� latency� time,�

�t� LAT� ,� of� 6� sample� clock� cycles� plus� the� HI5762� digital� data�

�output� delay,� t� OD� .� Table� 2� lists� the� values� that� can� be�

�expected� for� the� indicated� timing� delays.� Refer� to� the� HI5762�

�data� sheet� for� additional� timing� information.�

�The� sample� clock� and� digital� output� data� signals� are� made�

�available� through� two� connectors� contained� on� the�

�evaluation� board.� The� line� buffering� provided� by� the� data�

�output� latches� allows� for� driving� long� leads� or� analyzer�

�inputs.� These� data� latches� are� not� necessary� for� the� digital�

�output� data� if� the� load� presented� to� the� converter� does� not�

�exceed� the� data� sheet� load� limits� of� 100mA� and� 15pF.� The�

�P2� I/O� connector� allows� the� evaluation� board� to� be�

�POWER�

�SUPPLY�

�+5VAIN�

�NOMINAL�

�VALUE�

�5.0V� ±� 5%�

�CURRENT�

�(TYP)�

�51mA�

�FUNCTION(S)�

�SUPPLIED�

�Analog� Input� Op� Amps,�

�Reference� Voltage� Op�

�Amps,� Bandgap� Refer-�

�interfaced� to� the� DSP� evaluation� boards� available� from�

�Intersil.� Alternatively,� the� digital� output� data� and� sample�

�clock� can� also� be� accessed� by� clipping� the� test� leads� of� a�

�logic� analyzer� or� data� acquisition� system� onto� the� I/O� pins� of�

�connector� header� P1.�

�ence�

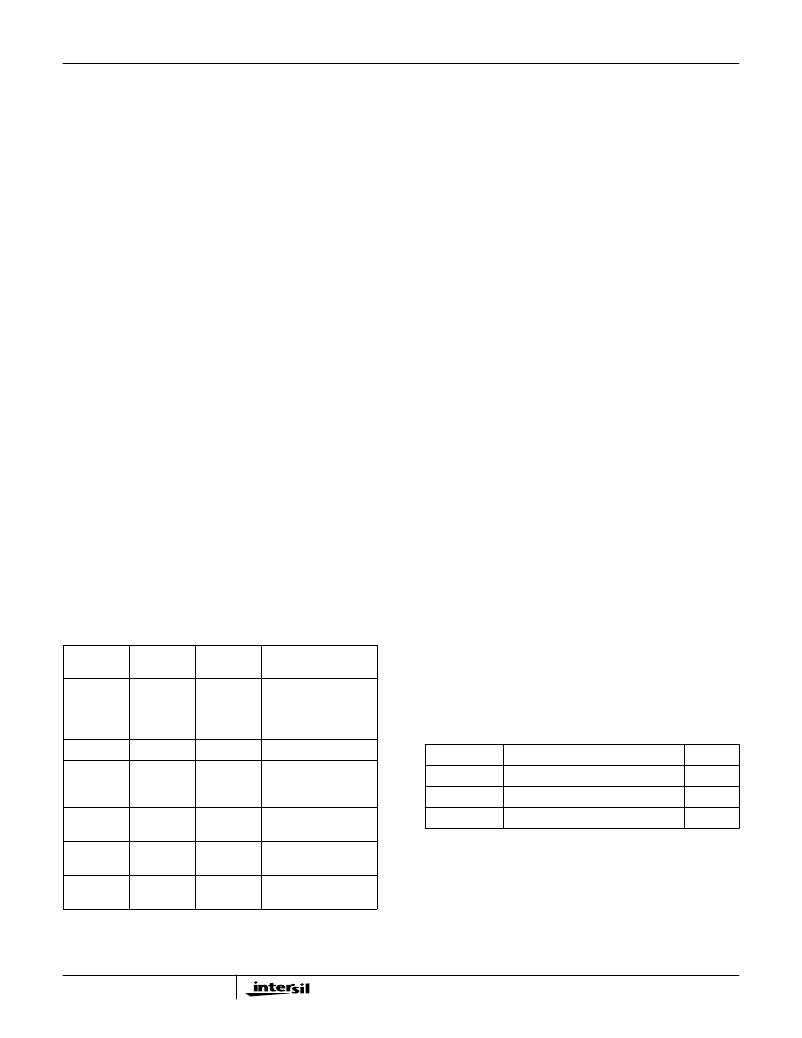

�TABLE� 2.� TIMING� SPECIFICATIONS�

�+5VA1IN�

�-5VAIN�

�5.0V� ±� 5%�

�-5.0V� ±� 5%�

�73mA�

�50mA�

�A/D� AV� CC1� and� AV� CC2�

�Analog� Input� Op� Amps,�

�Reference� Voltage� Op�

�PARAMETER�

�t� OD�

�DESCRIPTION�

�HI5762� Digital� Output� Data� Delay�

�TYP�

�50ns�

�Amps�

�t� PD1�

�U7� Prop� Delay�

�9ns�

�+5VDIN�

�5.0V� ±� 5%�

�15mA�

�Sample� Clock� Genera-�

�t� PD2�

�U10/11� Prop� Delay�

�4.5ns�

�tor� and� D-FF’s�

�+5VD1IN�

�5.0V� ±� 5%�

�61mA�

�A/D� DV� CC1� and�

�HI5762� Performance� Characterization�

�DV� CC2�

�Dynamic� testing� is� used� to� evaluate� the� performance� of� the�

�+5VD2IN�

�5.0V� ±� 5%� or�

�3.0V� ±� 10%�

�4.5mA�

�A/D� DV� CC3�

�HI5762� A/D� converter.� Among� the� tests� performed� are�

�Signal-to-Noise� and� Distortion� Ratio� (SINAD),� Signal-to-�

�Noise� Ratio� (SNR),� Total� Harmonic� Distortion� (THD),�

�Spurious� Free� Dynamic� Range� (SFDR)� and� Intermodulation�

�Distortion� (IMD).�

�3-2�

�相关PDF资料 |

PDF描述 |

|---|---|

| HI5767EVAL1 | EVALUATION PLATFORM HI5767 |

| HI5767EVAL2 | EVALUATION PLATFORM HI5767 |

| HI5805EVAL1 | EVALUATION PLATFORM HI5805 |

| HI5828EVAL2 | EVALUATION PLATFORM HI5828 |

| HI5960SOICEVAL1 | EVALUATION PLATFORM SOIC HI5960 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HI5766 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:10-Bit, 60 MSPS A/D Converter |

| HI5766_05 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:10-Bit, 60MSPS A/D Converter |

| HI5766EVAL1 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Harris Corporation 功能描述: |

| HI5766KCA | 功能描述:IC ADC 10-BIT 60MSPS 28-SSOP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:12 采样率(每秒):3M 数据接口:- 转换器数目:- 功率耗散(最大):- 电压电源:- 工作温度:- 安装类型:表面贴装 封装/外壳:SOT-23-6 供应商设备封装:SOT-23-6 包装:带卷 (TR) 输入数目和类型:- |

| HI5766KCAZ | 功能描述:模数转换器 - ADC A/D 10-BIT 60MSPS 28 SSOP COM TEMP RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

发布紧急采购,3分钟左右您将得到回复。