- 您现在的位置:买卖IC网 > PDF目录371821 > HIP6018 (Intersil Corporation) FPGA - 100000 SYSTEM GATE 2.5 VOLT - NOT RECOMMENDED for NEW DESIGN PDF资料下载

参数资料

| 型号: | HIP6018 |

| 厂商: | Intersil Corporation |

| 元件分类: | FPGA |

| 英文描述: | FPGA - 100000 SYSTEM GATE 2.5 VOLT - NOT RECOMMENDED for NEW DESIGN |

| 中文描述: | 先进的双PWM和线性功率控制 |

| 文件页数: | 7/14页 |

| 文件大小: | 133K |

| 代理商: | HIP6018 |

2-230

VIN2 (Pin 12)

This pin supplies power to the internal regulator. Connect

this pin to a suitable 3.3V source.

Additionally, this pin is used to monitor the 3.3V supply. If,

following a startup cycle, the voltage drops below 2.05V

(typically), the chip shuts down. A new soft-start cycle is

initiated upon return of the 3.3V supply above the under-

voltage threshold.

Description

Operation

The HIP6018 monitors and precisely controls 4 output

voltage levels (Refer to Figures 1, 2, and 3). It is designed for

microprocessor computer applications with 3.3V and 5V

power, and 12V bias input from an ATX power supply. The IC

has one PWM controller, a linear controller, and a linear

regulator. The PWM controller is designed to regulate the

microprocessor core voltage (V

OUT1

) by driving 2 MOSFETs

(Q1 and Q2) in a synchronous-rectified buck converter

configuration. The core voltage is regulated to a level

programmed by the 5-bit digital-to-analog converter (DAC).

An integrated linear regulator supplies the 2.5V clock power

(V

OUT2

). The linear controller drives an external MOSFET

(Q3) to supply the GTL bus power (V

OUT3

).

Initialization

The HIP6018 automatically initializes upon receipt of input

power. Special sequencing of the input supplies is not

necessary. The Power-On Reset (POR) function continually

monitors the input supply voltages. The POR monitors the

bias voltage (+12V

IN

) at the VCC pin, the 5V input voltage

(+5V

IN

) on the OCSET1 pin, and the 3.3V input on the VIN2

pin. The normal level on OCSET1 is equal to +5V

IN

less a

fixed voltage drop (see over-current protection). The POR

function initiates soft-start operation after all three input supply

voltages exceed their POR thresholds.

Soft-Start

The POR function initiates the soft-start sequence. Initially,

the voltage on the SS pin rapidly increases to approximately

1V (this minimizes the soft-start interval). Then an internal

11

μ

A current source charges an external capacitor (C

SS

) on

the SS pin to 4V. The PWM error amplifier reference input (+

terminal) and output (COMP1 pin) is clamped to a level

proportional to the SS pin voltage. As the SS pin voltage

slews from 1V to 4V, the output clamp generates PHASE

pulses of increasing width that charge the output

capacitor(s). After this initial stage, the reference input clamp

slows the output voltage rate-of-rise and provides a smooth

transition to the final set voltage. Additionally both linear

regulator’s reference inputs are clamped to a voltage

proportional to the SS pin voltage. This method provides a

rapid and controlled output voltage rise.

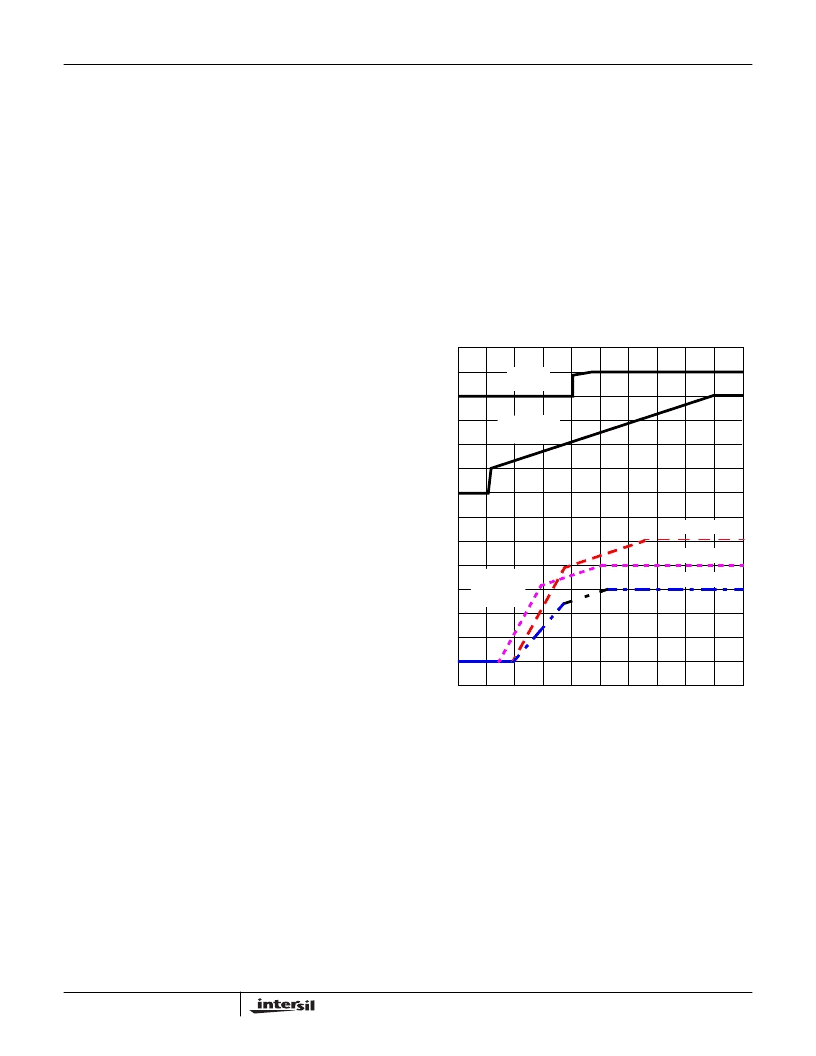

Figure 3 shows the soft-start sequence for the typical

application. At T0 the SS voltage rapidly increases to

approximately 1V. At T1, the SS pin and error amplifier

output voltage reach the valley of the oscillator’s triangle

wave. The oscillator’s triangular waveform is compared to

the clamped error amplifier output voltage. As the SS pin

voltage increases, the pulse-width on the PHASE pin

increases. The interval of increasing pulse-width continues

until each output reaches sufficient voltage to transfer

control to the input reference clamp. If we consider the 2.0V

output (V

OUT1

) in Figure 3, this time occurs at T2. During

the interval between T2 and T3, the error amplifier

reference ramps to the final value and the converter

regulates the output to a voltage proportional to the SS pin

voltage. At T3 the input clamp voltage exceeds the

reference voltage and the output voltage is in regulation.

The remaining outputs are also programmed to follow the SS

pin voltage. Each linear output (V

OUT2

and V

OUT3

) initially

follows a ramp similar to that of the PWM output. When each

output reaches sufficient voltage the input reference clamp

slows the rate of output voltage rise. The PGOOD signal

toggles ‘high’ when all output voltage levels have exceeded

their under-voltage levels. See the Soft-Start Interval section

under Applications Guidelines for a procedure to determine

the soft-start interval.

Fault Protection

All three outputs are monitored and protected against

extreme overload. A sustained overload on any linear

FIGURE 6. SOFT-START INTERVAL

0V

0V

0V

TIME

PGOOD

(2V/DIV)

SOFT-START

(1V/DIV)

OUTPUT

VOLTAGES

(0.5V/DIV)

V

OUT1

(DAC = 2V)

V

OUT2

( = 2.5V)

V

OUT3

( = 1.5V)

T1

T2

T3

T0

T4

HIP6018

相关PDF资料 |

PDF描述 |

|---|---|

| HIP6018CB | Advanced PWM and Dual Linear Power Control |

| HIP6019BCB | Advanced Dual PWM and Dual Linear Power Control |

| HIP6019B | FPGA - 100000 SYSTEM GATE 2.5 VOLT - NOT RECOMMENDED for NEW DESIGN |

| HIP6028EVAL1 | Advanced PWM and Dual Linear Power Control with Integrated ACPI Support Interface |

| HIP6028 | Advanced PWM and Dual Linear Power Control with Integrated ACPI Support Interface |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HIP6018B | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Advanced PWM and Dual Linear Power Control |

| HIP6018B_05 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Advanced PWM and Dual Linear Power Control |

| HIP6018BCB | 功能描述:IC REG TRPL BCK/LINEAR 24-SOIC RoHS:否 类别:集成电路 (IC) >> PMIC - 稳压器 - 线性 + 切换式 系列:- 标准包装:2,500 系列:- 拓扑:降压(降压)同步(3),线性(LDO)(2) 功能:任何功能 输出数:5 频率 - 开关:300kHz 电压/电流 - 输出 1:控制器 电压/电流 - 输出 2:控制器 电压/电流 - 输出 3:控制器 带 LED 驱动器:无 带监控器:无 带序列发生器:是 电源电压:5.6 V ~ 24 V 工作温度:-40°C ~ 85°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

| HIP6018BCB-T | 功能描述:IC REG TRPL BCK/LINEAR 24-SOIC RoHS:否 类别:集成电路 (IC) >> PMIC - 稳压器 - 线性 + 切换式 系列:- 标准包装:2,500 系列:- 拓扑:降压(降压)同步(3),线性(LDO)(2) 功能:任何功能 输出数:5 频率 - 开关:300kHz 电压/电流 - 输出 1:控制器 电压/电流 - 输出 2:控制器 电压/电流 - 输出 3:控制器 带 LED 驱动器:无 带监控器:无 带序列发生器:是 电源电压:5.6 V ~ 24 V 工作温度:-40°C ~ 85°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

| HIP6018BCBZ | 功能描述:电压模式 PWM 控制器 ADV DL PWM "3 IN1" W/LWER DAC RNG RoHS:否 制造商:Texas Instruments 输出端数量:1 拓扑结构:Buck 输出电压:34 V 输出电流: 开关频率: 工作电源电压:4.5 V to 5.5 V 电源电流:600 uA 最大工作温度:+ 125 C 最小工作温度:- 40 C 封装 / 箱体:WSON-8 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。