- 您现在的位置:买卖IC网 > PDF目录371822 > HIP6500BEVAL1 (Intersil Corporation) Multiple Linear Power Controller with ACPI Control Interface PDF资料下载

参数资料

| 型号: | HIP6500BEVAL1 |

| 厂商: | Intersil Corporation |

| 元件分类: | 基准电压源/电流源 |

| 英文描述: | Multiple Linear Power Controller with ACPI Control Interface |

| 中文描述: | 多重线性电源控制器ACPI控制接口 |

| 文件页数: | 12/15页 |

| 文件大小: | 156K |

| 代理商: | HIP6500BEVAL1 |

12

Placement of the decoupling and bulk capacitors should

follow a placement reflecting their purpose. As such, the

high-frequency decoupling capacitors should be placed as

close as possible to the load they are decoupling; the ones

decoupling the controller close to the controller pins, the

ones decoupling the load close to the load connector or the

load itself (if embedded). Even though bulk capacitance

(aluminum electrolytics or tantalum capacitors) placement is

not as critical as the high-frequency capacitor placement,

having these capacitors close to the load they serve is

preferable.

The only critical small signal component is the soft-start

capacitor, C

SS

. Locate this component close to SS pin of the

control IC and connect to ground through a via placed close

to the capacitor’s ground pad. Minimize any leakage current

paths from SS node, since the internal current source is only

10

μ

A.

d

A multi-layer printed circuit board is recommended. Figure

12 shows the connections of most of the components in the

converter. Note that the individual capacitors each could

represent numerous physical capacitors. Dedicate one solid

layer for a ground plane and make all critical component

ground connections through vias placed as close to the

component terminal as possible. Dedicate another solid

layer as a power plane and break this plane into smaller

islands of common voltage levels. Ideally, the power plane

should support both the input power and output power

nodes. Use copper filled polygons on the top and bottom

circuit layers to create power islands connecting the filtering

components (output capacitors) and the loads. Use the

remaining printed circuit layers for small signal wiring.

Component Selection Guidelines

Output Capacitors Selection

The output capacitors for all outputs should be selected to

allow the output voltage to meet the dynamic regulation

requirements of active state operation (S0, S1). The load

transient for the various microprocessor system’s

components may require high quality capacitors to supply

the high slew rate (di/dt) current demands. Thus, it is

recommended that the output capacitors be selected for

transient load regulation, paying attention to their parasitic

components (ESR, ESL).

Also, during the transition between active and sleep states,

there is a short interval of time during which none of the

power pass elements are conducting - during this time the

output capacitors have to supply all the output current. The

output voltage drop during this brief period of time can be

easily approximated with the following formula:

×

=

, where

V

OUT

- output voltage drop

ESR

OUT

- output capacitor bank ESR

I

OUT

- output current during transition

C

OUT

- output capacitor bank capacitance

t

t

- active-to-sleep or sleep-to-active transition time (10

μ

s typ).

The output voltage drop is heavily dependent on the ESR

(equivalent series resistance) of the output capacitor bank,

the choice of capacitors should be such as to maintain the

output voltage above the lowest allowable regulation level.

V

CLK

(V

OUT4

) Output Capacitors Selection

The output capacitor for the V

CLK

linear regulator provides

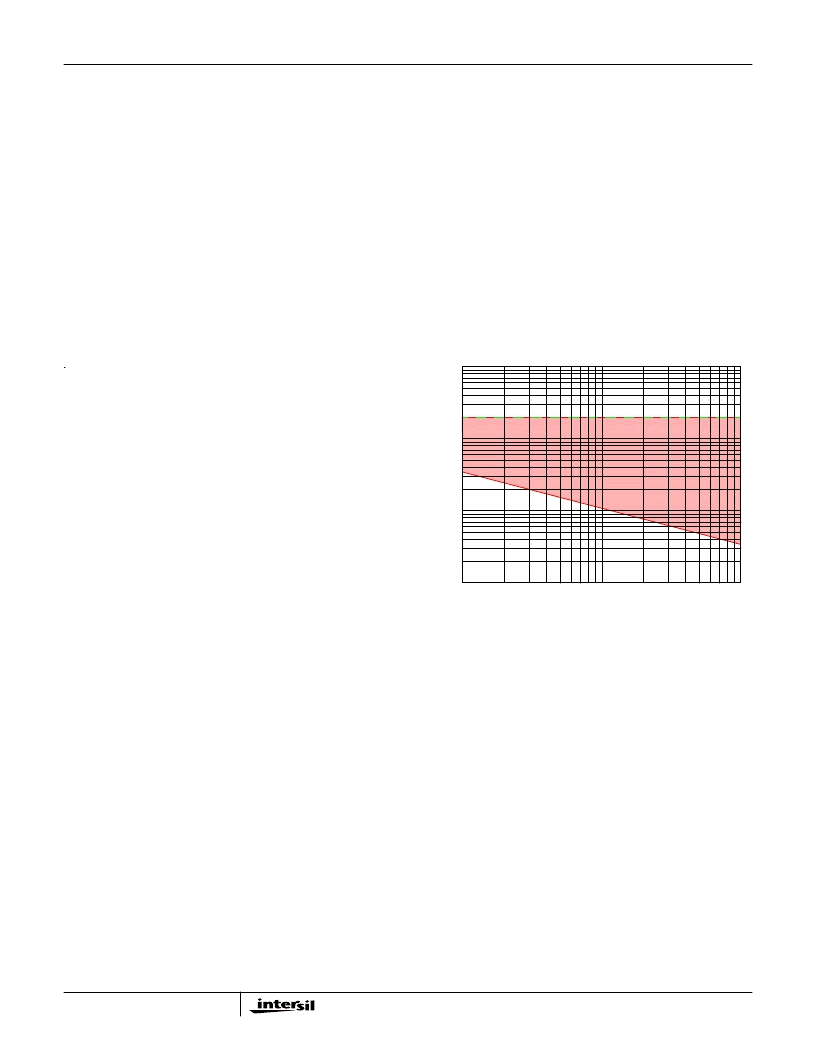

loop stability. Figure 13 outlines a capacitance vs. equivalent

series resistance envelope. For stable operation and

optimized performance, select a C

OUT4

capacitor or

combination of capacitors with characteristics within the

shown envelope.

Input Capacitors Selection

The input capacitors for an HIP6500B application have to

have a sufficiently low ESR as to not allow the input voltage

to dip excessively when energy is transferred to the output

capacitors. If the ATX supply does not meet the

specifications, certain imbalances between the ATX’s

outputs and the HIP6500B’s regulation levels could have as

a result a brisk transfer of energy from the input capacitors to

the supplied outputs. At the transition between active and

sleep states, this phenomena could result in the 5VSB

voltage dropping below the POR level (typically 4.1V) and

temporarily disabling the HIP6500B. The solution to a

potential problem such as this is using larger input

capacitors with a lower total combined ESR.

V

OUT

I

OUT

ESR

OUT

t

OUT

---------------

+

FIGURE 13. C

OUT4

OUTPUT CAPACITOR

E

)

1.0

0.1

10

0.01

CAPACITANCE (

μ

F)

10

100

1000

HIP6500B

相关PDF资料 |

PDF描述 |

|---|---|

| HIP6500 | Multiple Linear Power Controller with ACPI Control Interface |

| HIP6500CB | Multiple Linear Power Controller with ACPI Control Interface |

| HIP6500EVAL1 | Multiple Linear Power Controller with ACPI Control Interface |

| HIP6501 | Triple Linear Power Controller with ACPI Control Interface |

| HIP6501A | Triple Linear Power Controller with ACPI Control Interface(带ACPI控制接口的线性电源控制器) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HIP6500CB | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HIP6500CB-TS2490 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HIP6500EVAL1 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Multiple Linear Power Controller with ACPI Control Interface |

| HIP6501 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Triple Linear Power Controller with ACPI Control Interface |

| HIP6501A | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Triple Linear Power Controller with ACPI Control Interface |

发布紧急采购,3分钟左右您将得到回复。