参数资料

| 型号: | HIP6500BEVAL1 |

| 厂商: | Intersil |

| 文件页数: | 7/20页 |

| 文件大小: | 0K |

| 描述: | EVALUATION BOARD HIP6500 |

| 标准包装: | 1 |

| 类型: | ACPI 控制器 |

| 适用于相关产品: | HIP6500B |

| 所含物品: | 完全组装的评估板 |

�� �

�

�

�Application� Note� 9862�

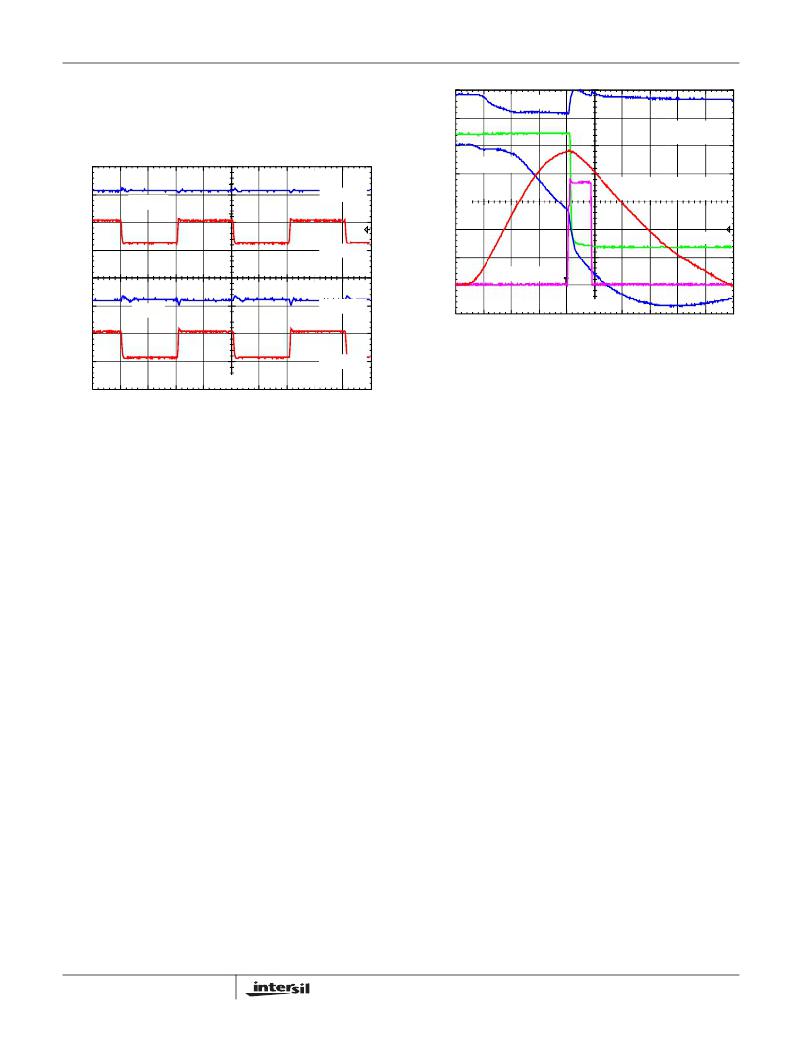

�In� Figure� 12,� the� outputs� shown� are� separately� subjected� to�

�load� transients� while� operating� in� sleep� state� (S3).� Transient�

�loading� of� the� outputs� is� as� follows:�

�-� 2.5V� MEM� :� 50mA� to� 200mA� at� 1A/� μ� s�

�-� 3.3V� SB� :� 30mA� to� 200mA� at� 0.1A/� μ� s�

�2.5V� MEM�

�3.3VIN�

�1� -� 5.00A/DIV�

�2� -� 1.00V/DIV�

�2.5V>�

�2.5V� MEM�

�100mV/DIV�

�2.5V� MEM�

�OUTPUT� CURRENT� 1�

�0A>�

�SS� (TP7)�

�200mA/DIV�

�GND>�

�FAULT� (TP4)� 2�

�3.3V>�

�3.3V� SB�

�100mV/DIV�

�T0�

�T1�

�T2�

�10� μ� s/DIV�

�T3�

�0A>�

�500� μ� s/DIV�

�200mA/DIV�

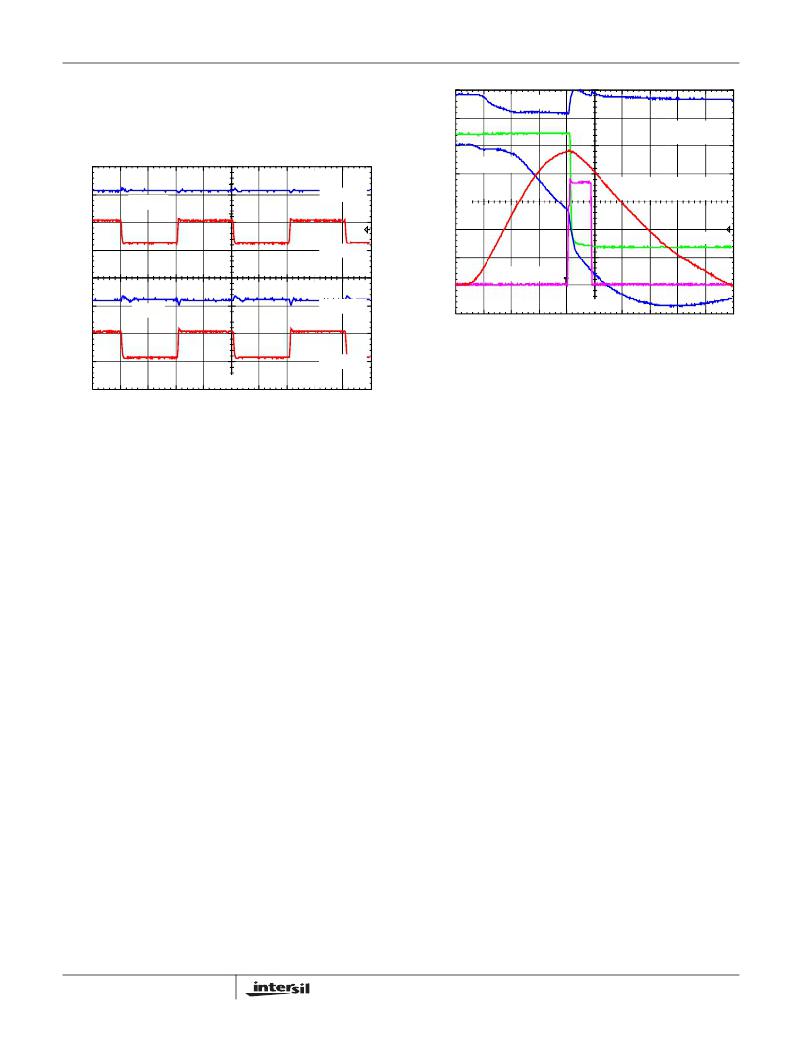

�FIGURE� 13.� HIP6500BEVAL1� 2.5V� MEM� OUTPUT�

�UNDERVOLTAGE� RESPONSE� WHILE� IN� ACTIVE�

�STATE� (S0,� S1)�

�FIGURE� 12.� HIP6500BEVAL1� SLEEP� STATE� (S3)� OUTPUT�

�TRANSIENT� RESPONSE�

�Output� Short-Circuit� Protection�

�Figure� 13� depicts� the� circuit’s� behavior� in� response� to� a�

�sudden� output� short-circuit� (output� under-voltage),� applied,�

�in� this� scope� capture,� on� the� 2.5V� MEM� output,� while�

�operating� in� active� state.� At� time� T0� a� short-circuit� is� applied�

�using� an� electronic� load� -� as� a� result,� the� 2.5V� output� starts�

�to� rapidly� discharge,� crossing� the� falling� under-voltage�

�threshold� at� time� T1.� To� avoid� false� triggers,� the� UV� detector�

�is� equipped� with� a� 10� μ� s� filter.� As� the� output� voltage� remains�

�below� the� undervoltage� (UV)� threshold� for� more� than� 10� μ� s,� it�

�triggers� a� fault� response� at� time� T2.� The� logic� high� output� on�

�the� FAULT� pin� sets� the� external� fault� latch� circuitry� which�

�shuts� down� the� ATX� supply� and� quickly� discharges� the� SS�

�capacitor� below� the� chip� shutdown� level,� reached� at� time� T3.�

�The� chip� reset� disables� the� fault� reporting� and� the� latch�

�maintains� the� circuit� in� a� reset� state.� The� latch� is� necessary�

�to� compensate� for� the� slow� response� of� the� ATX� supply,� by�

�shutting� down� the� controller� IC,� along� with� the� pass�

�elements.� Depressing� the� CLEAR� FAULT� button� resets� the�

�latch� and� releases� the� circuit� for� operation.�

�HIP6500B/02BEVAL1� Modifications�

�Setting� the� 2.5/3.3V� MEM� Output� to� 3.3V�

�(HIP6500BEVAL1� Only)�

�The� HIP6500BEVAL1� evaluation� board� ships� populated� to�

�demonstrate� support� for� RDRAM� or� some� double� data� rate�

�(DDR)� SDRAM� memory,� with� the� memory� output� set� for�

�2.5V.� The� HIP6500B,� however,� is� designed� for� either� 2.5V� or�

�3.3V� memory� output� voltage.� To� change� the� memory� output�

�voltage� on� the� evaluation� board� perform� the� following� steps:�

�?� Replace� R3� with� a� 15k� Ω� resistor�

�?� Remove� Q2,� and� install� an� N-MOS� transistor� in� its�

�place� (HUF76113� or� equivalent� recommended).� Please�

�note� the� connection� diagram� and� insure� the� correct�

�connections� are� established� (N-MOS� might� not� fit� the�

�provided� footprint)�

�With� the� above� modifications,� the� memory� output� will� be� set�

�to� 3.3V.� In� this� configuration,� the� output� voltage� obtainable� in�

�active� state� is� directly� related� to� the� ATX� 3.3V� output,� the�

�memory� output� current,� and� the� r� (DS)ON� of� Q2,� according� to�

�the� following� equation:�

�V� MEM� =� V� IN� –� I� MEM� ×� r� (� DS� )� ON�

�Improving� Output� Voltage� Tolerance�

�The� key� to� improving� the� output� voltage� tolerance� is�

�identifying� the� parameters� which� affect� it,� and� then� taking�

�steps� toward� improving� them.�

�The� output� DC� voltage� droop� on� the� 3.3V� DUAL� and� 5V� DUAL�

�outputs� under� applied� load� is� due� to� the� resistive� losses�

�across� the� N-MOS� switch’s� own� r� DS(ON)� -� decreasing� the�

�r� DS(ON)� results� in� reduced� load-dependent� voltage� drooping.�

�7�

�相关PDF资料 |

PDF描述 |

|---|---|

| HIP6501AEVAL1 | EVALUATION BOARD ACPI HIP6501 |

| HIP9011EVAL1Z | BOARD EVALUATION FOR HIP9011 |

| HM2H08P115LF | HM2H08P115LF SHROUD STYLE B LF |

| HM2P12P1LF | HM2 M INS STYLE N WIDE |

| HM2R06P1LF | MILLIPACS RCP HSG |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HIP6500CB | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HIP6500CB-TS2490 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HIP6500EVAL1 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Multiple Linear Power Controller with ACPI Control Interface |

| HIP6501 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Triple Linear Power Controller with ACPI Control Interface |

| HIP6501A | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Triple Linear Power Controller with ACPI Control Interface |

发布紧急采购,3分钟左右您将得到回复。