- 您现在的位置:买卖IC网 > PDF目录17024 > HW-V5-ML561-UNI-G-J (Xilinx Inc)EVALUATION PLATFORM VIRTEX-5 PDF资料下载

参数资料

| 型号: | HW-V5-ML561-UNI-G-J |

| 厂商: | Xilinx Inc |

| 文件页数: | 10/91页 |

| 文件大小: | 0K |

| 描述: | EVALUATION PLATFORM VIRTEX-5 |

| 产品变化通告: | Development Systems Discontinuation 16/Jan/2012 |

| 标准包装: | 1 |

| 系列: | Virtex®-5 LXT |

| 类型: | FPGA |

| 适用于相关产品: | XC5VLX50T-FFG1136 |

| 所含物品: | 评估平台,线缆,CD,小型闪存卡,DDR2 DIMM,- 不包括电源 - |

第1页第2页第3页第4页第5页第6页第7页第8页第9页当前第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页

Virtex-5 FPGA Data Sheet: DC and Switching Characteristics

DS202 (v5.3) May 5, 2010

Product Specification

18

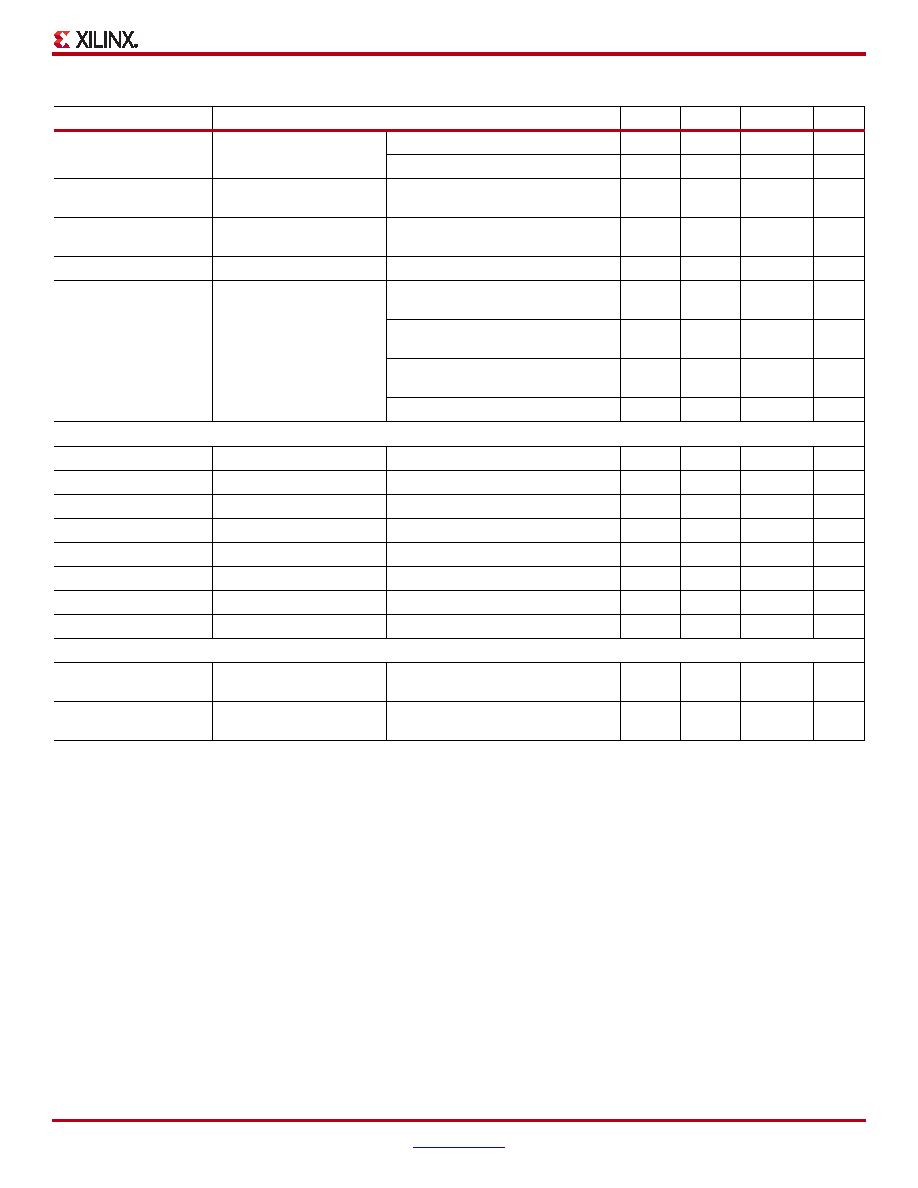

Table 35: GTP_DUAL Tile Receiver Switching Characteristics

Symbol

Description

Min

Typ

Max

Units

FGTPRX

Serial data rate

RX oversampler not enabled

0.5

FGTPMAX

Gb/s

RX oversampler enabled

0.1

0.5

Gb/s

RXOOBVDPP

OOB detect threshold

peak-to-peak

OOBDETECT_THRESHOLD = 100

60

105

165

mV

RXSST

Receiver spread-spectrum

tracking(1)

Modulated @ 33 KHz

–5000

0

ppm

RXRL

Run length (CID)

Internal AC capacitor bypassed

150

UI

RXPPMTOL

Data/REFCLK PPM offset

tolerance(2)

CDR 2nd-order loop disabled with

PLL_RXDIVSEL_OUT = 1(3)

–200

200

ppm

CDR 2nd-order loop disabled with

PLL_RXDIVSEL_OUT = 2(3)

–200

200

ppm

CDR 2nd-order loop disabled with

PLL_RXDIVSEL_OUT = 4(3)

–100

100

ppm

CDR 2nd-order loop enabled

–1000

1000

ppm

SJ Jitter Tolerance(4)

JT_SJ3.75

Sinusoidal Jitter(5)

3.75 Gb/s

0.30

UI

JT_SJ3.2

Sinusoidal Jitter(5)

3.20 Gb/s

0.40

UI

JT_SJ2.50

Sinusoidal Jitter(5)

2.50 Gb/s

0.40

UI

JT_SJ2.00

Sinusoidal Jitter(5)

2.00 Gb/s

0.40

UI

JT_SJ1.00

Sinusoidal Jitter(5)

1.00 Gb/s

0.30

UI

JT_SJ500

Sinusoidal Jitter(5)

500 Mb/s

0.30

UI

JT_SJ500

Sinusoidal Jitter(5)

500 Mb/s OS

0.30

UI

JT_SJ100

Sinusoidal Jitter(5)

100 Mb/s OS

0.30

UI

SJ Jitter Tolerance with Stressed Eye(4)

JT_TJSE3.2

Total Jitter with Stressed

Eye(6)

3.20 Gb/s

0.87

UI

JT_SJSE3.2

Sinusoidal Jitter with

Stressed Eye(6)

3.20 Gb/s

0.30

UI

Notes:

1.

Using PLL_RXDIVSEL_OUT = 1 only.

2.

Indicates the maximum offset between the receiver reference clock and the serial data. For example, a reference clock with ±100 ppm

resolution results in a maximum offset of 200 ppm between the reference clock and the serial data.

3.

CDR 1st-order step size set to 2.

4.

All jitter values are based on a Bit Error Ratio of 1e–12.

5.

Using 80 MHz sinusoidal jitter only in the absence of deterministic and random jitter.

6.

Stimulus signal includes 0.4UI of DJ and 0.17UI of RJ. RX equalizer is enabled.

相关PDF资料 |

PDF描述 |

|---|---|

| HW-V5-ML550-UNI-G-J | EVALUATION PLATFORM VIRTEX-5 |

| HW-V5-ML525-UNI-G-J | EVAL PLATFORM ROCKET IO VIRTEX-5 |

| STD21W-F | WIRE & CABLE MARKERS |

| XE8000EV120 | BOARD EVAL FOR SX8722I070TRLF |

| AD923011-200EBZ | BOARD EVAL FOR AD9230 200MSPS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HW-V5-PCIE2-UNI-G | 功能描述:KIT DEV PCIEXPRESS GTX VIRTEX5 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Virtex® -5 产品培训模块:Blackfin® Processor Core Architecture Overview Blackfin® Device Drivers Blackfin® Optimizations for Performance and Power Consumption Blackfin® System Services 特色产品:Blackfin? BF50x Series Processors 标准包装:1 系列:Blackfin® 类型:DSP 适用于相关产品:ADSP-BF548 所含物品:板,软件,4x4 键盘,光学拨轮,QVGA 触摸屏 LCD 和 40G 硬盘 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相关产品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA |

| HW-VID-KIT | 功能描述:可编程逻辑 IC 开发工具 Lattice Video Interface Kit RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压: |

| HW-VL1 | 制造商:IDEC CORPORATION 功能描述:BARRIER |

| HW-VL2 | 制造商:IDEC Corporation 功能描述:COVER;HW FNGR SAFE CONTAC CVR 制造商:IDEC CORPORATION 功能描述:HW FNGR SAFE CONTAC CVR |

| HW-VL3 | 制造商:IDEC Corporation 功能描述: 制造商:IDEC Corporation 功能描述:Replacs TW-VL3 FNGR SAF |

发布紧急采购,3分钟左右您将得到回复。