- 您现在的位置:买卖IC网 > PDF目录67682 > IBM25NPE405L-3DA200CZ 32-BIT, 200 MHz, RISC PROCESSOR, PBGA324 PDF资料下载

参数资料

| 型号: | IBM25NPE405L-3DA200CZ |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 200 MHz, RISC PROCESSOR, PBGA324 |

| 封装: | 23 MM, PLASTIC, EBGA-324 |

| 文件页数: | 20/48页 |

| 文件大小: | 741K |

| 代理商: | IBM25NPE405L-3DA200CZ |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页当前第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

Advance Information

PowerNPTM NPe405L Embedded Processor Data Sheet

27

Signal List

The table following table provides a summary of the number of package pins associated with each functional

interface group.

In the table “Signal Functional Description” on page 28, each external signal is listed along with a short

description of the signal function. The signals are grouped together according to their function. Some signals

are multiplexed on the same package pin (ball) so that the pin can be used for different functions. In most

cases, the signal name is shown in this table without any multiplexed signal names that may be associated

with it. In cases where multiplexed signals are in the same functional group, the names appear as a default

signal followed by secondary signals in square brackets (for example, PCIC0:3[BE0:3]). Active-low signals

such as BE0:3 are marked with an overline. Any signal that is not the primary (default) signal on a multiplexed

pin is shown in square backets.

The active signal on a multiplexed pin is controlled by programming. It is expected that in any single

application, a particular pin will always be programmed to serve the same function. The flexibility of

multiplexing allows a single chip to offer a richer pin selection than would otherwise be possible.

In addition to multiplexing, many pins are also multi-purpose. For example, EMC0TxErr[EMC0Tx1En]

functions as an error output when the Ethernet interface operates in MII mode, or as a transmit enable output

when operating in RMII mode.

One group of pins is used as strapped inputs during system reset. These pins function as strapped inputs

only during reset and are used for other functions during normal operation (see “Initialization” on page 47).

Note that these are not multiplexed pins since the function of the pins is not programmable.

The following table lists all of the I/O signals provided by the NPe405L. Please refer to “Signals Listed

Alphabetically” on page 13 for the pin number to which each signal is assigned.

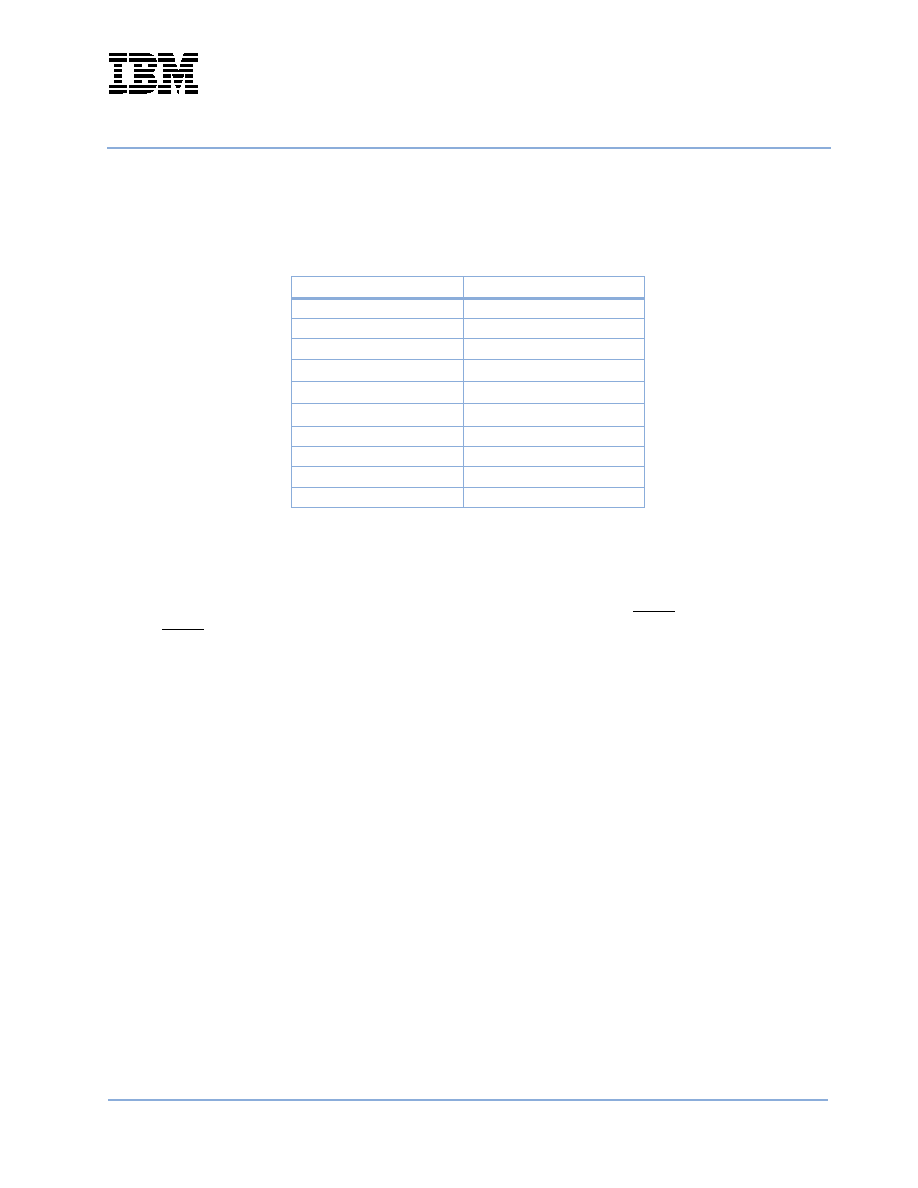

Pin Summary

Group

No. of Pins

Nonmultiplexed Signals

167

Multiplexed Signals

48

Total Signal Pins

215

AVDD

1

OVDD

16

VDD

8

Gnd

48

Thermal (and Gnd)

36

Reserved

0

Total Pins

324

相关PDF资料 |

PDF描述 |

|---|---|

| IBM25NPE405L-3FA200CZ | 32-BIT, 200 MHz, RISC PROCESSOR, PBGA324 |

| IBM25NPE405L-3FA266CZ | 32-BIT, 266 MHz, RISC PROCESSOR, PBGA324 |

| IBM25PPC405EP-3GB133CZ | 32-BIT, 133.33 MHz, RISC PROCESSOR, PBGA385 |

| IBM25PPC405EP-3GB133C | 32-BIT, 133.33 MHz, RISC PROCESSOR, PBGA385 |

| IBM25PPC405GP-3DD200C | RISC PROCESSOR, PBGA456 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IBM25NPE405L-3FA133C | 制造商:AMCC 制造商全称:Applied Micro Circuits Corporation 功能描述:PowerNP |

| IBM25NPE405L-3FA133CZ | 制造商:AMCC 制造商全称:Applied Micro Circuits Corporation 功能描述:PowerNP |

| IBM25NPE405L-3FA200C | 制造商:AMCC 制造商全称:Applied Micro Circuits Corporation 功能描述:PowerNP |

| IBM25NPE405L-3FA200CZ | 制造商:AMCC 制造商全称:Applied Micro Circuits Corporation 功能描述:PowerNP |

| IBM25NPE405L-3FA266C | 制造商:AMCC 制造商全称:Applied Micro Circuits Corporation 功能描述:PowerNP |

发布紧急采购,3分钟左右您将得到回复。