- 您现在的位置:买卖IC网 > PDF目录67682 > IBM25NPE405L-3DA200CZ 32-BIT, 200 MHz, RISC PROCESSOR, PBGA324 PDF资料下载

参数资料

| 型号: | IBM25NPE405L-3DA200CZ |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 200 MHz, RISC PROCESSOR, PBGA324 |

| 封装: | 23 MM, PLASTIC, EBGA-324 |

| 文件页数: | 38/48页 |

| 文件大小: | 741K |

| 代理商: | IBM25NPE405L-3DA200CZ |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页当前第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

Advance Information

PowerNPTM NPe405L Embedded Processor Data Sheet

43

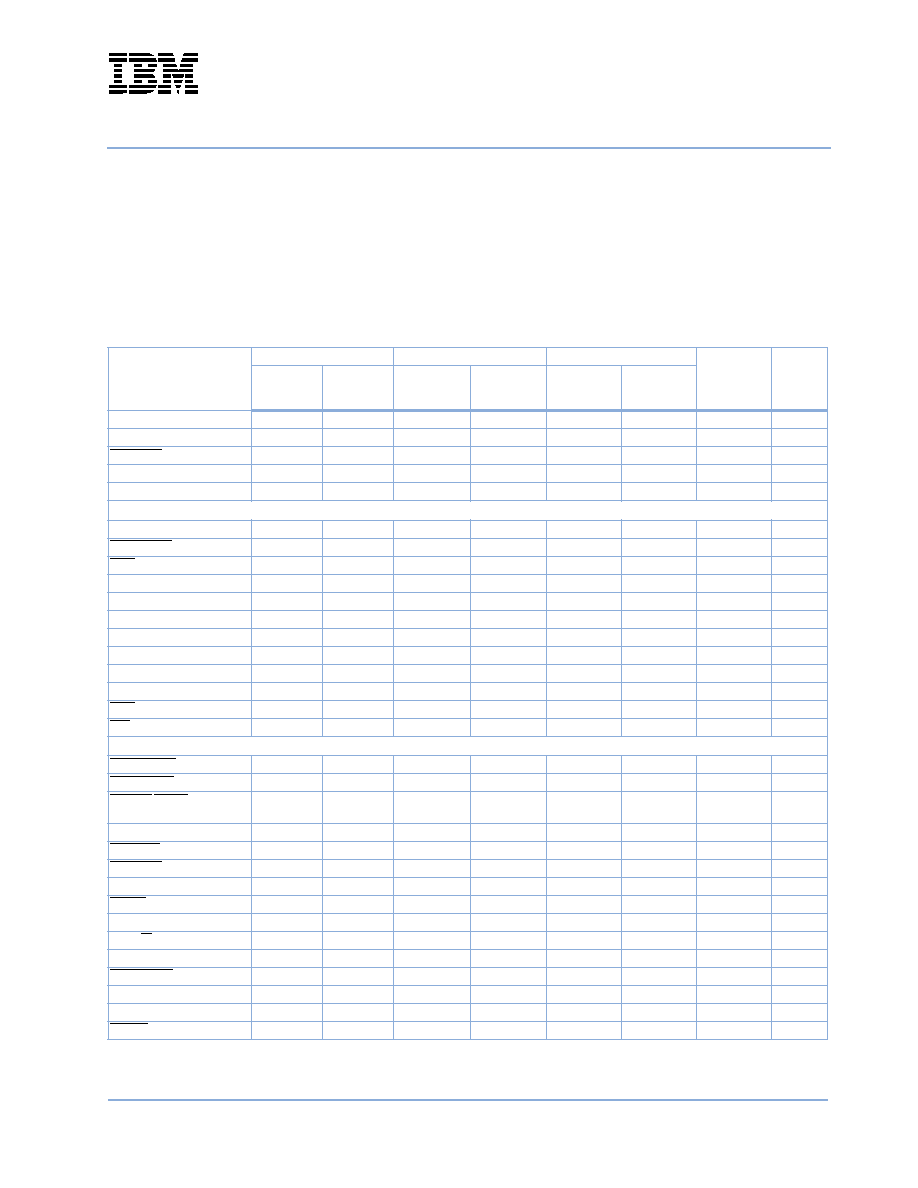

SysClk

n/a

SysErr

n/a

5.3

1.7

12

8

SysReset

n/a

12

8

TestEn

dc

n/a

TmrClk

n/a

async

n/a

SDRAM Interface

BA1:0

n/a

7.2

1.5

19

12

SysClk

2, 3

BankSel3:0

n/a

5.8

1.0

19

12

SysClk

3

CAS

n/a

7.0

1.4

19

12

SysClk

2, 3

ClkEn0:1

n/a

4.9

1.0

40

25

SysClk

3

DQM3:0

n/a

5.9

1.0

19

12

SysClk

3

DQMCB

n/a

5.9

1.0

19

12

SysClk

3

ECC7:0

2.0

0.3

5.7

1.0

19

12

SysClk

3

MemAddr12:0

n/a

7.2

1.4

19

12

SysClk

2, 3

MemClkOut0:1

n/a

0.4

-1.2

19

12

SysClk

3, 4

MemData31:0

2.0

0.3

5.6

1.0

19

12

SysClk

3

RAS

n/a

7.4

1.6

19

12

SysClk

2, 3

WE

n/a

7.1

1.4

19

12

SysClk

2, 3

External Slave Peripheral Interface

DMAReq0:3[GPIO9:12]

4.8

0.0

7.0

1.1

n/a

PerClk

DMAAck0:3[GPIO13:16]

n/a

7.5

1.1

12

8

PerClk

EOT0:3[TC0:3]

[GPIO24:27]

4.3

-0.1

8.5

1.2

12

8

PerClk

PerAddr4:31

n/a

8.5

0.9

17

11

PerClk

PerBLast

n/a

7.4

1.4

12

8

PerClk

PerCS0:3

n/a

7.2

1.3

12

8

PerClk

PerData0:15

4.8

1.0

9.3

1.0

17

11

PerClk

PerOE

n/a

7.6

1.4

12

8

PerClk

PerPar0:1

3.1

0.0

8.3

0.9

17

11

PerClk

PerR/W

n/a

7.5

1.4

12

8

PerClk

PerReady

7.5

-0.5

n/a

PerClk

PerWBE0:1

n/a

7.5

1.3

12

8

PerClk

n/a

0.5

-0.9

17

11

PLB Clk

5

PerErr

4.0

-0.6

n/a

PerClk

PerWE[GPIO31]

n/a

8.3

1.3

12

8

I/O Specications—200MHz (Part 3 of 3)

Notes:

1. Ethernet interface meets timing requirements as defined by IEEE 802.3 standard.

2. The two-cycle SDRAM command interface is driven in cycle 1 and used in cycle 2. Output times in table are in cycle 1.

3. SDRAM output timing is relative to the rising edge of the internal PLB clock, which is an integral multiple of and rising-

edge aligned with SysClk. Therefore, SDRAM output timings in the table are shown relative to SysClk. Timings shown

are for a lumped 50pF load, however the interface has been verified for PC100-compliant operation using transmission

line circuit analysis.

4. SDRAM MemClkOut0:1 rising edge at package pin precedes the internal PLB clock by approximately 0.5ns for a

typical clock network or a lumped 10pF load.

5. PerClk rising edge at package pin with a 10pF load trails the internal PLB clock by approximately 0.8ns.

Signal

Input (ns)

Output (ns)

Output Current (mA)

Clock

Notes

Setup Time

(minimum)

Hold Time

(minimum)

Valid Delay

(maximum)

50pF load

Hold Time

(minimum)

50pF load

I/O H

(maximum)

I/O L

(minimum)

相关PDF资料 |

PDF描述 |

|---|---|

| IBM25NPE405L-3FA200CZ | 32-BIT, 200 MHz, RISC PROCESSOR, PBGA324 |

| IBM25NPE405L-3FA266CZ | 32-BIT, 266 MHz, RISC PROCESSOR, PBGA324 |

| IBM25PPC405EP-3GB133CZ | 32-BIT, 133.33 MHz, RISC PROCESSOR, PBGA385 |

| IBM25PPC405EP-3GB133C | 32-BIT, 133.33 MHz, RISC PROCESSOR, PBGA385 |

| IBM25PPC405GP-3DD200C | RISC PROCESSOR, PBGA456 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IBM25NPE405L-3FA133C | 制造商:AMCC 制造商全称:Applied Micro Circuits Corporation 功能描述:PowerNP |

| IBM25NPE405L-3FA133CZ | 制造商:AMCC 制造商全称:Applied Micro Circuits Corporation 功能描述:PowerNP |

| IBM25NPE405L-3FA200C | 制造商:AMCC 制造商全称:Applied Micro Circuits Corporation 功能描述:PowerNP |

| IBM25NPE405L-3FA200CZ | 制造商:AMCC 制造商全称:Applied Micro Circuits Corporation 功能描述:PowerNP |

| IBM25NPE405L-3FA266C | 制造商:AMCC 制造商全称:Applied Micro Circuits Corporation 功能描述:PowerNP |

发布紧急采购,3分钟左右您将得到回复。