- 您现在的位置:买卖IC网 > PDF目录2070 > ICS1574BMT (IDT, Integrated Device Technology Inc)IC CLOCK GEN PROGR LASER 16-SOIC PDF资料下载

参数资料

| 型号: | ICS1574BMT |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 11/12页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK GEN PROGR LASER 16-SOIC |

| 产品变化通告: | Product Discontinuation 13/May/2009 |

| 标准包装: | 2,500 |

| 类型: | 时钟/频率合成器,时钟发生器 |

| PLL: | 是 |

| 输入: | 时钟,晶体 |

| 输出: | CMOS |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:1 |

| 差分 - 输入:输出: | 无/无 |

| 频率 - 最大: | 400MHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 4.75 V ~ 5.25 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-SOIC(0.154",3.90mm 宽) |

| 供应商设备封装: | 16-SOIC |

| 包装: | 带卷 (TR) |

| 其它名称: | 1574BMT |

ICS1574B

8

]

1

[

P]

0

[

PN

I

A

G

)

n

a

i

d

a

r

/

A

(

00

5

0

.

0

01

5

1

.

0

10

5

.

0

11

5

.

1

]

2

[

V]

1

[

V]

0

[

V

N

I

A

G

O

C

V

)

t

l

o

V

/

z

H

M

(

10

0

3

10

1

5

4

11

0

6

111

0

8

BIT(S)

BIT REF.

DESCRIPTION

15

Reserved

Must be set to 0.

16

AUX_PCLK

Must be set to 0 except when in the AUX-EN test mode.

When in the AUX-EN test mode, this bit controls the

PCLK output.

17 – 24

Reserved

Must be set to 0.

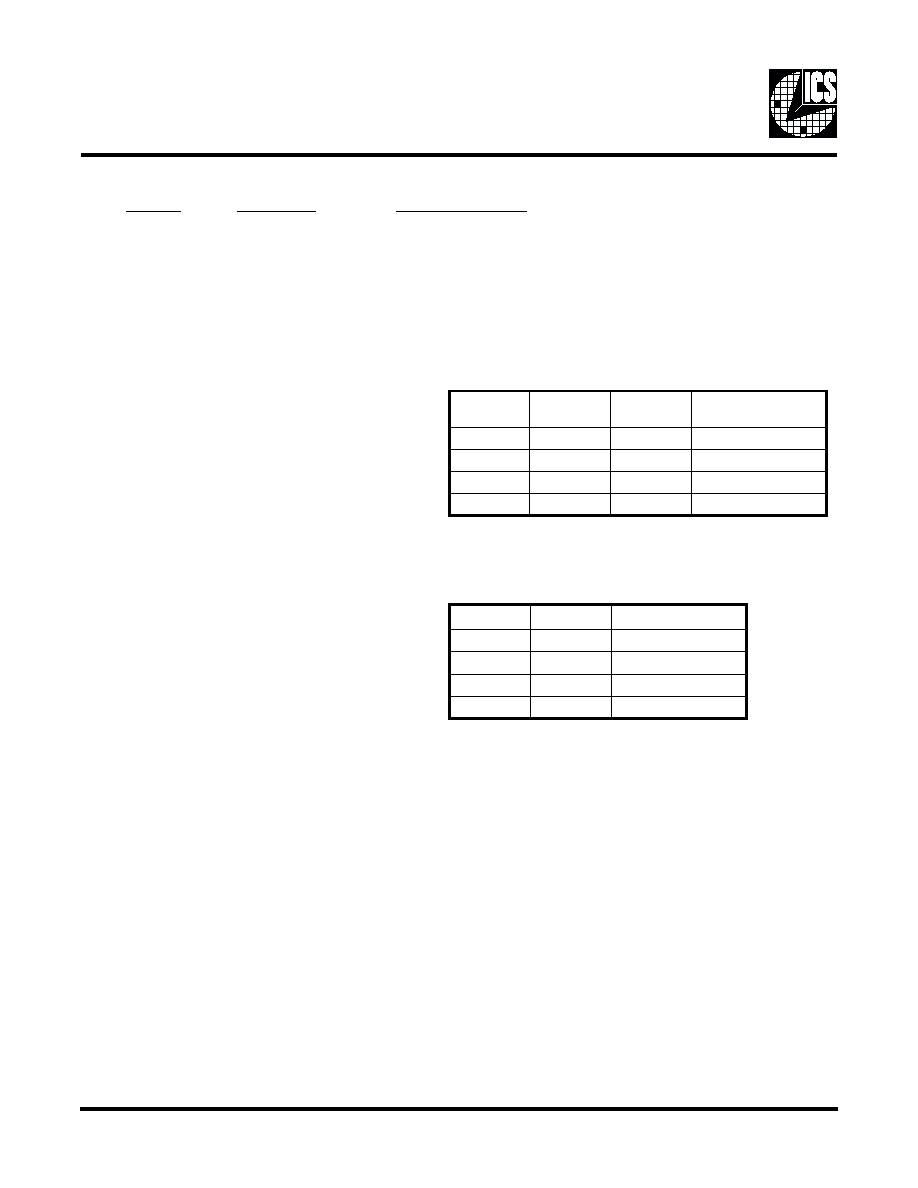

25 – 27

V[0]..V[2]

Sets the gain of VCO

28

Reserved

Must be set to 1.

29 – 30

P[0]..P[1]

Sets the gain of the phase detector according to this table:

31

Reserved

Must be set to 0.

32

P[2]

Phase detector tuning bit. Should normally be set to one.

See text.

33 – 38

M[0]..M[5]

M counter control bits. Modulus = value + 1.

39

PCLKEN_POL

When = 0, PCLK output enabled when PCLKEN input is

low. When = 1, PCLK output enabled when PCLKEN input

is high.

40

DBLFREQ

Doubles modulus of dual-modulus prescaler (from 6 / 7 to

12 /14).

41 – 44

A[0]..A[3]

Controls A counter. When set to zero, modulus = 7.

Otherwise, modulus = 7 for "value" underflows of the

prescaler, and modulus = 6 thereafter until M counter

underflows.

相关PDF资料 |

PDF描述 |

|---|---|

| ICS180M-01LF | IC CLOCK GEN LOW EMI 8-SOIC |

| ICS181M-02LF | IC CLOCK GEN LOW EMI 8-SOIC |

| ICS181M-03LF | IC CLOCK GEN LOW EMI 8-SOIC |

| ICS181M-51LF | IC CLOCK GEN LOW EMI 8-SOIC |

| ICS181M-52LF | IC CLOCK GEN LOW EMI 8-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS1577N | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog IC |

| ICS-16 | 制造商:MAXCONN 功能描述: |

| ICS162834 | 制造商:ICS 制造商全称:ICS 功能描述:18-Bit 3.3V Registered Buffer |

| ICS162834AG-T | 制造商:ICS 制造商全称:ICS 功能描述:18-Bit 3.3V Registered Buffer |

| ICS162835 | 制造商:ICS 制造商全称:ICS 功能描述:18-Bit 3.3V Registered Buffer |

发布紧急采购,3分钟左右您将得到回复。