- 您现在的位置:买卖IC网 > PDF目录2070 > ICS1574BMT (IDT, Integrated Device Technology Inc)IC CLOCK GEN PROGR LASER 16-SOIC PDF资料下载

参数资料

| 型号: | ICS1574BMT |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 7/12页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK GEN PROGR LASER 16-SOIC |

| 产品变化通告: | Product Discontinuation 13/May/2009 |

| 标准包装: | 2,500 |

| 类型: | 时钟/频率合成器,时钟发生器 |

| PLL: | 是 |

| 输入: | 时钟,晶体 |

| 输出: | CMOS |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:1 |

| 差分 - 输入:输出: | 无/无 |

| 频率 - 最大: | 400MHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 4.75 V ~ 5.25 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-SOIC(0.154",3.90mm 宽) |

| 供应商设备封装: | 16-SOIC |

| 包装: | 带卷 (TR) |

| 其它名称: | 1574BMT |

ICS1574B

4

PLL Post-Scaler

A programmable post-scaler may be inserted between the

VCO and the PCLK divider of the ICS1574B. This is useful in

generating lower frequencies, as the VCO has been optimized

for high-frequency operation. The post-scaler is not affected

by the PCLKEN input.

The post-scaler allows the selection of:

VCO frequency

VCO frequency divided by 2

VCO frequency divided by 4

AUX-EN Test Mode

PLL Synthesizer Description —

Ratiometric Mode

The ICS1574B generates its output frequencies using phase-

locked loop techniques. The phase-locked loop (or PLL) is a

closed-loop feedback system that drives the output frequency

to be ratiometrically related to the reference frequency pro-

vided to the PLL (see Figure 1). The reference frequency is

generated by an on-chip crystal oscillator or the reference fre-

quency may be applied to the ICS1574B from an external

frequency source.

The phase-frequency detector shown in the block diagram

drives the voltage-controlled oscillator, or VCO, to a fre-

quency that will cause the two inputs to the phase-frequency

detector to be matched in frequency and phase. This occurs

when:

back divider makes use of a dual-modulus prescaler tech-

nique that allows the programmable counters to operate at

low speed without sacrificing resolution. This is an improve-

ment over conventional fixed prescaler architectures that

typically impose a factor-of-four (or larger) penalty in this re-

spect.

Table 1 permits the derivation of “A” & “M” converter pro-

gramming directly from desired modulus.

Digital Inputs

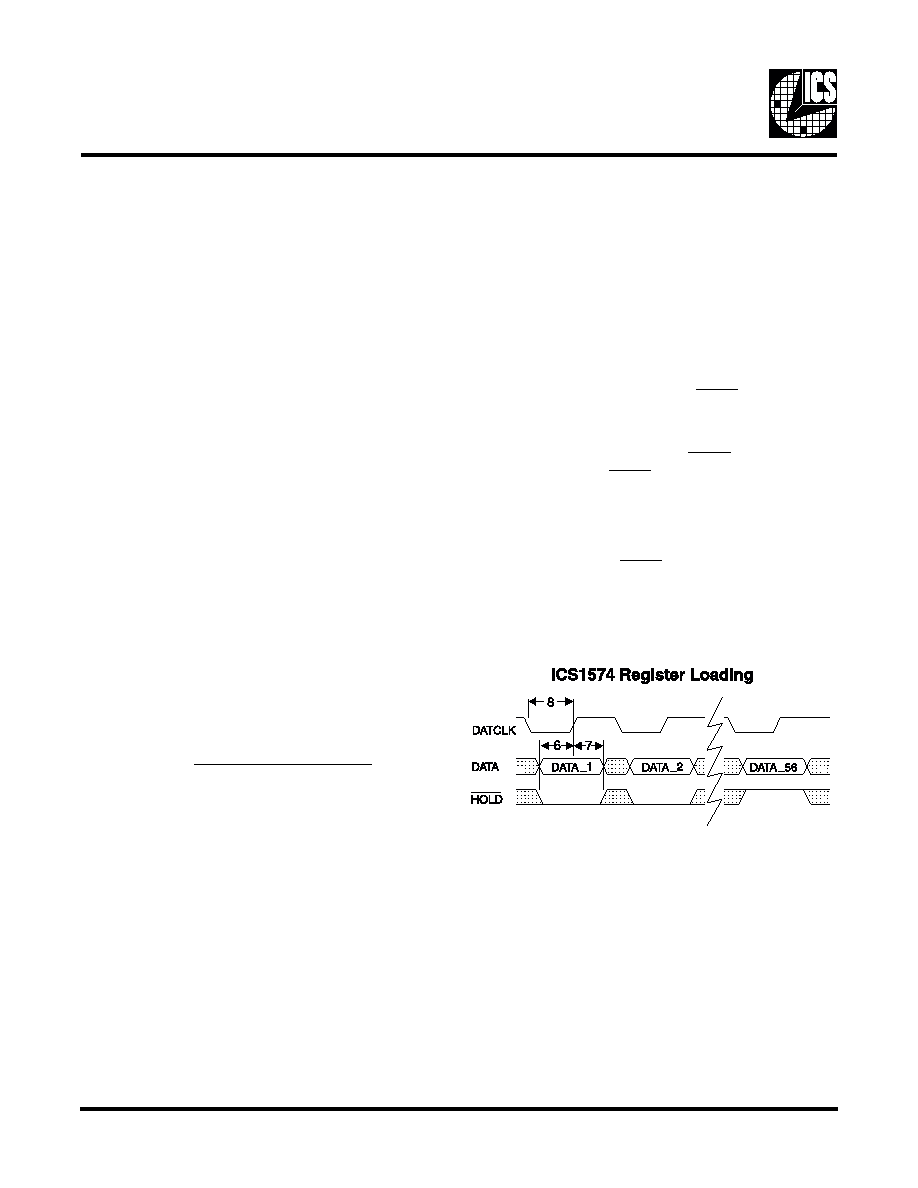

The programming of the ICS1574B is performed serially

by using the DATCLK, DATA, and HOLD pins to load an

internal shift register.

DATA is shifted into the register on the rising edge of

DATCLK. The logic value on the HOLD pin is latched at

the same time. When HOLD is low, the shift register may

be loaded without disturbing the operation of the

ICS1574B. When high, the shift register outputs are trans-

ferred to the control registers, and the new programming

information becomes active. Ordinarily, a high level

should be placed on the HOLD pin when the last data bit is

presented. See Figure 3 for the programming sequence.

The PCLKEN input polarity may be programmed under

register control via Bit 39.

F(VCO): =

F(XTAL1) Feedback Divider

Reference Divider

Figure 3

This expression is exact; that is, the accuracy of the output

frequency depends solely on the reference frequency pro-

vided to the part (assuming correctly programmed dividers).

The VCO gain is programmable, permitting the ICS1574B to

be optimized for best performance at all operating frequen-

cies.

The reference divider may be programmed for any modulus

from 1 to 128 in steps of one.

The feedback divider may be programmed for any modulus

from 37 through 392 in steps of one. Any even modulus from

392 through 784 can also be achieved by setting the “double”

bit which doubles the feedback divider modulus. The feed-

Output Description

The PCLK output is a high-current CMOS type drive

whose frequency is controlled by a programmable divider

that may be selected for a modulus of 3, 4, 5, 6, 8, 10, 12,

16 or 20. It may also be suppressed under register control

via Bit 46.

相关PDF资料 |

PDF描述 |

|---|---|

| ICS180M-01LF | IC CLOCK GEN LOW EMI 8-SOIC |

| ICS181M-02LF | IC CLOCK GEN LOW EMI 8-SOIC |

| ICS181M-03LF | IC CLOCK GEN LOW EMI 8-SOIC |

| ICS181M-51LF | IC CLOCK GEN LOW EMI 8-SOIC |

| ICS181M-52LF | IC CLOCK GEN LOW EMI 8-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS1577N | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog IC |

| ICS-16 | 制造商:MAXCONN 功能描述: |

| ICS162834 | 制造商:ICS 制造商全称:ICS 功能描述:18-Bit 3.3V Registered Buffer |

| ICS162834AG-T | 制造商:ICS 制造商全称:ICS 功能描述:18-Bit 3.3V Registered Buffer |

| ICS162835 | 制造商:ICS 制造商全称:ICS 功能描述:18-Bit 3.3V Registered Buffer |

发布紧急采购,3分钟左右您将得到回复。