- 您现在的位置:买卖IC网 > PDF目录9982 > ICS1894K-32LF (IDT, Integrated Device Technology Inc)PHYCEIVER LOW PWR 3.3V 32QFN PDF资料下载

参数资料

| 型号: | ICS1894K-32LF |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 23/50页 |

| 文件大小: | 0K |

| 描述: | PHYCEIVER LOW PWR 3.3V 32QFN |

| 标准包装: | 490 |

| 类型: | PHY 收发器 |

| 规程: | MII,RMII |

| 电源电压: | 3.14 V ~ 3.47 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-VFQFN 裸露焊盘 |

| 供应商设备封装: | 32-QFN 裸露焊盘(5x5) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页当前第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页

ICS1894-32

10BASE-T/100BASE-TX INTEGRATED PHYCEIVER WITH RMII INTERFACE

PHYCEIVER

IDT 10BASE-T/100BASE-TX INTEGRATED PHYCEIVER WITH RMII INTERFACE

3

ICS1894-32

REV M 021512

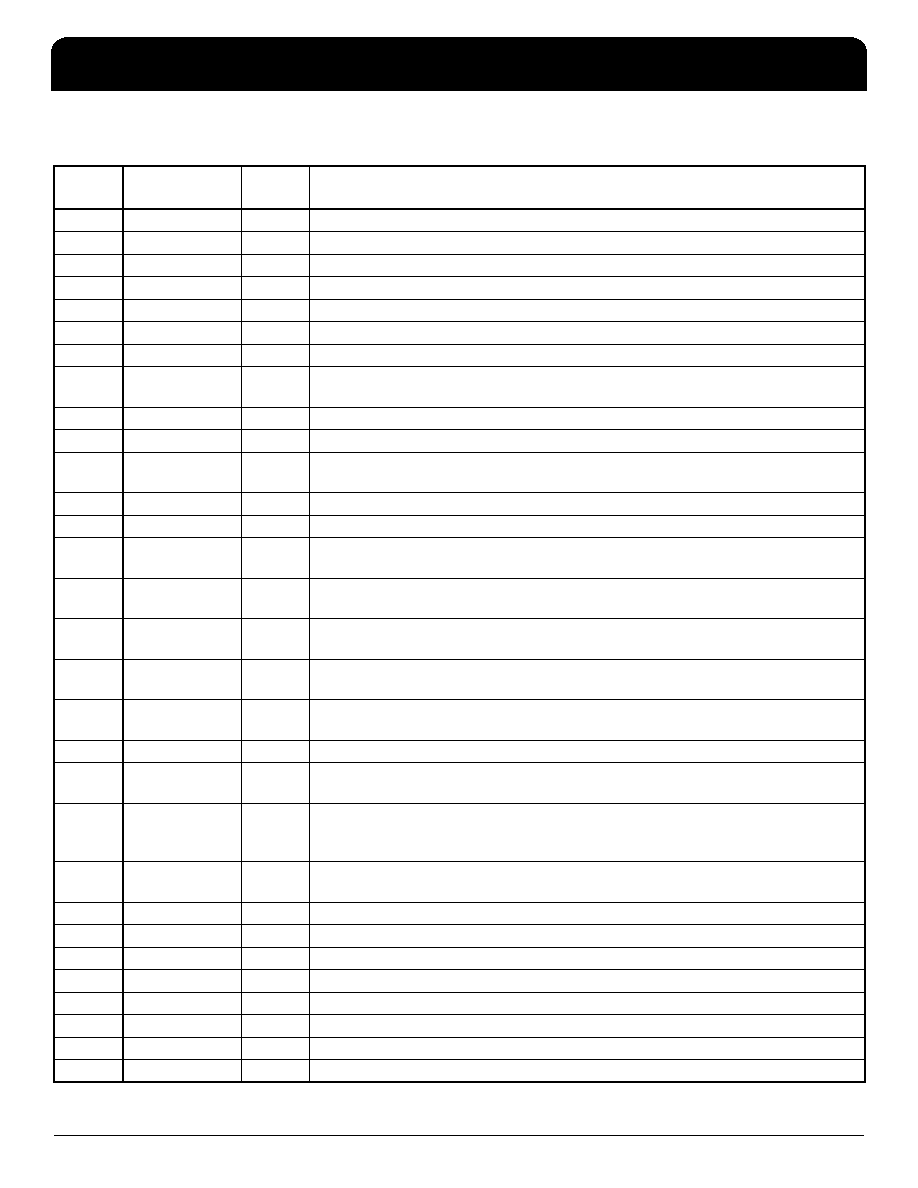

Pin Descriptions

Pin

Number

Pin

Name

Pin

Type1

Pin Description

1

TP_AP

AIO

Twisted pair port A (for either transmit or receive) positive signal

2

TP_AN

AIO

Twisted pair port A (for either transmit or receive) negative signal

3

VSS

Ground Connect to ground.

4

VDD

Power

3.3V Power Supply

5

TP_BN

AIO

Twisted pair port B (for either transmit or receive) negative signal

6

TP_BP

AIO

Twisted pair port B (for either transmit or receive) positive signal

7

VDD

Power

3.3V Power Supply

8

TCSR

AIO

Transmit Current bias pin, connected to Vdd and ground via resistors (see

“Recommended Component Values” table and the “ICS1894-32 TCSR” figure).

9

VSS

Ground Connect to ground.

10

RESET_N

Input

Hardware reset for the entire chip (active low)

11

P2/INT

IO/Ipd

PHY address Bit 2 as input (during power on reset/hardware reset)

Interrupt output as output (default active low, can be programmed to active high)

12

MDIO

IO

Management Data Input/Output

13

MDC

Input

Management Data Clock

14

AMDIX/RXD3

IO/Ipu

AMDIX enable as input (during power on reset/hardware reset)

Receive data Bit 3 in MII mode as output.

15

P3/RXD2

IO/Ipd

PHY address Bit 3 as input (during power on reset/hardware reset)

Receive data Bit 2 in MII mode as output.

16

RXTRI/

RXD1

IO/Ipd

RX tri-state enable as input (during power on reset/hardware reset)

Receive data Bit 1 in both RMII and MII mode as output.

17

FDPX/

RXD0

IO/Ipu

Full duplex enable as input (during power on reset/hardware reset)

Receive data Bit 0 in both RMII and MII mode as output

18

RMII/RXDV

IO/Ipd

RMII/MII select as input (during power on reset/hardware reset)

Receive data valid in MII mode and CRS_DV in RMII mode as output.

19

VDDIO

Power

3.3 V/1.8 V IO Power Supply.

20

ANSEL/

RXCLK

IO/Ipu

Auto-negotiation enable as input (during power on reset/hardware reset)

Receive clock in MII mode as output.

21

NOD/

RXER

IO/Ipd

Node select as input (during power on reset/hardware reset)

Receive error in MII/RMII mode as output

It is recommended to always pull this pin low on power-up or hardware reset.

22

SPEED/

TXCLK

IO/Ipu

10M/100M select as input (during power on reset/hardware reset)

Transmit clock in MII mode as output

23

TXEN

Input

Transmit enable in RMII/MII mode

24

TXD0

Input

Transmit data Bit 0 in RMII/MII mode

25

VDDD

Power

3.3 V Power Supply

26

TXD1

Input

Transmit data Bit 1 in RMII/MII mode

27

TXT2

Input

Transmit data Bit 2 in MII mode

28

TXD3

Input

Transmit data Bit 3 in MII mode

29

REFOUT

Output

25 MHz crystal output, floating in RMII mode

30

REFIN

Input

25 MHz crystal (or clock) input in MII mode. 50 MHz clock input in RMII mode.

相关PDF资料 |

PDF描述 |

|---|---|

| IDT72261LA15PF | IC FIFO 8192X18 LP 15NS 64QFP |

| VE-B5F-IV-F1 | CONVERTER MOD DC/DC 72V 150W |

| MS27473T12A98SA | CONN PLUG 10POS STRAIGHT W/SCKT |

| VE-B5D-IV-F4 | CONVERTER MOD DC/DC 85V 150W |

| IDT72255LA20PFI | IC FIFO 8KX18 LP 20NS 64QFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS1894K-32LFT | 功能描述:PHYCEIVER LOW PWR 3.3V 32QFN RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:PHYceiver™ 产品培训模块:RS-232 & USB Transceiver 标准包装:2,000 系列:- 类型:收发器 驱动器/接收器数:1/1 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-SSOP(0.209",5.30mm 宽) 供应商设备封装:16-SSOP 包装:带卷 (TR) 其它名称:296-19849-2 |

| ICS1894K-33LF | 制造商:Integrated Device Technology Inc 功能描述:PHYCEIVER LOW PWR 3.3V 32QFN |

| ICS1894K-33LFT | 制造商:Integrated Device Technology Inc 功能描述:PHYCEIVER LOW PWR 3.3V 32QFN |

| ICS1894K-34LF | 制造商:Integrated Device Technology Inc 功能描述:PHYCEIVER LOW PWR 3.3V 32QFN |

| ICS1894K-34LFT | 制造商:Integrated Device Technology Inc 功能描述:PHYCEIVER LOW PWR 3.3V 32QFN |

发布紧急采购,3分钟左右您将得到回复。