- 您现在的位置:买卖IC网 > PDF目录9982 > ICS1894K-32LF (IDT, Integrated Device Technology Inc)PHYCEIVER LOW PWR 3.3V 32QFN PDF资料下载

参数资料

| 型号: | ICS1894K-32LF |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 48/50页 |

| 文件大小: | 0K |

| 描述: | PHYCEIVER LOW PWR 3.3V 32QFN |

| 标准包装: | 490 |

| 类型: | PHY 收发器 |

| 规程: | MII,RMII |

| 电源电压: | 3.14 V ~ 3.47 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-VFQFN 裸露焊盘 |

| 供应商设备封装: | 32-QFN 裸露焊盘(5x5) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页当前第48页第49页第50页

ICS1894-32

10BASE-T/100BASE-TX INTEGRATED PHYCEIVER WITH RMII INTERFACE

PHYCEIVER

IDT 10BASE-T/100BASE-TX INTEGRATED PHYCEIVER WITH RMII INTERFACE

7

ICS1894-32

REV M 021512

The MIIM interface consists of the following:

A physical connection that incorporates the clock line

(MDC) and the data line (MDIO).

A specific protocol that operates across the

aforementioned physical connection that allows an

external controller to communicate with one or more

ICS1894-32 devices. Each ICS1894-32 device is

assigned a PHY address between 1 and 7 by the P[4:0]

strapping pins. P3 and P4 address bits are hardcoded to

‘0’ in design.

An internal addressable set of thirty-one 8-bit MDIO

registers. Register [0:6] are required, and their functions

are defined by the IEEE 802.3u Specification. The

additional registers are provided for expanded

functionality.

The ICS1894-32 supports MIIM in both MII mode and RMII

mode.

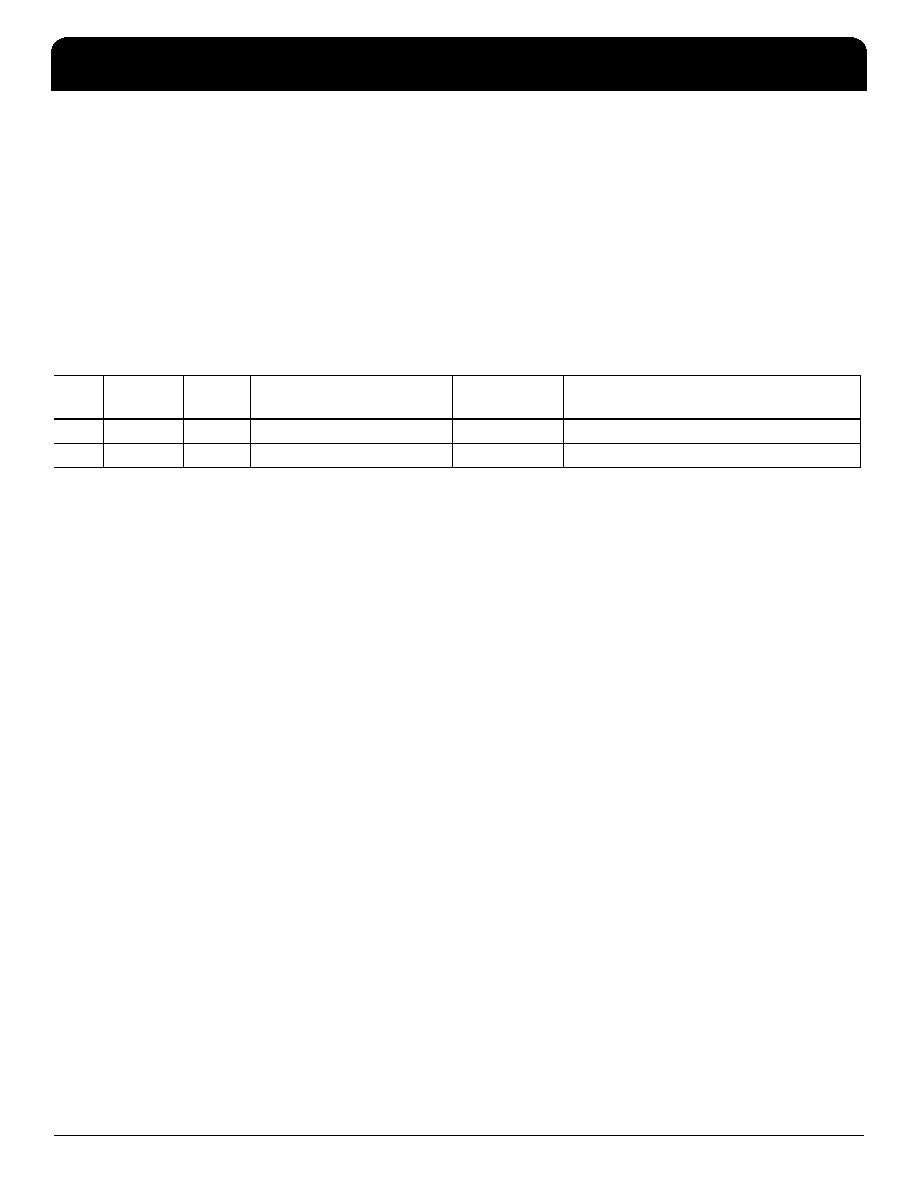

The following table shows the MII Management frame

format for the ICS1894-32.

MII Management Frame Format

Interrupt (INT)

P2/INT (pin 11) is an optional interrupt signal that is used to

inform the external controller that there has been a status

update in the ICS1894-32 PHY register. Register 23 shows

the status of the various interrupts while register 22 controls

the enabling/disabling of the interrupts.

MII Data Interface

The Media Independent Interface (MII) is specified in

Clause 22 of the IEEE 802.3u Specification. It provides a

common interface between physical layer and MAC layer

devices, and has the following key characteristics:

Supports 10Mbps and 100Mbps data rates.

Uses a 25MHz reference clock, sourced by the PHY.

Provides independent 4-bit wide (nibble) transmit and

receive data paths.

Contains two distinct groups of signals: one for

transmission and the other for reception.

The ICS1894-32 is configured for MII mode upon power-up

or hardware reset with the following:

A 25MHz crystal connected to REFIN, REFOUT (pins 30,

29), or an external 25MHz clock source (oscillator)

connected to REFIN

Preamble Start of

Frame

Read/Write

OP Code

PHY Address

Bits [4:0]

REG Address

Bits [4:0]

TA

Data Bits

[15:0]

Idle

Read

32 1’s

01

10

00AAA

RRRRR

Z0

DDDDDDDD_DDDDDDDD

Z

Write

32 1’s

01

00AAA

RRRRR

10

DDDDDDDD_DDDDDDDD

Z

相关PDF资料 |

PDF描述 |

|---|---|

| IDT72261LA15PF | IC FIFO 8192X18 LP 15NS 64QFP |

| VE-B5F-IV-F1 | CONVERTER MOD DC/DC 72V 150W |

| MS27473T12A98SA | CONN PLUG 10POS STRAIGHT W/SCKT |

| VE-B5D-IV-F4 | CONVERTER MOD DC/DC 85V 150W |

| IDT72255LA20PFI | IC FIFO 8KX18 LP 20NS 64QFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS1894K-32LFT | 功能描述:PHYCEIVER LOW PWR 3.3V 32QFN RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:PHYceiver™ 产品培训模块:RS-232 & USB Transceiver 标准包装:2,000 系列:- 类型:收发器 驱动器/接收器数:1/1 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-SSOP(0.209",5.30mm 宽) 供应商设备封装:16-SSOP 包装:带卷 (TR) 其它名称:296-19849-2 |

| ICS1894K-33LF | 制造商:Integrated Device Technology Inc 功能描述:PHYCEIVER LOW PWR 3.3V 32QFN |

| ICS1894K-33LFT | 制造商:Integrated Device Technology Inc 功能描述:PHYCEIVER LOW PWR 3.3V 32QFN |

| ICS1894K-34LF | 制造商:Integrated Device Technology Inc 功能描述:PHYCEIVER LOW PWR 3.3V 32QFN |

| ICS1894K-34LFT | 制造商:Integrated Device Technology Inc 功能描述:PHYCEIVER LOW PWR 3.3V 32QFN |

发布紧急采购,3分钟左右您将得到回复。