- 您现在的位置:买卖IC网 > PDF目录67695 > ICS853058AGT 853058 SERIES, 8 LINE TO 1 LINE MULTIPLEXER, COMPLEMENTARY OUTPUT, PDSO24 PDF资料下载

参数资料

| 型号: | ICS853058AGT |

| 元件分类: | 编、解码器及复用、解复用 |

| 英文描述: | 853058 SERIES, 8 LINE TO 1 LINE MULTIPLEXER, COMPLEMENTARY OUTPUT, PDSO24 |

| 封装: | 4.40 X 7.80 MM, 0.92 MM HEIGHT, MS-153, TSSOP-24 |

| 文件页数: | 17/17页 |

| 文件大小: | 240K |

| 代理商: | ICS853058AGT |

853058AG

www.icst.com/products/hiperclocks.html

REV. A APRIL 24, 2006

9

Integrated

Circuit

Systems, Inc.

ICS853058

8:1, DIFFERENTIAL-TO-

3.3V OR 2.5V LVPECL/ECL CLOCK MULTIPLEXER

LVPECL CLOCK INPUT INTERFACE

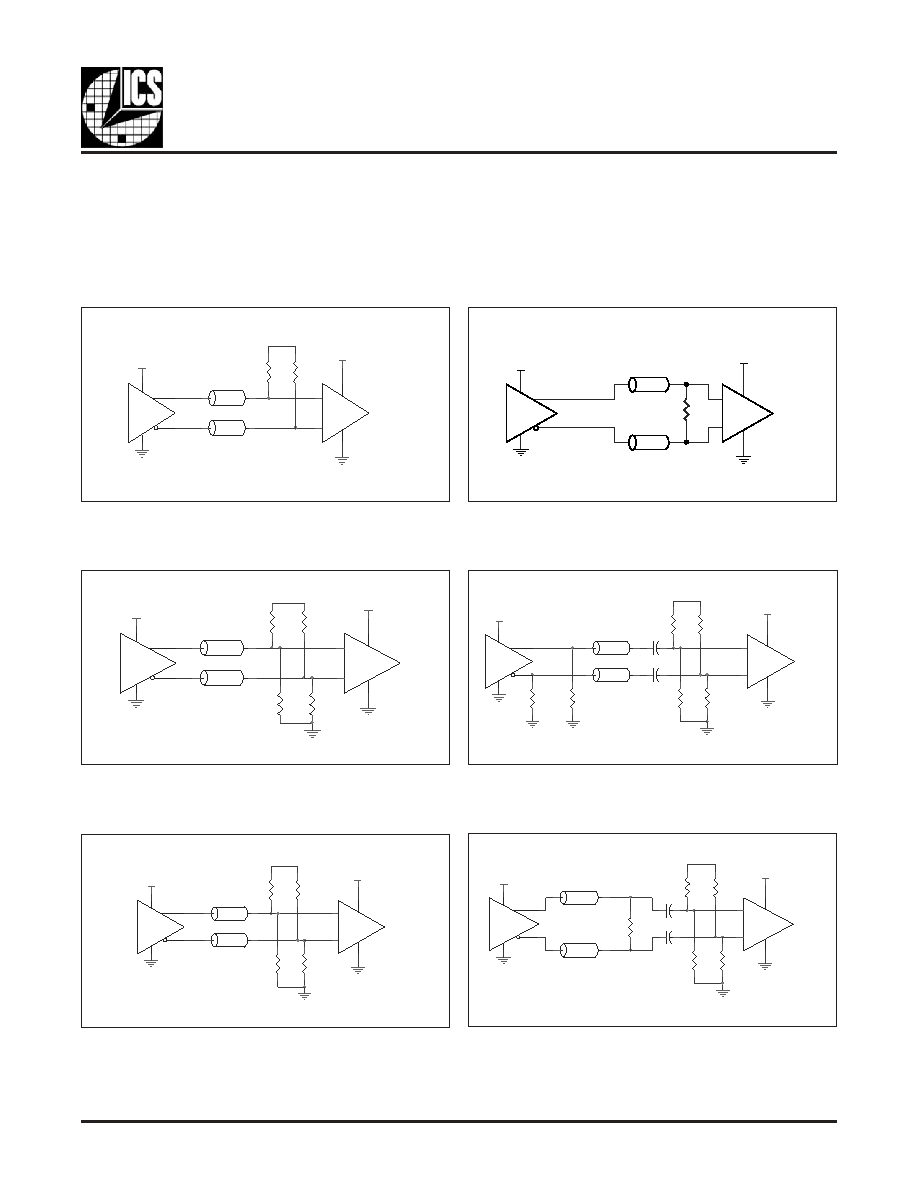

The PCLK /nPCLK accepts LVPECL, CML, SSTL and other

differential signals. Both V

SWING and VOH must meet the VPP

and V

CMR input requirements. Figures 2A to 2F show inter-

face examples for the HiPerClockS PCLK/nPCLK input

driven by the most common driver types. The input inter-

faces suggested here are examples only. If the driver is

from another vendor, use their termination recommenda-

tion. Please consult with the vendor of the driver compo-

nent to confirm the driver termination requirements.

FIGURE 2A. HIPERCLOCKS PCLK/nPCLK INPUT DRIVEN

BY AN

OPEN COLLECTOR CML DRIVER

FIGURE 2B. HIPERCLOCKS PCLK/nPCLK INPUT DRIVEN

BY A

BUILT-IN PULLUP CML DRIVER

FIGURE 2C. HIPERCLOCKS PCLK/nPCLK INPUT DRIVEN

BY A

3.3V LVPECL DRIVER

FIGURE 2F.

HIPERCLOCKS PCLK/nPCLK INPUT DRIVEN

BY A

3.3V LVDS DRIVER

PCLK/nPCLK

2.5V

Zo = 60 Ohm

SSTL

HiPerClockS

PCLK

nPCLK

R2

120

3.3V

R3

120

Zo = 60 Ohm

R1

120

R4

120

2.5V

FIGURE 2E. HIPERCLOCKS PCLK/nPCLK INPUT DRIVEN

BY AN

SSTL DRIVER

HiPerClockS

PCLK

nPCLK

PCLK/nPCLK

3.3V

R2

50

R1

50

3.3V

Zo = 50 Ohm

CML

3.3V

Zo = 50 Ohm

3.3V

HiPerClockS

PCLK

nPCLK

R2

84

R3

125

Input

Zo = 50 Ohm

R4

125

R1

84

LVPECL

3.3V

Zo = 50 Ohm

C2

R2

1K

R5

100

Zo = 50 Ohm

3.3V

C1

R3

1K

LVDS

R4

1K

HiPerClockS

PCLK

nPCLK

R1

1K

Zo = 50 Ohm

3.3V

PC L K /n PC LK

3.3V

R5

100 - 200

3.3V

HiPerClockS

PCLK

nPCLK

R1

125

PCLK/nPCLK

R2

125

R3

84

C1

C2

Zo = 50 Ohm

R4

84

Zo = 50 Ohm

R6

100 - 200

3.3V LVPECL

FIGURE 2D. HIPERCLOCKS PCLK/nPCLK INPUT DRIVEN

BY A

3.3V LVPECL DRIVER WITH AC COUPLE

3.3V

CML Built-In Pullup

R1

100

PCLK

nPCLK

HiPerClockS

PCLK/nPCLK

Zo = 50 Ohm

相关PDF资料 |

PDF描述 |

|---|---|

| ICS8530DY-01 | 8530 SERIES, LOW SKEW CLOCK DRIVER, 16 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

| ICS8530DY-01LF | 8530 SERIES, LOW SKEW CLOCK DRIVER, 16 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

| ICS8530DY-01 | 8530 SERIES, LOW SKEW CLOCK DRIVER, 16 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

| ICS8530DYI-01LFT | 8530 SERIES, LOW SKEW CLOCK DRIVER, 16 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

| ICS8530DYI-01 | 8530 SERIES, LOW SKEW CLOCK DRIVER, 16 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS8530DY01 | 制造商:ICS 功能描述: |

| ICS8530DY-01LF | 功能描述:IC CLK BUFF 1:16 500MHZ 48-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:HiPerClockS™ 产品培训模块:High Bandwidth Product Overview 标准包装:1,000 系列:Precision Edge® 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:4 差分 - 输入:输出:是/是 输入:CML,LVDS,LVPECL 输出:CML 频率 - 最大:2.5GHz 电源电压:2.375 V ~ 2.625 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-VFQFN 裸露焊盘,16-MLF? 供应商设备封装:16-MLF?(3x3) 包装:带卷 (TR) |

| ICS8530DY-01LFT | 功能描述:IC CLK BUFF 1:16 500MHZ 48-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:HiPerClockS™ 标准包装:74 系列:- 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 输入:HCSL, LVCMOS, LVDS, LVPECL, LVTTL 输出:HCSL,LVDS 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:管件 |

| ICS8530DYI-01LF | 功能描述:IC CLK BUFF 1:16 500MHZ 48-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:HiPerClockS™ 标准包装:74 系列:- 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 输入:HCSL, LVCMOS, LVDS, LVPECL, LVTTL 输出:HCSL,LVDS 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:管件 |

| ICS8530DYI-01LFT | 功能描述:IC CLK BUFF 1:16 500MHZ 48-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:HiPerClockS™ 标准包装:74 系列:- 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 输入:HCSL, LVCMOS, LVDS, LVPECL, LVTTL 输出:HCSL,LVDS 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。