- 您现在的位置:买卖IC网 > PDF目录67703 > ICS87946AYI-01LF (INTEGRATED DEVICE TECHNOLOGY INC) LOW SKEW CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 PDF资料下载

参数资料

| 型号: | ICS87946AYI-01LF |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | LOW SKEW CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 |

| 封装: | 7 X 7 MM, 1.40 MM HEIGHT, MS-026, LQFP-32 |

| 文件页数: | 1/15页 |

| 文件大小: | 1230K |

| 代理商: | ICS87946AYI-01LF |

LOW SKEW, ÷1, ÷2 LVPECL-TO-LVCMOS/LVTTL

CLOCK GENERATOR

ICS87946I-01

IDT / ICS 16:1, SINGLE-ENDED MULTIPLEXER

1

ICS87946AYI-01 REV. BMAY 4, 2007

Description

The ICS87946I-01 is a low skew, ÷1, ÷2 Clock

Generator and a member of the HiPerClockS

family of High Performance Clock Solutions from

IDT. The ICS87946I-01 has one LVPECL clock input

pair. The PCLK/PCLK pair can accept LVPECL,

CML, or SSTL input levels. The low impedance LVCMOS/LVTTL

outputs are designed to drive 50

series or parallel terminated

transmission lines. The effective fanout can be increased from 10

to 20 by utilizing the ability of the outputs to drive two series

terminated lines.

The divide select inputs, DIV_SELx, control the output frequency

of each bank. The outputs can be utilized in the ÷1, ÷2 or a

combination of ÷1 and ÷2 modes. The master reset input, MR/OE,

resets the internal frequency dividers and also controls the active

and high impedance states of all outputs.

The ICS87946I-01 is characterized at 3.3V core/3.3V output and

3.3V core/2.5V output. Guaranteed bank, output and part-to-part

skew characteristics make the ICS87946I-01 ideal for those clock

distribution applications demanding well defined performance and

repeatability.

Features

Ten single ended LVCMOS/LVTTL outputs,

7

typical output impedance

LVPECL clock input pair

PCLK/PCLK supports the following input levels:

LVPECL, CML, SSTL

Maximum input frequency: 250MHz

Output skew: 120ps (maximum)

Part-to-part skew: 700ps (maximum)

Multiple frequency skew: 320ps (maximum)

Additive phase jitter, RMS: 0.19ps (typical)

3.3V core, 3.3V or 2.5V output supply modes-40°C to 85°C

ambient operating temperature

Available in both standard (RoHS 5) and lead-free (RoHS 6)

packages

HiPerClockS

ICS

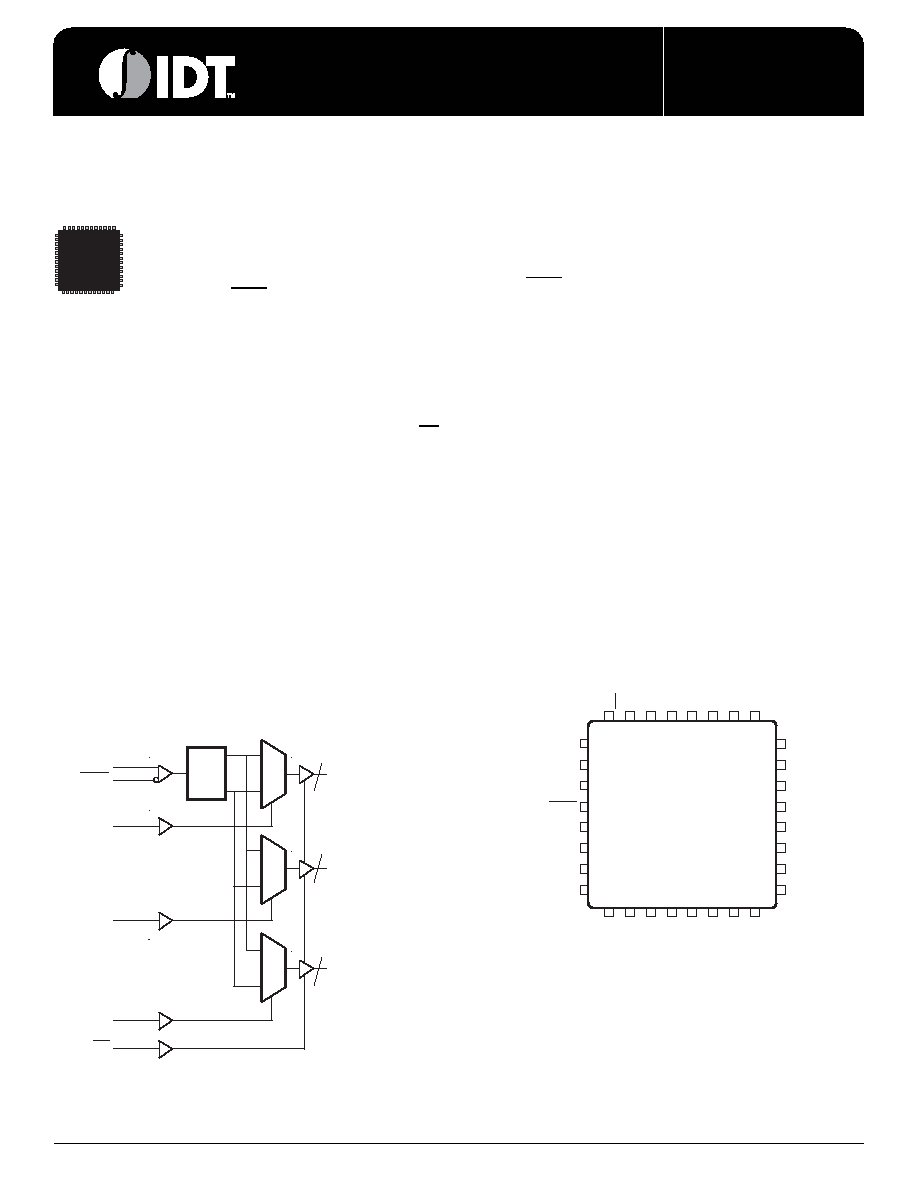

9

10 11 12 13 14 15 16

32 31 30

29 28

27 26 25

1

2

3

4

5

6

7

8

24

23

22

21

20

19

18

17

nc

VDD

PCLK

DIV_SELA

DIV_SELB

DIV_SELC

GND

QB0

VDDB

QB1

GND

QB2

VDDB

VDDC

V

DDC

QC0

GND

QC1

V

DDC

QC2

GND

QC3

GND

QA0

V

DDA

QA1

GND

QA2

V

DDA

MR/OE

ICS87946I-01

32-Lead LQFP

7mm x 7mm x 1.45mm

package body

Y Package

Top View

Pin Assignment

Block Diagram

PCLK

DIV_SELA

QA0:QA2

0

1

÷1

÷2

Pullup

Pulldown

Pullup

Pulldown

DIV_SELB

DIV_SELC

QC0:QC3

0

1

Pulldown

MR/OE Pulldown

QB0:QB2

0

1

0

1

Pulldown

3

4

相关PDF资料 |

PDF描述 |

|---|---|

| ICS87946AYI-01T | LOW SKEW CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 |

| ICS87949AY-01LF | LOW SKEW CLOCK DRIVER, 15 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

| ICS87949AY-01 | LOW SKEW CLOCK DRIVER, 15 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

| ICS87949AY-01LFT | LOW SKEW CLOCK DRIVER, 15 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

| ICS87949AY-01T | LOW SKEW CLOCK DRIVER, 15 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS87946AYI-01LFT | 功能描述:IC CLOCK GENERATOR 32-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS87946AYI-147 | 制造商:Integrated Device Technology Inc 功能描述:IC CLOCK DIVIDER 32LQFP |

| ICS87946AYI-147LF | 功能描述:IC CLOCK GENERATOR 32-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS87946AYI-147LFT | 功能描述:IC CLOCK GENERATOR 32-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS87946AYI-147T | 制造商:Integrated Device Technology Inc 功能描述:IC CLOCK DIVIDER 32LQFP |

发布紧急采购,3分钟左右您将得到回复。