- 您现在的位置:买卖IC网 > PDF目录67704 > ICS9148F-14 (INTEGRATED DEVICE TECHNOLOGY INC) 66.6 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 PDF资料下载

参数资料

| 型号: | ICS9148F-14 |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 66.6 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 封装: | 0.300 INCH, SSOP-48 |

| 文件页数: | 11/18页 |

| 文件大小: | 807K |

| 代理商: | ICS9148F-14 |

2

ICS9148-14

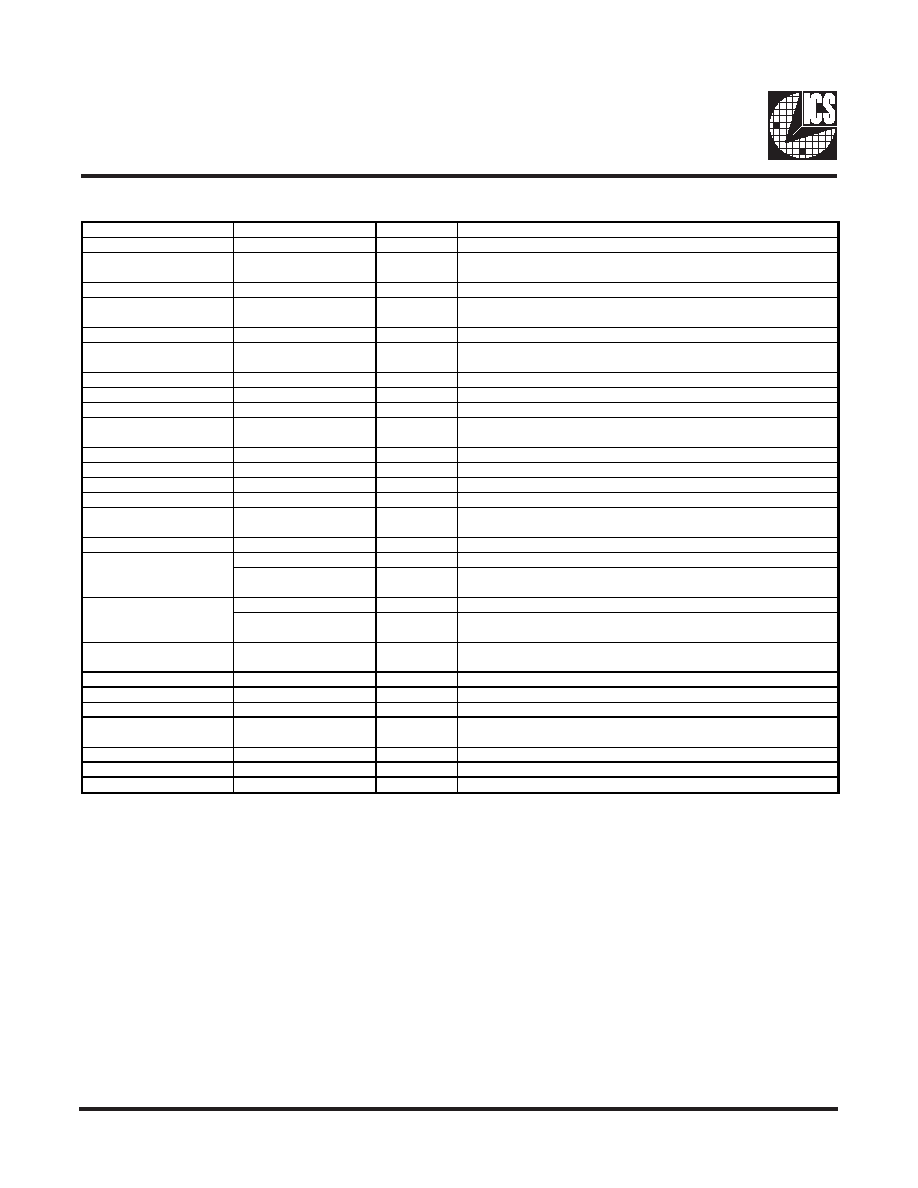

Pin Descriptions

Power Groups

VDD = Supply for PLL core

GND1,VDD1=REF(0:3),X1,X2

GND2,VDD2=PCICLK(0:4),E_PCICLK

GND3, VDD3 = SDRAM (0:5), SDRAM6/CPU_STOP#, SDRAM7/PCI_STOP#,

Ground (GND3) for CPU outputs and CPUPLL

GND4,VDD4 = 48/24MHz

GNDH,VDDH=AGP

VDDL=CPUCLK(0:2)

PIN NUMBER

PIN NAME

TYPE

DESCRIPTION

2, 1, 47, 46

REF (0:3)

OUT

Reference clock Outputs

3, 10, 17, 24,

31, 37, 42

GND ((1:4, H)

PWR

Ground pins for entire circuit. See "Power Groups" description for

specific outputs and internal logic connected to pins.

4

X1

IN

Crystal or reference input, has internal crystal load cap

5

X2

OUT

Crystal output, has internal load cap and feedback

resistor to X1

6

MODE

IN

Input function selection (no pullup)

7, 15

VDD2

PWR

Supply for PCICLK_F, PCICLK (0:4), and E_PCICLK nominal

3.3V

8

N/C

-

Not connected

9, 11, 12, 13, 14

PCICLK (0:4)

OUT

PCI clocks

16

E_PCICLK

OUT

Early PCI clock offset from other PCI clocks

18

FSEL

IN

Selects 100MHz or 66.6MHz for SDRAM and CPU at power up.

(no pullup)

19

SDATA

IN

I2C data input (no pullup), is 5V input tolerant

20

SCLK

IN

I2C clock input (no pullup), is 5V input tolerant

21

VDD4

PWR

Supply for 48/24MHz, nominal 3.3V

22

48/24MHz

OUT

48/24MHz driver output for USB or Super I/O

23

PWR_DWN#

IN

Powers down chip, active low, stopping outputs, OSC and PLL.

(no pullup)

25

VDD

PWR

Supply for PLL core, nominal 3.3V

26

SDRAM7

OUT

SDRAM clock matches CPU frequency

PCI_STOP#

IN

Halts PCICLK (0:4), AGP and E_PCICLK at logic "0" level

when low, see function table

27

SDRAM6

OUT

SDRAM clock matches CPU frequency.

CPU_STOP#

IN

Halts CPU CLK (0:2) at logic "0" level when low, see function

table.

28, 34

VDD3

PWR

Supply for SDRAM (0:5), SDRAM6/CPU_STOP#,

SDRAM7/PCI_STOP#, nominal 3.3V

40

VDDL

PWR

Supply for CPUCLK (0:2), either 2.5 or 3.3V nominal

41, 39, 38

CPUCLK (0:2)

OUT

CPUCLK clock output, powered by VDDL2

36, 35, 33, 32, 30, 29

SDRAM (0:5)

OUT

SDRAMs clock matches CPU frequency

43

AGP

OUT

AGP clock output. Powered by VDDH see frequency select table.

Defined as 2X PCI.

44

VDDH

PWR

Supply for AGP, 3.3V nominal

45

CPU3.3-2.5#

IN

3.3 or 2.5 VDD buffer strength selection, has no pullup.

48

VDD1

PWR

Supply for REF (0:3), X1, X2, nominal 3.3V

相关PDF资料 |

PDF描述 |

|---|---|

| ICS9148F-17-LF | 100.3569 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| ICS9148F-17 | 100.3569 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| ICS9148F-18LF | 100 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO28 |

| ICS9148F-25 | 83.3 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| ICS9148F-32 | 100 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS9148F-17 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:CPU System Clock Generator |

| ICS9148F-18 | 制造商:ICS 制造商全称:ICS 功能描述:Pentium/ProTM System Clock Chip |

| ICS9148F-20 | 制造商:ICS 制造商全称:ICS 功能描述:Pentium/ProTM System Clock Chip |

| ICS9148F25 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Industrial Control IC |

| ICS9148F-25 | 功能描述:IC CLK SYNTHESIZER CHIP 48-SSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。