- 您现在的位置:买卖IC网 > PDF目录67706 > ICS9250YF-30LF-T (INTEGRATED DEVICE TECHNOLOGY INC) 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 PDF资料下载

参数资料

| 型号: | ICS9250YF-30LF-T |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 封装: | 0.300 INCH, SSOP-56 |

| 文件页数: | 1/15页 |

| 文件大小: | 337K |

| 代理商: | ICS9250YF-30LF-T |

Integrated

Circuit

Systems, Inc.

ICS9250-30

0398A—07/03/02

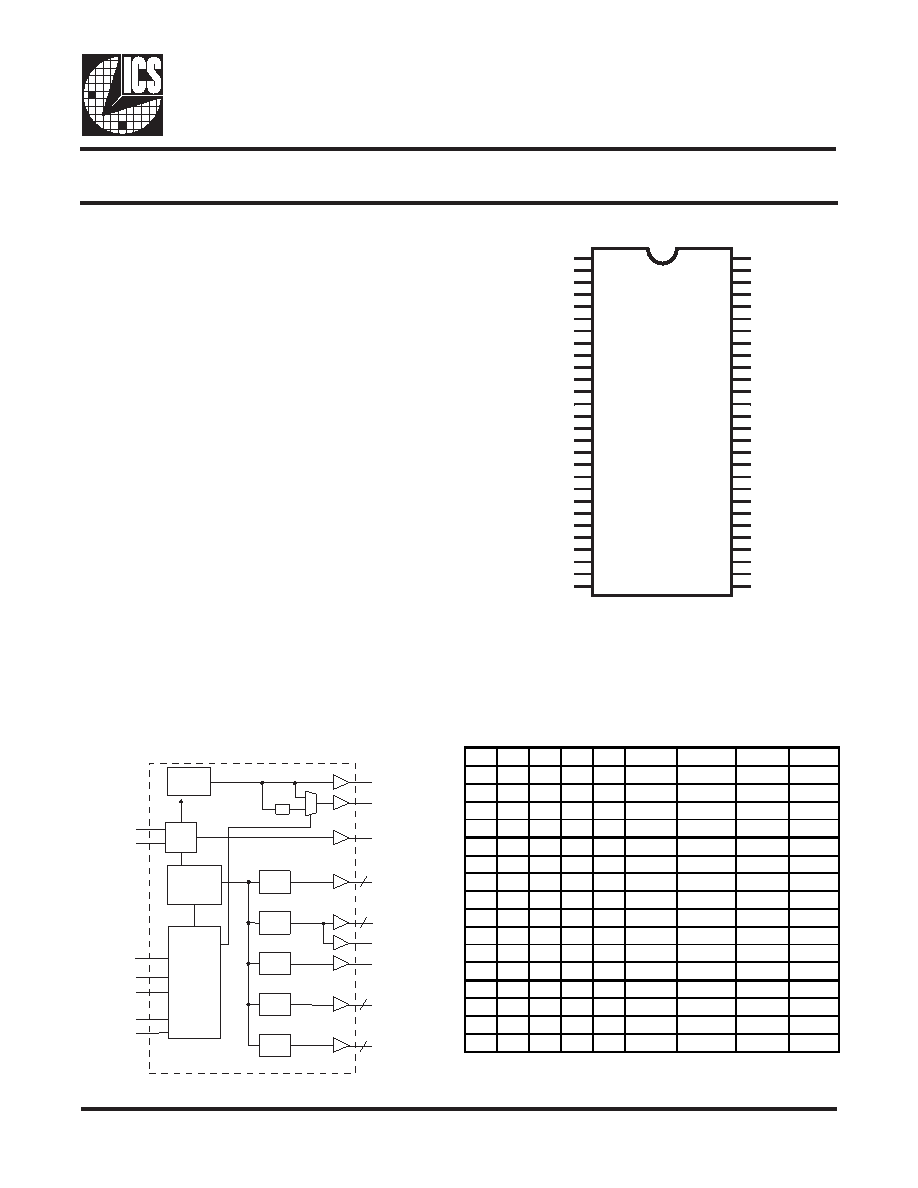

Block Diagram

Pin Configuration

Recommended Application:

810/810E and Solano type chipset

Output Features:

2 - CPUs @ 2.5V, up to 200MHz.

13 - SDRAM @ 3.3V, up to 200MHz.

3 - 3V66 @ 3.3V, 2x PCI MHz.

8 - PCI @3.3V.

1 - 48MHz, @3.3V fixed.

1 - 24/48MHz @ 3.3V

1 - REF @3.3V, 14.318MHz.

1 - IOAPIC @ 2.5V.

Features:

Support PC133 SDRAM.

Up to 200MHz frequency support

Support power management through PD#.

Spread spectrum for EMI control

(± 0.25% Center Spread or 0 to -0.5% down spread)

Uses external 14.318MHz crystal

FS pins for frequency select

Key Specifications:

CPU Output Jitter: <250ps

CPU Output Skew: <175ps

PCI Output Skew: <500ps

3V66 Output Skew <175ps

For group skew timing, please refer to the

Group Timing Relationship Table.

Frequency Generator & Integrated Buffers for Celeron & PII/III

56-Pin 300 mil SSOP

1. These pins will have 1.5 to 2X drive strength.

* 120K ohm pull-up to VDD on indicated inputs.

SDATA

SCLK

PLL2

PLL1

Spread

Spectrum

48MHz

24_48MHz

CPUCLK [1:0]

2

12

8

3

SDRAM [11:0]

IOAPIC

PCICLK [7:0]

SDRAM_F

3V66 [2:0]

X1

X2

XTAL

OSC

CPU

DIVDER

SDRAM

DIVDER

IOAPIC

DIVDER

PCI

DIVDER

3V66

DIVDER

FS[4:0]

PD#

SEL24_48#

Control

Logic

Config.

Reg.

/ 2

REF0

VDDREF

X1

X2

GNDREF

GND3V66

3V66-1

3V66-2

VDD3V66

VDDPCI

*FS0/PCICLK0

*FS1/PCICLK1

*SEL24_48#/PCICLK2

GNDPCI

PCICLK3

PCICLK4

PCICLK5

VDDPCI

PCICLK6

PCICLK7

GNDPCI

PD#

SCLK

SDATA

VDDSDR

SDRAM11

SDRAM10

GNDSDR

3V66-0

1

REF0/FS4*

VDDLAPIC

IOAPIC

VDDLCPU

CPUCLK0

CPUCLK1

GNDLCPU

GNDSDR

SDRAM0

SDRAM1

SDRAM2

VDDSDR

SDRAM3

SDRAM4

SDRAM5

GNDSDR

SDRAM6

SDRAM7

SDRAM_F

VDDSDR

GND48

24_48MHz/FS2 *

48MHz/FS3*

VDD48

VDDSDR

SDRAM8

SDRAM9

GNDSDR

1

ICS9250-30

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

FS4 FS3 FS2 FS1 FS0

CPU

SDRAM

3V66

PCI

0000

0

66.67

100.00

66.67

33.33

0001

1

68.33

102.50

68.33

34.17

0011

0

80.00

120.00

80.00

40.00

0011

1

83.00

124.50

83.00

41.50

0100

0

100.00

66.67

33.33

0101

1

103.00

68.67

34.33

0111

0

115.00

76.67

38.33

0111

1

200.00

66.67

33.33

1000

0

133.33

66.67

33.33

1000

1

166.67

83.34

41.67

1001

1

137.00

68.50

34.25

1011

1

160.00

80.00

40.00

1100

0

133.33

100.00

66.67

33.33

1100

1

166.67

125.00

83.34

41.67

1101

1

137.00

102.75

68.50

34.25

1111

1

160.00

120.00

80.00

40.00

Functionality

For other hardware/I

2C selectable frequencies please

refer to Byte 0 frequency select register.

相关PDF资料 |

PDF描述 |

|---|---|

| ICS9250YF-37-T | 144 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| ICS9250YF-38LF-T | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| ICS9250YG-22LF-T | 133 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| ICS9250YF-22LF-T | 133 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| ICS9250YF-22-T | 133 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS9250YF-30-T | 制造商:ICS 制造商全称:ICS 功能描述:Frequency Generator & Integrated Buffers for Celeron & PII/III⑩ |

| ICS9250YF-32-T | 制造商:ICS 制造商全称:ICS 功能描述:Frequency Generator & Integrated Buffers for PII/III⑩ |

| ICS9250YF-38-T | 制造商:ICS 制造商全称:ICS 功能描述:Frequency Generator with 200MHz Differential CPU Clocks |

| ICS9250YG-22-T | 制造商:ICS 制造商全称:ICS 功能描述:Frequency Generator for P IV⑩ |

| ICS9250YG-38-T | 制造商:ICS 制造商全称:ICS 功能描述:Frequency Generator with 200MHz Differential CPU Clocks |

发布紧急采购,3分钟左右您将得到回复。