- 您现在的位置:买卖IC网 > PDF目录67707 > ICS950104YFT 166 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 PDF资料下载

参数资料

| 型号: | ICS950104YFT |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 166 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 封装: | 0.300 INCH, MO-118, SSOP-48 |

| 文件页数: | 12/19页 |

| 文件大小: | 222K |

| 代理商: | ICS950104YFT |

2

ICS950104

Advance Information

Third party brands and names are the property of their respective owners.

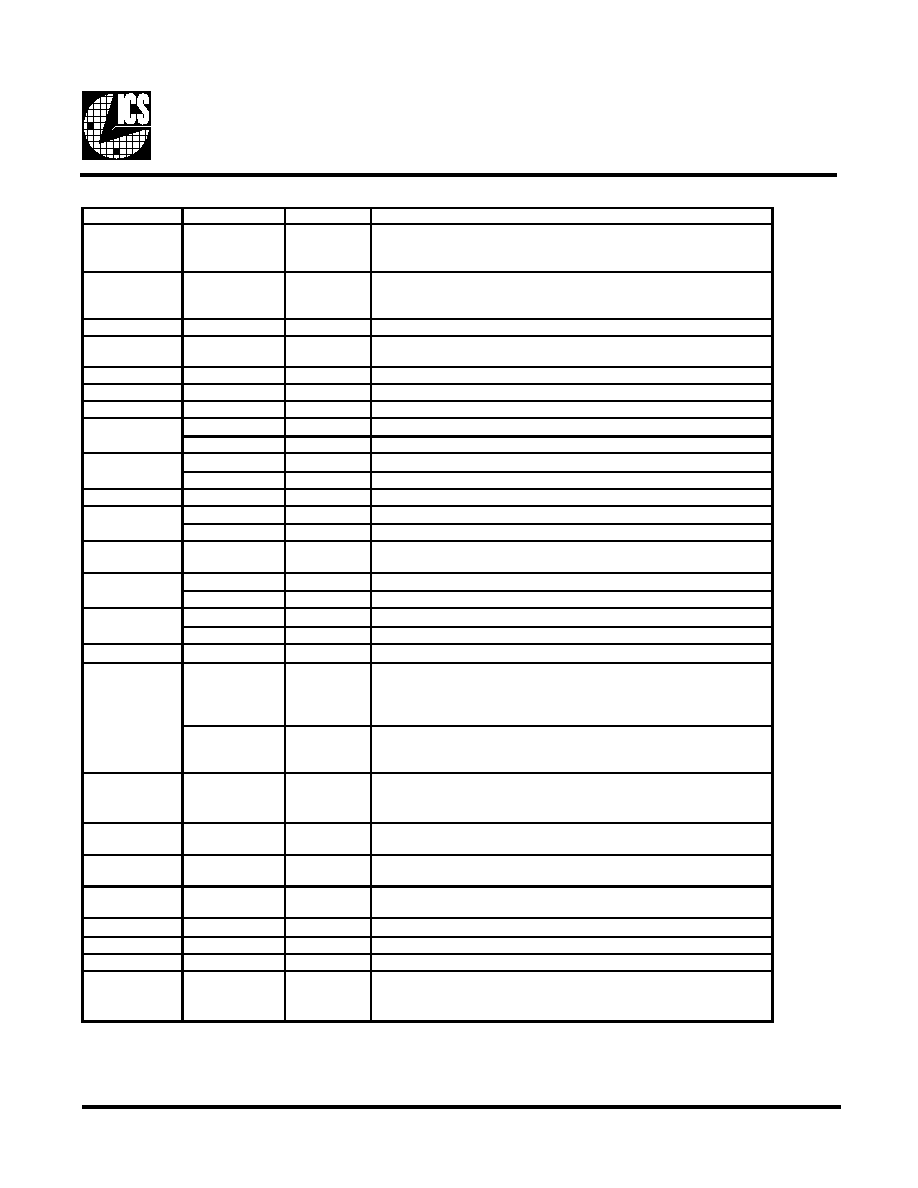

Pin Descriptions

Notes:

1:

Internal Pull-up Resistor of 120K to 3.3V on indicated inputs

2:

Bidirectional input/output pins, input logic levels are latched at internal power-on-reset. Use 10Kohm resistor

to program logic Hi to VDD or GND for logic low.

3:

Internal Pull-down resistor of 120K to GND on indicated inputs.

PIN NUMBER

PIN NAME

TYPE

DESCRIPTION

1

CPUCLKC0

OUT

"Complementary" clocks of differential pair CPU outputs. These clocks are 180°

out of phase with SDRAM clocks. These open drain outputs need an external

1.5V pull-up.

2

CPUCLKT0

OUT

"True" clocks of differential pair CPU outputs. These clocks are in phase with

SDRAM clocks. These open drain outputs need an external 1.5V pull-up.

3, 9, 18, 30, 37

VDD

PWR

Power supply pins, nominal 3.3V

4, 12, 17, 25, 31,

36, 46, 48

GND

PWR

Ground pins

5, 22

AVDD

PWR

Analog power supply for 3.3V

6

X1

IN

Crystal input,nominally 14.318MHz.

7

X2

OUT

Crystal output, nominally 14.318MHz.

FS0

2, 3

IN

Frequency select pin.

REF0

OUT

14.318 MHz reference clock.

FS1

2, 3

IN

Frequency select pin.

REF1

OUT

14.318 MHz reference clock.

11

REF2

OUT

14.318 MHz reference clock.

FS2

1, 3

IN

Frequency select pin.

PCICLK_F

OUT

Free running PCICLK not stoped by PCI_STOP#

21, 20, 19, 16, 15,

14

PCICLK(5:0)

OUT

PCI clock outputs.

MULTSEL

2, 3

IN

3.3V LVTTL input for selecting the current multiplier for CPU outputs.

24_48MHz

OUT

Selectable 48 or 24MHz output

FS3

2, 3

IN

Frequency select pin.

48MHz

OUT

48MHz output clock

26

SCLK

IN

Clock input of I

2C input, 5V tolerant input

PD#

1

IN

Asynchronous active low input pin used to power down the device into a low

power state. The internal clocks are disabled and the VCO and the crystal are

stopped. The latency of the power down will not be greater than 3ms. This pin

will be activiated when

VttPWRGD#

IN

This 3.3V LVTTL input is a level sensitive strobe used to determine when FS

and MULTISEL0 inputs are valid and are ready to be sampled (active low)

28

CPU_STOP#

1

IN

This asynchronous input halts CPU, SDRAM, and AGP clocks at logic "0" level

when driven low, the stop selection can be programmed through I

2C.

29

PCI_STOP#

1

IN

Stops all PCICLKsbesides the PCICLK_F clocks at logic 0 level,

when input low

32, 33, 34, 35, 38,

39, 40, 41

SDRAM ( 7:0 )

OUT

SDRAM clock outputs.

42

SDRAM_STOP#

1

IN

Stops all SDRAMs besides the SDRAM_F clocks at logic 0 level, when input

low

43

SDATA

IN

Data input for I

2C serial input, 5V tolerant input

44

VDDL

PWR

Power supply pins, nominal 2.5V

45

CPUCLK

OUT

2.5V CPU clock

47

I REF

OUT

This pin establishes the reference current for the CPUCLK pairs. This

pin requires a fixed precision resistor tied to ground in order to establish

the appropriate current.

23

27

10

8

13

24

相关PDF资料 |

PDF描述 |

|---|---|

| ICS950201YFT | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| ICS950201YFT | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| ICS950201YF-T | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| ICS950201YGLF-T | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| ICS950201YFLF-T | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS950201 | 制造商:ICS 制造商全称:ICS 功能描述:Programmable Timing Control Hub⑩ for P4⑩ |

| ICS950201AFLF | 功能描述:IC TIMING CTRL HUB P4 56-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:TCH™ 标准包装:1 系列:- 类型:时钟/频率发生器,多路复用器 PLL:是 主要目的:存储器,RDRAM 输入:晶体 输出:LVCMOS 电路数:1 比率 - 输入:输出:1:2 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:Digi-Reel® 其它名称:296-6719-6 |

| ICS950201AFLFT | 功能描述:IC TIMING CTRL HUB P4 56-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:TCH™ 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| ICS950201AFT-IB0 | 制造商:Ics 功能描述:ELECTRONIC COMPONENT 制造商:Integrated Device Technology Inc 功能描述:ELECTRONIC COMPONENT |

| ICS950201AG | 制造商:INT_CIR_SYS 功能描述: |

发布紧急采购,3分钟左右您将得到回复。