- 您现在的位置:买卖IC网 > Datasheet目录329 > IDT70V27S15PF (IDT, Integrated Device Technology Inc)IC SRAM 512KBIT 15NS 100TQFP Datasheet资料下载

参数资料

| 型号: | IDT70V27S15PF |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 11/21页 |

| 文件大小: | 0K |

| 描述: | IC SRAM 512KBIT 15NS 100TQFP |

| 标准包装: | 6 |

| 格式 - 存储器: | RAM |

| 存储器类型: | SRAM - 双端口,异步 |

| 存储容量: | 512K (32K x 16) |

| 速度: | 15ns |

| 接口: | 并联 |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | 0°C ~ 70°C |

| 封装/外壳: | 100-LQFP |

| 供应商设备封装: | 100-TQFP(14x14) |

| 包装: | 托盘 |

| 其它名称: | 70V27S15PF |

�� �

�

�

�IDT� 70V27S/L�

�High-Speed� 3.3V� 32K� x� 16� Dual-Port� Static� RAM�

�Commercial� and� Industrial� Temperature� Range�

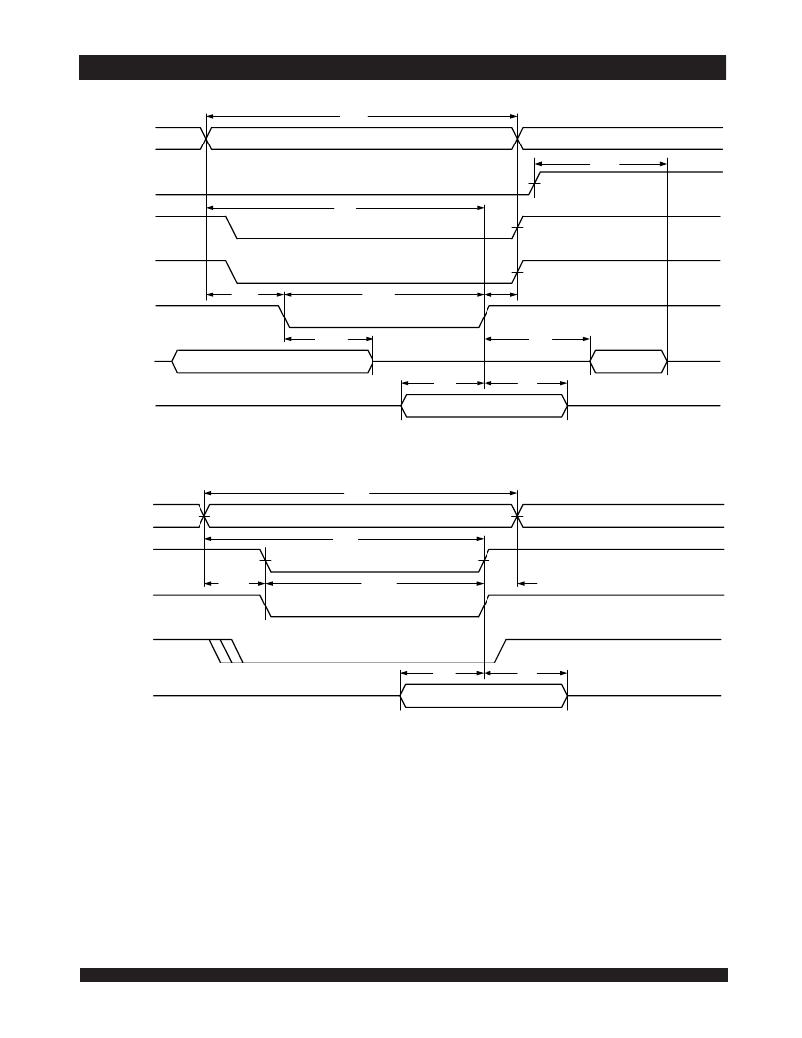

�Timing� Waveform� of� Write� Cycle� No.� 1,� R/� W� Controlled� Timing�

�t� WC�

�ADDRESS�

�(1,5,8)�

�OE�

�t� AW�

�t� HZ�

�(7)�

�CE� or� SEM�

�UB� or� LB�

�(9,10)�

�(9)�

�t� AS� (6)�

�t� WP�

�(2)�

�t� WR�

�(3)�

�R/� W�

�t� WZ� (7)�

�t� OW�

�DATA� OUT�

�(4)�

�t� DW�

�t� DH�

�(4)�

�DATA� IN�

�3603� drw� 07�

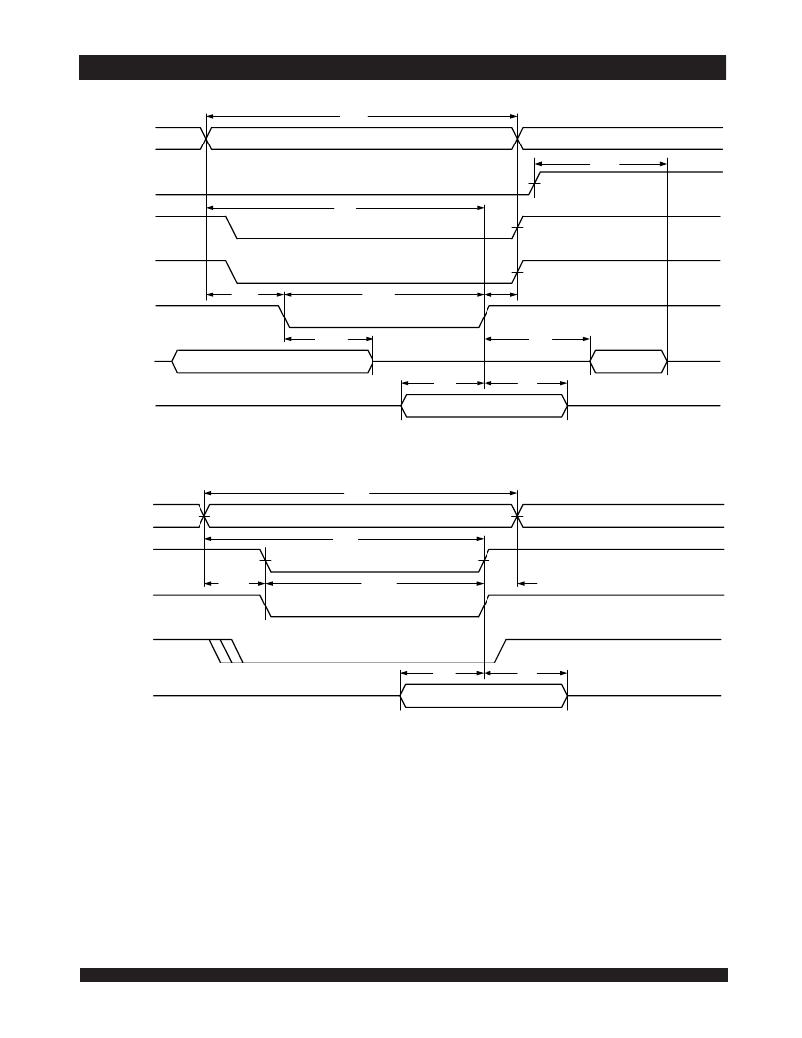

�Timing� Waveform� of� Write� Cycle� No.� 2,� CE� ,� UB� ,� LB� Controlled� Timing� (1,5)�

�t� WC�

�ADDRESS�

�t� AW�

�CE� or� SEM�

�(9,10)�

�UB� or� LB�

�(9)�

�R/� W�

�t� AS� (6)�

�t� EW� (2)�

�t� DW�

�t� WR� (3)�

�t� DH�

�DATA� IN�

�3603� drw� 08�

�NOTES:�

�1.� R/� W� or� CE� or� UB� and� LB� must� be� HIGH� during� all� address� transitions.�

�2.� A� write� occurs� during� the� overlap� (t� EW� or� t� WP� )� of� a� LOW� CE� and� a� LOW� R/� W� for� memory� array� writing� cycle.�

�3.� t� WR� is� measured� from� the� earlier� of� CE� or� R/� W� (or� SEM� or� R/� W� )� going� HIGH� to� the� end� of� write� cycle.�

�4.� During� this� period,� the� I/O� pins� are� in� the� output� state� and� input� signals� must� not� be� applied.�

�5.� If� the� CE� or� SEM� LOW� transition� occurs� simultaneously� with� or� after� the� R/� W� LOW� transition,� the� outputs� remain� in� the� High-impedance� state.�

�6.� Timing� depends� on� which� enable� signal� is� asserted� last,� CE� or� R/� W� .�

�7.� This� parameter� is� guaranteed� by� device� characterization,� but� is� not� production� tested.� Transition� is� measured� 0mV� from� steady� state� with� the� Output� Test� Load� (Figure�

�2).�

�8.� If� OE� is� LOW� during� R/� W� controlled� write� cycle,� the� write� pulse� width� must� be� the� larger� of� t� WP� or� (t� WZ� +� t� DW� )� to� allow� the� I/O� drivers� to� turn� off� and� data� to� be� placed�

�on� the� bus� for� the� required� t� DW� .� If� OE� is� HIGH� during� an� R/� W� controlled� write� cycle,� this� requirement� does� not� apply� and� the� write� pulse� can� be� as� short� as� the�

�specified� t� WP� .�

�9.� To� access� RAM,� CE� =� V� IL� and� SEM� =� V� IH� .� To� access� semaphore,� CE� =� V� IH� and� SEM� =� V� IL� .� t� EW� must� be� met� for� either� condition.�

�10.� Refer� to� Chip� Enable� Truth� Table.�

�11�

�相关PDF资料 |

PDF描述 |

|---|---|

| IDT70V28L20PFGI | IC SRAM 1MBIT 20NS 100TQFP |

| IDT70V3319S166PRFG | IC SRAM 4MBIT 166MHZ 128TQFP |

| IDT70V3379S5PRFI | IC SRAM 576KBIT 5NS 128TQFP |

| IDT70V3389S5PRFI | IC SRAM 1.125MBIT 5NS 128TQFP |

| IDT70V3569S5DRI | IC SRAM 576KBIT 5NS 208QFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT70V27S15PF8 | 功能描述:IC SRAM 512KBIT 15NS 100TQFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:1,000 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 双端口,同步 存储容量:1.125M(32K x 36) 速度:5ns 接口:并联 电源电压:3.15 V ~ 3.45 V 工作温度:-40°C ~ 85°C 封装/外壳:256-LBGA 供应商设备封装:256-CABGA(17x17) 包装:带卷 (TR) 其它名称:70V3579S5BCI8 |

| IDT70V27S20PF | 功能描述:IC SRAM 512KBIT 20NS 100TQFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:1,000 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 双端口,同步 存储容量:1.125M(32K x 36) 速度:5ns 接口:并联 电源电压:3.15 V ~ 3.45 V 工作温度:-40°C ~ 85°C 封装/外壳:256-LBGA 供应商设备封装:256-CABGA(17x17) 包装:带卷 (TR) 其它名称:70V3579S5BCI8 |

| IDT70V27S20PF8 | 功能描述:IC SRAM 512KBIT 20NS 100TQFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:1,000 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 双端口,同步 存储容量:1.125M(32K x 36) 速度:5ns 接口:并联 电源电压:3.15 V ~ 3.45 V 工作温度:-40°C ~ 85°C 封装/外壳:256-LBGA 供应商设备封装:256-CABGA(17x17) 包装:带卷 (TR) 其它名称:70V3579S5BCI8 |

| IDT70V27S25PF | 功能描述:IC SRAM 512KBIT 25NS 100TQFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:1,000 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 双端口,同步 存储容量:1.125M(32K x 36) 速度:5ns 接口:并联 电源电压:3.15 V ~ 3.45 V 工作温度:-40°C ~ 85°C 封装/外壳:256-LBGA 供应商设备封装:256-CABGA(17x17) 包装:带卷 (TR) 其它名称:70V3579S5BCI8 |

| IDT70V27S25PF8 | 功能描述:IC SRAM 512KBIT 25NS 100TQFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:1,000 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 双端口,同步 存储容量:1.125M(32K x 36) 速度:5ns 接口:并联 电源电压:3.15 V ~ 3.45 V 工作温度:-40°C ~ 85°C 封装/外壳:256-LBGA 供应商设备封装:256-CABGA(17x17) 包装:带卷 (TR) 其它名称:70V3579S5BCI8 |

发布紧急采购,3分钟左右您将得到回复。