- 您现在的位置:买卖IC网 > PDF目录9948 > IDT723632L15PQF (IDT, Integrated Device Technology Inc)IC FIFO SYNC 512X36X2 132QFP PDF资料下载

参数资料

| 型号: | IDT723632L15PQF |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 2/25页 |

| 文件大小: | 0K |

| 描述: | IC FIFO SYNC 512X36X2 132QFP |

| 标准包装: | 36 |

| 系列: | 7200 |

| 功能: | 同步 |

| 存储容量: | 36.8K(512 x 36 x 2) |

| 数据速率: | 67MHz |

| 访问时间: | 15ns |

| 电源电压: | 4.5 V ~ 5.5 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 132-BQFP 缓冲式 |

| 供应商设备封装: | 132-PQFP(24.13x24.13) |

| 包装: | 托盘 |

| 其它名称: | 723632L15PQF |

10

IDT723622/723632/723642 CMOS SyncBiFIFO

256 x 36 x 2, 512 x 36 x 2, 1,024 x 36 x 2

COMMERCIALTEMPERATURERANGE

— PARALLEL LOAD FROM PORT A

ToprogramtheX1,X2,Y1,andY2registersfromportA,bothFlFOsshould

be reset simultaneously with FS0 and FS1 LOW during the LOW-to-HIGH

transition of the Reset inputs. After this reset is complete, the first four writes to

FIFO1 do not store data in the FIFO memory but load the offset registers in the

order Y1, X1, Y2, X2. The port A data inputs used by the offset registers are

(A7-A0), (A8-A0), or (A9-A0) for the IDT723622, IDT723632, or IDT723642,

respectively. The highest numbered input is used as the most significant bit of

the binary number in each case. Valid programming values for the registers

ranges from 1 to 252 for the IDT723622; 1 to 508 for the IDT723632; and 1 to

1,020fortheIDT723642. Afteralltheoffsetregistersareprogrammedfromport

A, the port B Input Ready flag (IRB) is set HIGH, and both FIFOs begin normal

operation.SeeFigure3forrelevantoffsetregisterparallelprogrammingtiming

diagram.

FIFO WRITE/READ OPERATION

The state of the port A data (A0-A35) outputs is controlled by port A Chip

Select (

CSA) and port A Write/Read select (W/RA). The A0-A35 outputs are

in the high-impedance state when either

CSA or W/RA is HIGH. The A0-A35

outputs are active when both

CSA and W/RA are LOW.

Data is loaded into FIFO1 from the A0-A35 inputs on a LOW-to-HIGH

transition of CLKA when

CSA is LOW, W/RA is HIGH, ENA is HIGH , MBA is

LOW, and IRA is HIGH. Data is read from FIFO2 to the A0-A35 outputs by a

LOW-to-HIGH transition of CLKA when

CSA is LOW, W/RA is LOW, ENA is

HIGH, MBA is LOW, and ORA is HIGH (see Table 2). FIFO reads and writes

on port A are independent of any concurrent port B operation. Write and Read

cycle timing diagrams for port A can be found in Figure 4 and 7.

TheportBcontrolsignalsareidenticaltothoseofportAwiththeexception

thattheportBWrite/Readselect(

W/RB)istheinverseoftheportAWrite/Read

select(W/

RA).ThestateoftheportBdata(B0-B35)outputsiscontrolledbythe

port B Chip Select (

CSB) and port B Write/Read select (W/RB). The B0-B35

outputs are in the high-impedance state when either

CSB is HIGH orW/RBis

LOW. The B0-B35 outputs are active when

CSB is LOW and W/RB is HIGH.

Data is loaded into FIFO2 from the B0-B35 inputs on a LOW-to-HIGH

transitionofCLKBwhen

CSBisLOW,W/RBisLOW,ENBisHIGH,MBBisLOW,

and IRB is HIGH. Data is read from FIFO1 to the B0-B35 outputs by a LOW-

to-HIGH transition of CLKB when

CSB is LOW,W/RBisHIGH,ENBisHIGH,

MBB is LOW, and ORB is HIGH (see Table 3) . FIFO reads and writes on port

B are independent of any concurrent port A operation. Write and Read cycle

timing diagrams for port B can be found in Figure 5 and 6.

SIGNAL DESCRIPTION

RESET

After power up, a Master Reset operation must be performed by

providingaLOWpulseto

RSTIandRST2simultaneously. Afterwards,theFIFO

memories of the IDT723622/723632/723642 are reset separately by taking

their Reset (

RST1,RST2)inputsLOWforatleastfourportAClock(CLKA)and

fourportBClock(CLKB)LOW-to-HIGHtransitions.TheResetinputscanswitch

asynchronouslytotheclocks.AFIFOresetinitializestheinternalreadandwrite

pointers and forces the Input Ready flag (IRA, IRB) LOW, the Output Ready

flag(ORA,ORB)LOW,theAlmost-Emptyflag(

AEA,AEB)LOW,andtheAlmost-

Full flag (

AFA, AFB) HIGH. Resetting a FIFO also forces the Mailbox Flag

(

MBF1, MBF2) of the parallel mailbox register HIGH. After a FlFO is reset, its

Input Ready flag is set HIGH after two clock cycles to begin normal operation.

A LOW-to-HIGH transition on a FlFO Reset (

RST1, RST2)inputlatches

the value of the Flag Select (FS0, FS1) inputs for choosing the Almost-Full and

Almost-Empty offset programming method (for details see Table 1, Flag

Programming and the Almost-Empty Flag and Almost-Full Flag Offset

Programmingsectionthatfollows).TherelevantFIFOResettimingdiagramcan

be found in Figure 2.

ALMOST-EMPTY FLAG AND ALMOST-FULL FLAG OFFSET PRO-

GRAMMING

Four registers in these devices are used to hold the offset values for

the Almost-Empty and Almost-Full flags. The port B Almost-Empty flag (

AEB)

OffsetregisterislabeledX1andtheportAAlmost-Emptyflag(

AEA)Offsetregister

islabeledX2.TheportAAlmost-Fullflag(

AFA)OffsetregisterislabeledY1and

theportBAlmost-Fullflag(

AFB)OffsetregisterislabeledY2.Theindexofeach

register name corresponds to its FIFO number. The offset registers can be

loadedwithpresetvaluesduringtheresetofaFIFOortheycanbeprogrammed

from port A (see Table 1).

— PRESET VALUES

ToloadtheFIFO'sAlmost-EmptyflagandAlmost-FullflagOffsetregisters

withoneofthethreepresetvalueslistedinTable1,atleastoneoftheflagselect

inputs must be HIGH during the LOW-to-HIGH transition of its Reset input. For

example, to load the preset value of 64 into X1 and Y1, FS0 and FS1 must be

HIGHwhenFlFO1Reset(

RST1)returnsHIGH.Flagoffsetregistersassociated

withFIFO2areloadedwithoneofthepresetvaluesinthesamewaywithFIFO2

Reset (

RST2) toggled simultaneously with FIFO1 Reset (RST1). For preset

value loading timing diagram, see Figure 2.

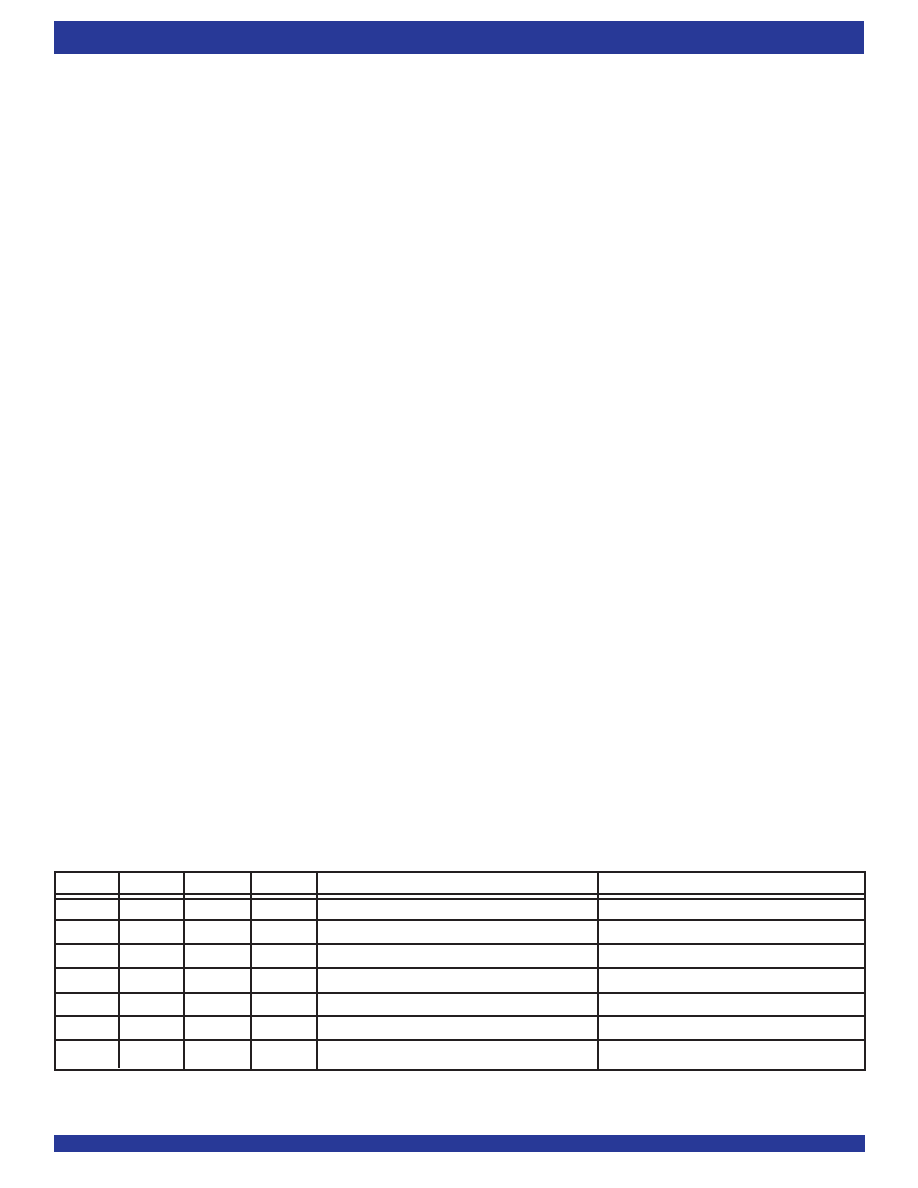

FS1

FS0

RST1

RST2

X1 AND Y1 REGlSTERS(1)

X2 AND Y2 REGlSTERS(2)

HH

↑

X64

X

HH

X

↑

X64

HL

↑

X16

X

HL

X

↑

X16

LH

↑

X8

X

LH

X

↑

X8

LL

↑↑

Programmed from port A

NOTES:

1. X1 register holds the offset for

AEB; Y1 register holds the offset for AFA.

2. X2 register holds the offset for

AEA; Y2 register holds the offset for AFB.

TABLE 1 — FLAG PROGRAMMING

相关PDF资料 |

PDF描述 |

|---|---|

| V150B24M250B3 | CONVERTER MOD DC/DC 24V 250W |

| VI-B6V-IV-F1 | CONVERTER MOD DC/DC 5.8V 150W |

| MS3100R22-19S | CONN RCPT 14POS WALL MNT W/SCKT |

| VI-B6T-IV-F4 | CONVERTER MOD DC/DC 6.5V 150W |

| VI-B6T-IV-F3 | CONVERTER MOD DC/DC 6.5V 150W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT723633L12PF | 功能描述:IC FIFO SYNC 512X36 128-TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:7200 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT723633L12PF8 | 功能描述:IC FIFO SYNC 512X36 128-TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:7200 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT723633L15PF | 功能描述:IC FIFO SYNC 512X36 128-TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:7200 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT723633L15PF8 | 功能描述:IC FIFO SYNC 512X36 128-TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:7200 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT723634L12PF | 功能描述:IC FIFO SYNC 512X36X2 128QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:7200 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

发布紧急采购,3分钟左右您将得到回复。