- 您现在的位置:买卖IC网 > PDF目录9944 > IDT723642L15PF8 (IDT, Integrated Device Technology Inc)IC FIFO SYNC 2048X36 120QFP PDF资料下载

参数资料

| 型号: | IDT723642L15PF8 |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 4/25页 |

| 文件大小: | 0K |

| 描述: | IC FIFO SYNC 2048X36 120QFP |

| 标准包装: | 750 |

| 系列: | 7200 |

| 功能: | 同步 |

| 存储容量: | 72K(2K x 36) |

| 数据速率: | 67MHz |

| 访问时间: | 15ns |

| 电源电压: | 4.5 V ~ 5.5 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 120-LQFP |

| 供应商设备封装: | 120-TQFP(14x14) |

| 包装: | 带卷 (TR) |

| 其它名称: | 723642L15PF8 |

12

IDT723622/723632/723642 CMOS SyncBiFIFO

256 x 36 x 2, 512 x 36 x 2, 1,024 x 36 x 2

COMMERCIALTEMPERATURERANGE

almost-emptystateisdefinedbythecontentsofregisterX1for

AEBandregister

X2 for

AEA.TheseregistersareloadedwithpresetvaluesduringaFIFOreset

or programmed from port A (see Almost-Empty flag and Almost-Full flag offset

programming section). An Almost-Empty flag is LOW when its FIFO contains

X or less words and is HIGH when its FIFO contains (X+1) or more words. A

data word present in the FIFO output register has been read from memory.

Two LOW-to-HIGH transitions of the Almost-Empty flag synchronizing

clock are required after a FIFO write for its Almost-Empty flag to reflect the new

level of fill. Therefore, the Almost-Full flag of a FIFO containing (X+1) or more

words remains LOW if two cycles of its synchronizing clock have not elapsed

since the write that filled the memory to the (X+1) level. An Almost-Empty flag

issetHIGHbythesecondLOW-to-HIGHtransitionofitssynchronizingclockafter

the FIFO write that fills memory to the (X+1) level. A LOW-to-HIGH transition of

anAlmost-Emptyflagsynchronizingclockbeginsthefirstsynchronizationcycle

ifitoccursattimetSKEW2orgreaterafterthewritethatfillstheFIFOto(X+1)words.

Otherwise,thesubsequentsynchronizingclockcyclemaybethefirstsynchro-

nization cycle. (See Figures 12 and 13).

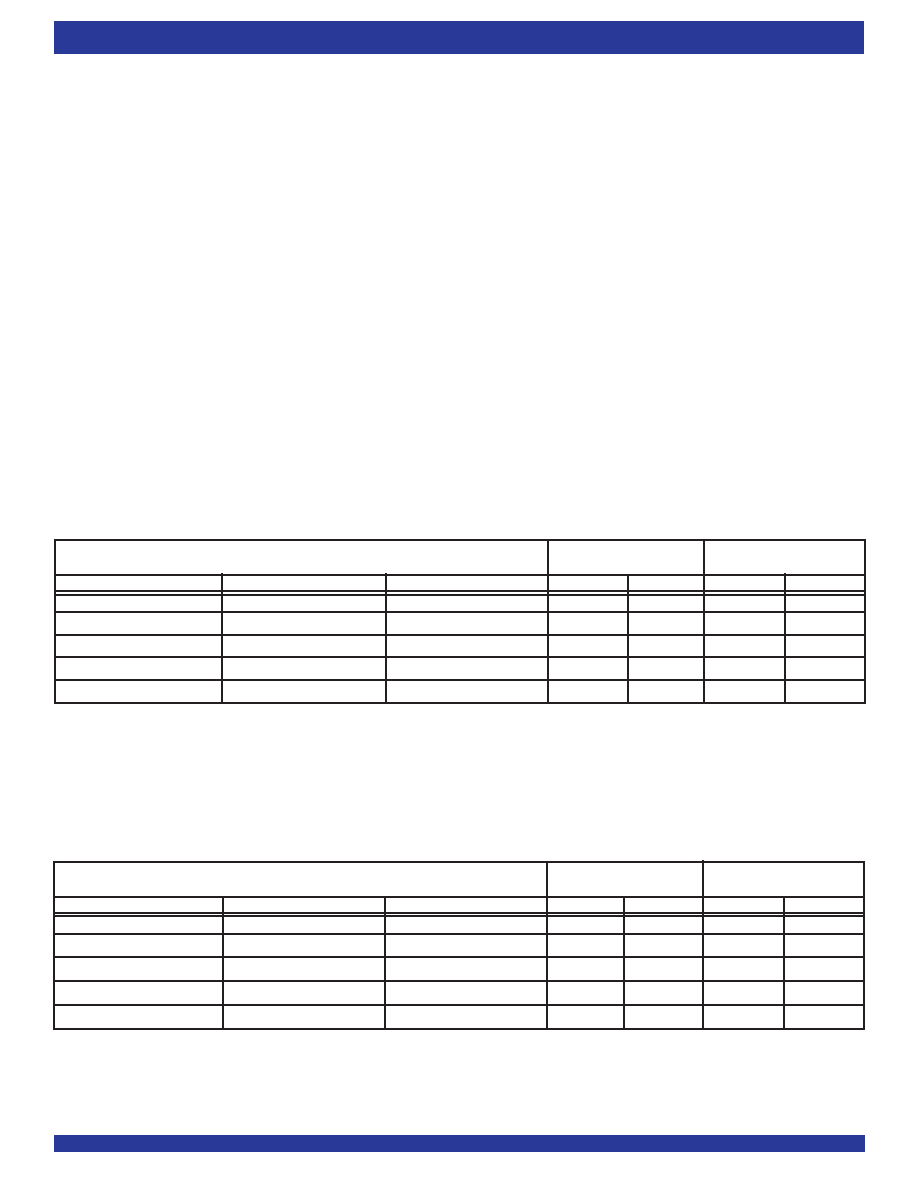

Synchronized

Number of Words in FIFO(1,2)

to CLKB

to CLKA

IDT723622(3)

IDT723632(3)

IDT723642(3)

ORB

AEB

AFA

IRA

000

L

H

1 to X1

H

L

H

(X1+1) to [256-(Y1+1)]

(X1+1) to [512-(Y1+1)]

(X1+1) to [1,024-(Y1+1)]

H

(256-Y1) to 255

(512-Y1) to 511

(1,024-Y1) to 1,023

H

L

H

256

512

1,024

H

L

full-2. From the time a word is read from a FIFO, its previous memory location

is ready to be written in a minimum of two cycles of the Input Ready flag

synchronizing clock. Therefore, an Input Ready flag is LOW if less than two

cycles of the Input Ready flag synchronizing clock have elapsed since the next

memory write location has been read. The second LOW-to-HIGH transition on

the Input Ready flag synchronizing Clock after the read sets the Input Ready

flag HIGH.

A LOW-to-HIGH transition on an Input Ready flag synchronizing clock

begins the first synchronization cycle of a read if the clock transition occurs at

timetSKEW1orgreateraftertheread.Otherwise,thesubsequentclockcyclecan

be the first synchronization cycle (see Figures 10 and 11 for timing diagrams).

ALMOST-EMPTY FLAGS (

AEA, AEB)

TheAlmost-EmptyflagofaFIFOissynchronizedtotheportclockthatreads

datafromitsarray.ThestatemachinethatcontrolsanAlmost-Emptyflagmonitors

a write pointer and read pointer comparator that indicates when the FIFO

memory status is almost-empty, almost-empty+1, or almost-empty+2. The

NOTES:

1. When a word loaded to an empty FIFO is shifted to the output register, its previous FIFO memory location is free.

2. Data in the output register does not count as a "word in FIFO memory". Since the first word written to an empty FIFO goes unrequested to the output register (no read

operation necessary), it is not included in the FIFO memory count.

3. X1 is the Almost-Empty offset for FIFO1 used by

AEB. Y1 is the Almost-Full offset for FIFO1 used by AFA. Both X1 and Y1 are selected during a reset of FIFO1 or

programmed from port A.

Synchronized

Number of Words in FIFO(1,2)

to CLKA

to CLKB

IDT723622(3)

IDT723632(3)

IDT723642(3)

ORA

AEA

AFB

IRB

000

L

H

1 to X2

H

L

H

(X2+1) to [256-(Y2+1)]

(X2+1) to [512-(Y2+1)]

(X2+1) to [1,024-(Y2+1)]

H

(256-Y2) to 255

(512-Y2) to 511

(1,024-Y2) to 1,023

H

L

H

256

512

1,024

H

L

NOTES:

1. When a word loaded to an empty FIFO is shifted to the output register, its previous FIFO memory location is free.

2. Data in the output register does not count as a "word in FIFO memory". Since the first word written to an empty FIFO goes unrequested to the output register (no read

operation necessary), it is not included in the FIFO memory count.

3. X2 is the Almost-Empty offset for FIFO2 used by

AEA. Y2 is the Almost-Full offset for FIFO2 used by AFB. Both X2 and Y2 are selected during a reset of FIFO2 or

programmed from port A.

TABLE 4 — FIFO1 FLAG OPERATION

TABLE 5 — FIFO2 FLAG OPERATION

相关PDF资料 |

PDF描述 |

|---|---|

| MAX1026BEEE+T | IC ADC 10BIT 300KSPS 16-QSOP |

| IDT72V3672L10PF8 | IC FIFO 16384X36 10NS 120QFP |

| MCZ33897TEFR2 | IC TXRX SGL WIRE CAN 14-SOIC |

| IDT72V283L7-5PF8 | IC FIFO 32768X18 7-5NS 80QFP |

| MS27466T15A35PA | CONN RCPT 37POS WALL MNT W/PINS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT723642L15PFG | 制造商:Integrated Device Technology Inc 功能描述:IC FIFO SYNC 256X36X2 120TQFP |

| IDT723642L15PFG8 | 制造商:Integrated Device Technology Inc 功能描述:IC FIFO SYNC 256X36X2 120TQFP |

| IDT723642L15PQF | 功能描述:IC FIFO SYNC 2048X36 132QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:7200 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT723642L15PQFGI | 功能描述:IC FIFO SYNC 2048X36 132QFP RoHS:是 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:7200 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT723643L12PF | 功能描述:IC FIFO SYNC 1024X36 128QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:7200 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

发布紧急采购,3分钟左右您将得到回复。