- 您现在的位置:买卖IC网 > PDF目录299201 > IDT72V2105L15PFI (INTEGRATED DEVICE TECHNOLOGY INC) 3.3 VOLT HIGH DENSITY CMOS SUPERSYNC FIFO 131,072 x 18 262,144 x 18 PDF资料下载

参数资料

| 型号: | IDT72V2105L15PFI |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | FIFO |

| 英文描述: | 3.3 VOLT HIGH DENSITY CMOS SUPERSYNC FIFO 131,072 x 18 262,144 x 18 |

| 中文描述: | 256K X 18 OTHER FIFO, 10 ns, PQFP64 |

| 封装: | PLASTIC, TQFP-64 |

| 文件页数: | 12/26页 |

| 文件大小: | 294K |

| 代理商: | IDT72V2105L15PFI |

2

COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES

IDT72V295/72V2105 3.3V HIGH DENSITY CMOS

SUPERSYNC FIFOTM 131,072 x 18, 262,144 x 18

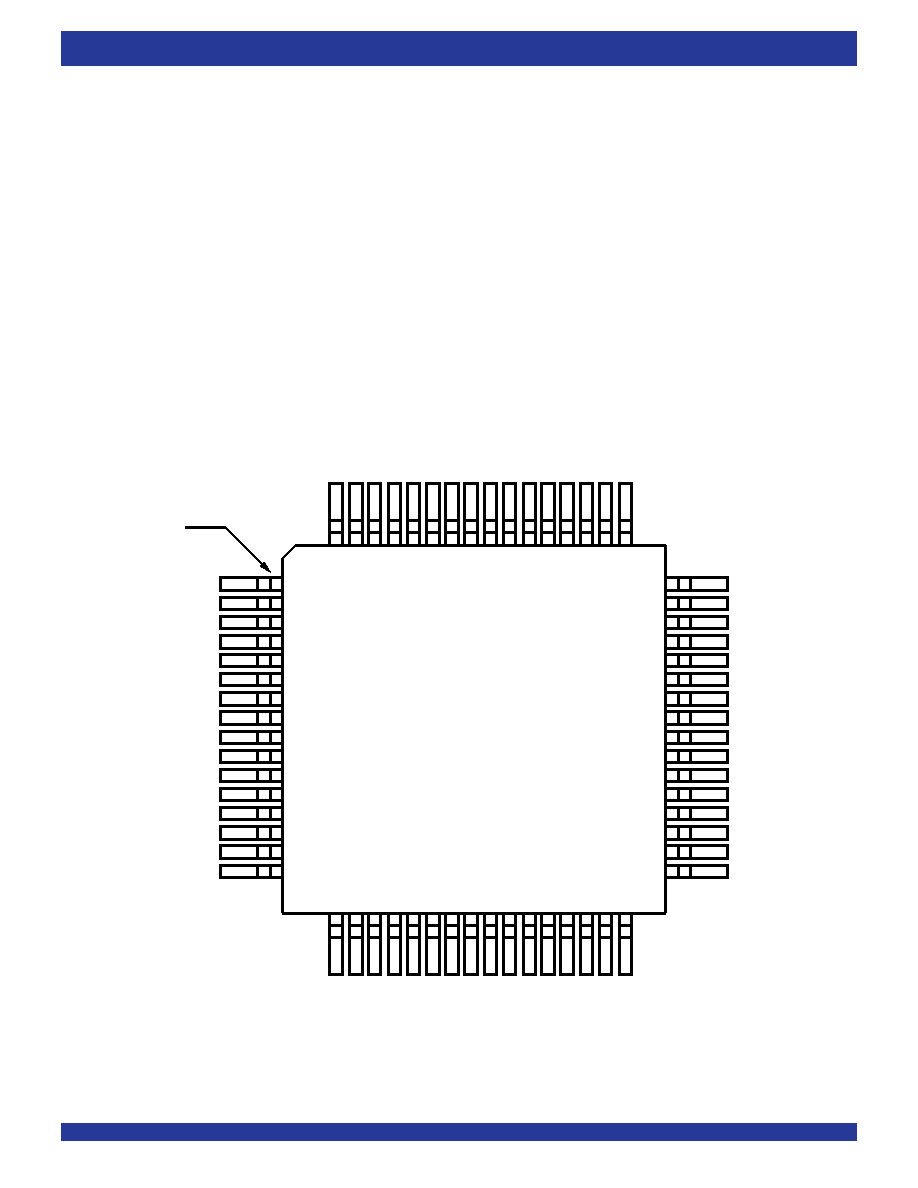

PIN CONFIGURATIONS

TQFP (PN64-1, order code: PF)

TOP VIEW

DESCRIPTION (CONTINUED)

thus it is no longer necessary to select which of the two clock inputs,

RCLK or WCLK, is running at the higher frequency.

The period required by the retransmit operation is now fixed and short.

The first word data latency period, from the time the first word is written

to an empty FIFO to the time it can be read, is now fixed and short. (The

variable clock cycle counting delay associated with the latency period

found on previous SuperSync devices has been eliminated on this

SuperSync family.)

SuperSync FIFOs are particularly appropriate for network, video, telecom-

munications, data communications and other applications that need to

buffer large amounts of data.

The input port is controlled by a Write Clock (WCLK) input and a Write

Enable (

WEN) input. Data is written into the FIFO on every rising edge of

WCLK when

WENis asserted. The output port is controlled by a Read Clock

(RCLK) input and Read Enable (

REN) input. Data is read from the FIFO on

every rising edge of RCLK when

REN is asserted. An Output Enable (OE)

input is provided for three-state control of the outputs.

The frequencies of both the RCLK and the WCLK signals may vary from

0 to fMAX with complete independence. There are no restrictions on the

frequency of the one clock input with respect to the other.

There are two possible timing modes of operation with these devices:

IDT Standard mode and First Word Fall Through (FWFT) mode.

NOTE:

1. DC = Don’t Care. Must be tied to GND or VCC, cannot be left open.

PIN 1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

WEN

SEN

DC(1)

VCC

GND

D17

D16

D15

D14

D13

D12

D11

D10

D9

D8

D7

64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49

17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32

Q17

Q16

GND

Q15

Q14

VCC

Q13

Q12

Q11

GND

Q10

Q9

Q8

Q7

Q6

GND

WCLK

PRS

MRS

LD

FWFT/SI

GND

FF

/IR

PAF

HF

V

CC

PAE

EF

/OR

RCLK

REN

RT

OE

Q5

Q4

V

CC

Q3

Q2

GND

Q1

Q0

GND

D0

D1

D2

D3

D4

D5

D6

4668 drw 02

相关PDF资料 |

PDF描述 |

|---|---|

| IDT72V36100L15PFI | 3.3 VOLT HIGH-DENSITY SUPERSYNC II⑩ 36-BIT FIFO |

| IDT72V36100L6BB | 3.3 VOLT HIGH-DENSITY SUPERSYNC II⑩ 36-BIT FIFO |

| IDT72V36100L6PF | 3.3 VOLT HIGH-DENSITY SUPERSYNC II⑩ 36-BIT FIFO |

| IDT72V36100L7.5PF | 3.3 VOLT HIGH-DENSITY SUPERSYNC II⑩ 36-BIT FIFO |

| IDT72V36102L10PF | 3.3 VOLT CMOS SyncBiFIFO-TM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT72V2105L15PFI8 | 功能描述:IC FIFO SUPERSYNCII 15NS 64-TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72V2105L20PF | 功能描述:IC FIFO SUPERSYNCII 20NS 64-TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:74ABT 功能:同步,双端口 存储容量:4.6K(64 x 36 x2) 数据速率:67MHz 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:120-LQFP 裸露焊盘 供应商设备封装:120-HLQFP(14x14) 包装:托盘 产品目录页面:1005 (CN2011-ZH PDF) 其它名称:296-3984 |

| IDT72V2105L20PF8 | 功能描述:IC FIFO SUPERSYNCII 20NS 64-TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72V2111L10PF | 功能描述:IC FIFO SS 512X9 10NS 64QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72V2111L10PF8 | 功能描述:IC FIFO SS 512X9 10NS 64QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

发布紧急采购,3分钟左右您将得到回复。