- 您现在的位置:买卖IC网 > PDF目录299201 > IDT72V2105L15PFI (INTEGRATED DEVICE TECHNOLOGY INC) 3.3 VOLT HIGH DENSITY CMOS SUPERSYNC FIFO 131,072 x 18 262,144 x 18 PDF资料下载

参数资料

| 型号: | IDT72V2105L15PFI |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | FIFO |

| 英文描述: | 3.3 VOLT HIGH DENSITY CMOS SUPERSYNC FIFO 131,072 x 18 262,144 x 18 |

| 中文描述: | 256K X 18 OTHER FIFO, 10 ns, PQFP64 |

| 封装: | PLASTIC, TQFP-64 |

| 文件页数: | 26/26页 |

| 文件大小: | 294K |

| 代理商: | IDT72V2105L15PFI |

9

COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES

IDT72V295/72V2105 3.3V HIGH DENSITY CMOS

SUPERSYNC FIFOTM 131,072 x 18, 262,144 x 18

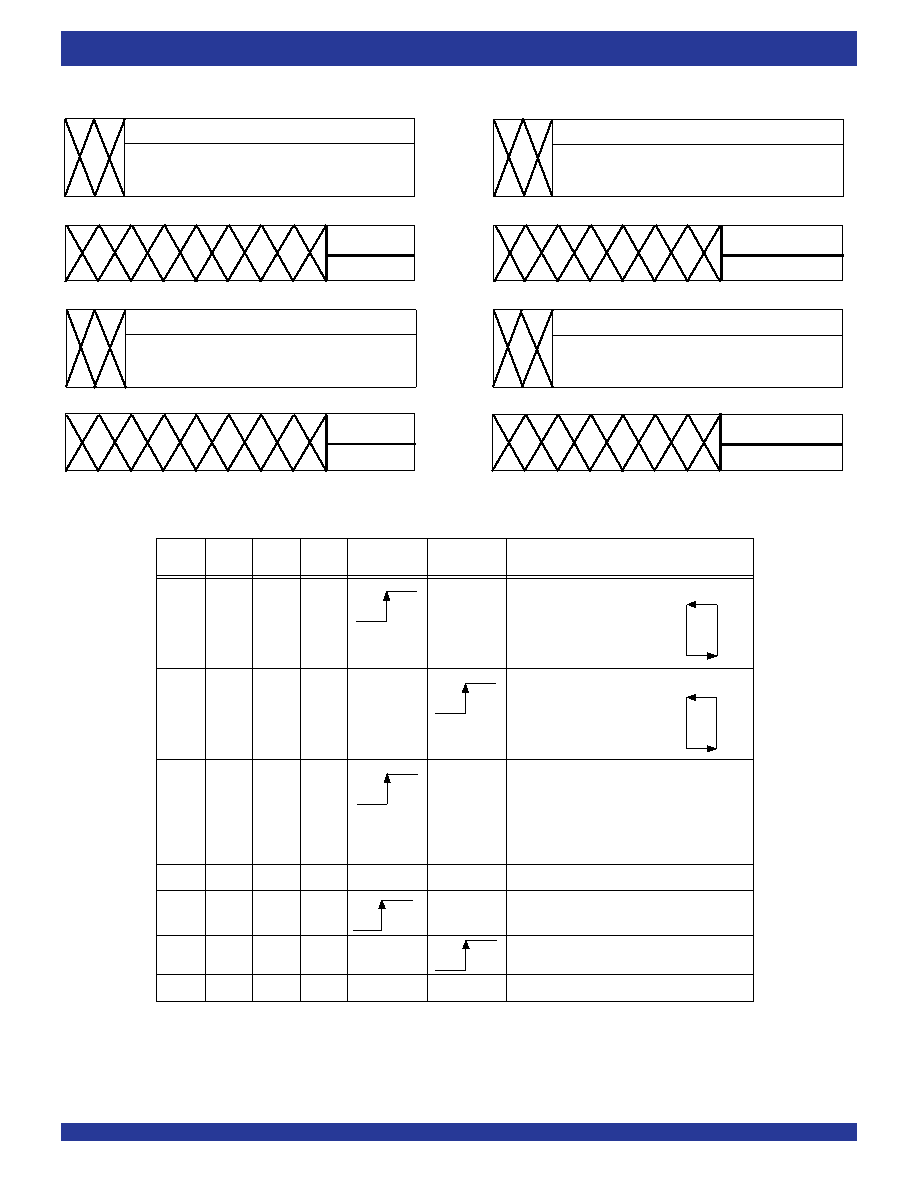

Figure 4. Programmable Flag Offset Programming Sequence

Figure 3. Offset Register Location and Default Values

17

0

007FH if

LD is LOW at Master Reset,

03FFH if

LD is HIGH at Master Reset

DEFAULT VALUE

FULL OFFSET (LSB) REGISTER

17

0

DEFAULT VALUE

007FH if

LD is LOW at Master Reset,

03FFH if

LD is HIGH at Master Reset

15

IDT72V295 (131,072 x 18-BIT)

16

15

16

EMPTY OFFSET (LSB) REGISTER

17

0

007FH if

LD is LOW at Master Reset,

03FFH if

LD is HIGH at Master Reset

FULL OFFSET (LSB) REGISTER

17

0

DEFAULT VALUE

007FH if

LD is LOW at Master Reset,

03FFH if

LD is HIGH at Master Reset

15

IDT72V2105 (262,144 x 18-BIT)

16

15

16

EMPTY OFFSET (LSB) REGISTER

17

DEFAULT

0H

0

1

17

0

21

17

0

21

17

0

1

EMPTY OFFSET

(MSB) REGISTER

DEFAULT

0H

FULL OFFSET

(MSB) REGISTER

DEFAULT

0H

EMPTY OFFSET

(MSB) REGISTER

DEFAULT

0H

FULL OFFSET

(MSB) REGISTER

4668 drw 06

WCLK

RCLK

X

XX

X

XX

4668 drw 07

LD

0

X

1

0

WEN

0

1

0

X

1

REN

1

0

1

X

0

1

X

SEN

1

X

0

No Operation

Write Memory

Read Memory

No Operation

Parallel write to registers:

Empty Offset (LSB)

Empty Offset (MSB)

Full Offset (LSB)

Full Offset (MSB)

Serial shift into registers:

34 bits for the 72V295

36 bits for the 72V2105

1 bit for each rising WCLK edge

Starting with Empty Offset (LSB)

Ending with Full Offset (MSB)

IDT72V295

IDT72V2105

Parallel read from registers:

Empty Offset (LSB)

Empty Offset (MSB)

Full Offset (LSB)

Full Offset (MSB)

NOTES:

1. The programming method can only be selected at Master Reset.

2. Parallel reading of the offset registers is always permitted regardless of which programming method has been selected.

3. The programming sequence applies to both IDT Standard and FWFT modes.

相关PDF资料 |

PDF描述 |

|---|---|

| IDT72V36100L15PFI | 3.3 VOLT HIGH-DENSITY SUPERSYNC II⑩ 36-BIT FIFO |

| IDT72V36100L6BB | 3.3 VOLT HIGH-DENSITY SUPERSYNC II⑩ 36-BIT FIFO |

| IDT72V36100L6PF | 3.3 VOLT HIGH-DENSITY SUPERSYNC II⑩ 36-BIT FIFO |

| IDT72V36100L7.5PF | 3.3 VOLT HIGH-DENSITY SUPERSYNC II⑩ 36-BIT FIFO |

| IDT72V36102L10PF | 3.3 VOLT CMOS SyncBiFIFO-TM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT72V2105L15PFI8 | 功能描述:IC FIFO SUPERSYNCII 15NS 64-TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72V2105L20PF | 功能描述:IC FIFO SUPERSYNCII 20NS 64-TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:74ABT 功能:同步,双端口 存储容量:4.6K(64 x 36 x2) 数据速率:67MHz 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:120-LQFP 裸露焊盘 供应商设备封装:120-HLQFP(14x14) 包装:托盘 产品目录页面:1005 (CN2011-ZH PDF) 其它名称:296-3984 |

| IDT72V2105L20PF8 | 功能描述:IC FIFO SUPERSYNCII 20NS 64-TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72V2111L10PF | 功能描述:IC FIFO SS 512X9 10NS 64QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72V2111L10PF8 | 功能描述:IC FIFO SS 512X9 10NS 64QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

发布紧急采购,3分钟左右您将得到回复。