- 您现在的位置:买卖IC网 > PDF目录9893 > IDT72V36110L7-5BBGI (IDT, Integrated Device Technology Inc)IC FIFO 131KX36 7-5NS 144BGA PDF资料下载

参数资料

| 型号: | IDT72V36110L7-5BBGI |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 37/48页 |

| 文件大小: | 0K |

| 描述: | IC FIFO 131KX36 7-5NS 144BGA |

| 标准包装: | 1 |

| 系列: | 72V |

| 功能: | 同步 |

| 存储容量: | 4.7M(131K x 36) |

| 数据速率: | 166MHz |

| 访问时间: | 5ns |

| 电源电压: | 3.15 V ~ 3.45 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 144-BGA |

| 供应商设备封装: | 144-PBGA(13x13) |

| 包装: | 托盘 |

| 其它名称: | 72V36110L7-5BBGI |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页当前第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

42

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

IDT72V36100/72V36110 3.3V HIGH DENSITY SUPERSYNC IITM 36-BIT FIFO

65,536 x 36 and 131,072 x 36

OCTOBER 22, 2008

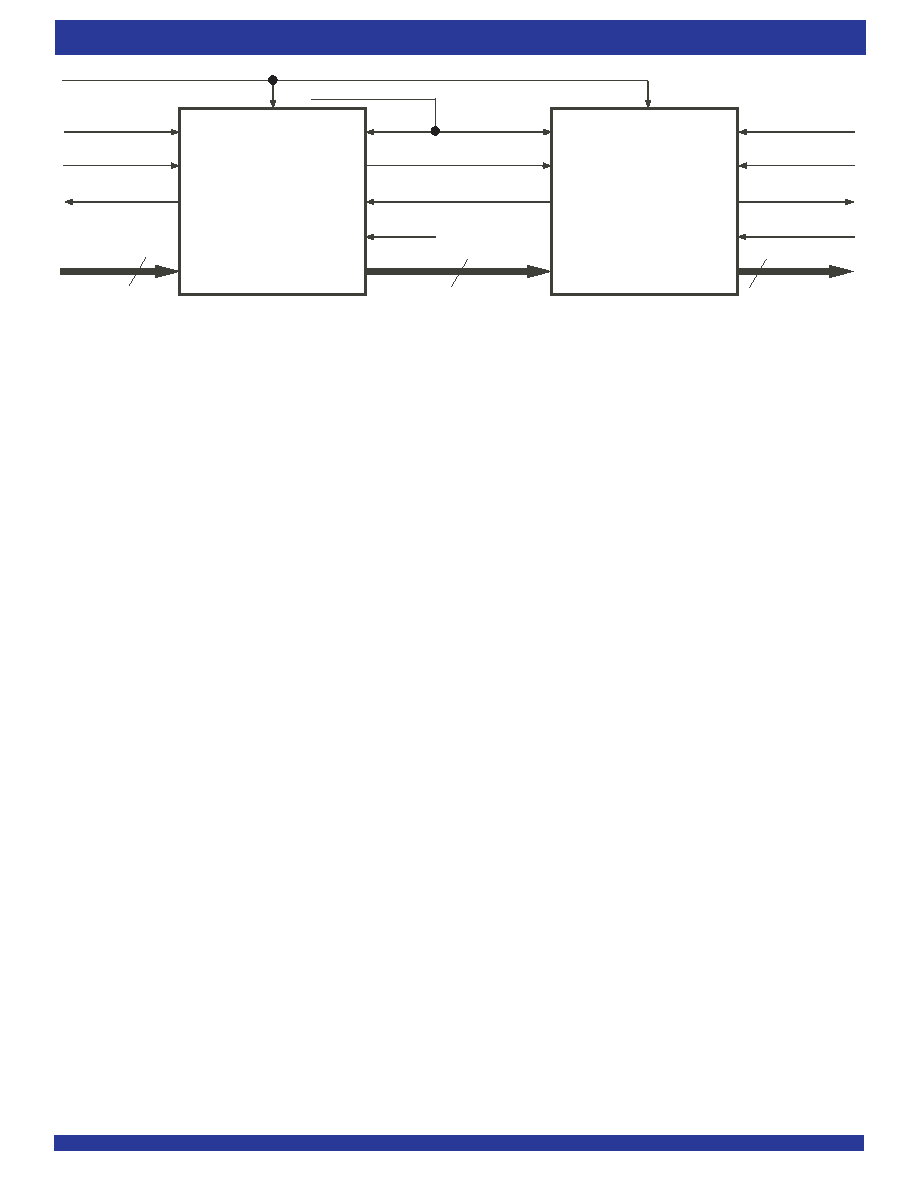

Figure 30. Block Diagram of 131,072 x 36 and 262,144 x 36 Depth Expansion

DEPTH EXPANSION CONFIGURATION (FWFT MODE ONLY)

The IDT72V36100 can easily be adapted to applications requiring depths

greaterthan65,536and131,072fortheIDT72V36110,withan36-bitbuswidth.

In FWFT mode, the FIFOs can be connected in series (the data outputs of one

FIFOconnectedtothedatainputsofthenext)withnoexternallogicnecessary.

The resulting configuration provides a total depth equivalent to the sum of the

depths associated with each single FIFO. Figure 30 shows a depth expansion

using two IDT72V36100/72V36110 devices.

CareshouldbetakentoselectFWFTmodeduringMasterResetforallFIFOs

in the depth expansion configuration. The first word written to an empty

configuration will pass from one FIFO to the next ("ripple down") until it finally

appears at the outputs of the last FIFO in the chain – no read operation is

necessarybuttheRCLKofeachFIFOmustbefree-running. Eachtimethedata

word appears at the outputs of one FIFO, that device's

OR line goes LOW,

enabling a write to the next FIFO in line.

For an empty expansion configuration, the amount of time it takes for

ORof

the last FIFO in the chain to go LOW (i.e. valid data to appear on the last FIFO's

outputs) after a word has been written to the first FIFO is the sum of the delays

for each individual FIFO:

(N – 1)*(4*transfer clock) + 3*TRCLK

whereNisthenumberofFIFOsintheexpansionandTRCLKistheRCLKperiod.

Note that extra cycles should be added for the possibility that the tSKEW1

specificationisnotmetbetweenWCLKandtransferclock,orRCLKandtransfer

clock, for the

OR flag.

The"rippledown"delayisonlynoticeableforthefirstwordwrittentoanempty

depth expansion configuration. There will be no delay evident for subsequent

words written to the configuration.

The first free location created by reading from a full depth expansion

configurationwill"bubbleup"fromthelastFIFOtothepreviousoneuntilitfinally

movesintothefirstFIFOofthechain. Eachtimeafreelocationiscreatedinone

FIFO of the chain, that FIFO's

IRlinegoesLOW,enablingtheprecedingFIFO

to write a word to fill it.

Forafullexpansionconfiguration,theamountoftimeittakesfor

IRofthefirst

FIFO in the chain to go LOW after a word has been read from the last FIFO is

the sum of the delays for each individual FIFO:

(N – 1)*(3*transfer clock) + 2 TWCLK

where N is the number of FIFOs in the expansion and TWCLK is the WCLK

period. NotethatextracyclesshouldbeaddedforthepossibilitythatthetSKEW1

specificationisnotmetbetweenRCLKandtransferclock,orWCLKandtransfer

clock, for the

IR flag.

The Transfer Clock line should be tied to either WCLK or RCLK, whichever

isfaster. Boththeseactionsresultindatamoving,asquicklyaspossible,tothe

end of the chain and free locations to the beginning of the chain.

Dn

INPUT READY

WRITE ENABLE

WRITE CLOCK

WEN

WCLK

IR

DATA IN

RCLK

READ CLOCK

RCLK

REN

OE

OUTPUT ENABLE

OUTPUT READY

Qn

Dn

IR

GND

WEN

WCLK

OR

REN

OE

Qn

READ ENABLE

OR

DATA OUT

IDT

72V36100

72V36110

TRANSFER CLOCK

6117 drw35

n

FWFT/SI

IDT

72V36100

72V36110

相关PDF资料 |

PDF描述 |

|---|---|

| MAX1293ACEG+T | IC ADC 12BIT 250KSPS 24-QSOP |

| ISL32273EFVZ | IC RCVR RS485/422 QD ESD 16TSSOP |

| MAX184BCWG+T | IC ADC 12BIT HS 24-SOIC |

| ISL32179EFRZ | IC XMITTER ESD RS422 LP 24-QFN |

| MAX1264ACEG+T | IC ADC 12BIT 400KSPS 24-QSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT72V36110L7-5BBGI8 | 功能描述:IC FIFO 131KX36 7-5NS 144BGA RoHS:是 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72V36110L7-5BBI | 功能描述:IC FIFO 131KX36 7-5NS 144BGA RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:74ABT 功能:同步,双端口 存储容量:4.6K(64 x 36 x2) 数据速率:67MHz 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:120-LQFP 裸露焊盘 供应商设备封装:120-HLQFP(14x14) 包装:托盘 产品目录页面:1005 (CN2011-ZH PDF) 其它名称:296-3984 |

| IDT72V36110L7-5PF | 功能描述:IC FIFO 131KX36 7-5NS 128QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72V36110L7-5PF8 | 功能描述:IC FIFO 131KX36 7-5NS 128QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72V36110L7-5PFGI | 功能描述:3.3V SUPERSYNC II 36BIT FIFO RoHS:是 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:74ABT 功能:同步,双端口 存储容量:4.6K(64 x 36 x2) 数据速率:67MHz 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:120-LQFP 裸露焊盘 供应商设备封装:120-HLQFP(14x14) 包装:托盘 产品目录页面:1005 (CN2011-ZH PDF) 其它名称:296-3984 |

发布紧急采购,3分钟左右您将得到回复。