- 您现在的位置:买卖IC网 > PDF目录9893 > IDT72V36110L7-5BBGI (IDT, Integrated Device Technology Inc)IC FIFO 131KX36 7-5NS 144BGA PDF资料下载

参数资料

| 型号: | IDT72V36110L7-5BBGI |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 39/48页 |

| 文件大小: | 0K |

| 描述: | IC FIFO 131KX36 7-5NS 144BGA |

| 标准包装: | 1 |

| 系列: | 72V |

| 功能: | 同步 |

| 存储容量: | 4.7M(131K x 36) |

| 数据速率: | 166MHz |

| 访问时间: | 5ns |

| 电源电压: | 3.15 V ~ 3.45 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 144-BGA |

| 供应商设备封装: | 144-PBGA(13x13) |

| 包装: | 托盘 |

| 其它名称: | 72V36110L7-5BBGI |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页当前第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

44

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

IDT72V36100/72V36110 3.3V HIGH DENSITY SUPERSYNC IITM 36-BIT FIFO

65,536 x 36 and 131,072 x 36

OCTOBER 22, 2008

JTAG INTERFACE

Five additional pins (TDI, TDO, TMS, TCK and

TRST) are provided to

support the JTAG boundary scan interface. The IDT72V36100/72V36110

incorporates the necessary tap controller and modified pad cells to implement

the JTAG facility.

Note that IDT provides appropriate Boundary Scan Description Language

program files for these devices.

The Standard JTAG interface consists of four basic elements:

Test Access Port (TAP)

TAP controller

Instruction Register (IR)

Data Register Port (DR)

The following sections provide a brief description of each element. For a

completedescriptionrefertotheIEEEStandardTestAccessPortSpecification

(IEEE Std. 1149.1-1990).

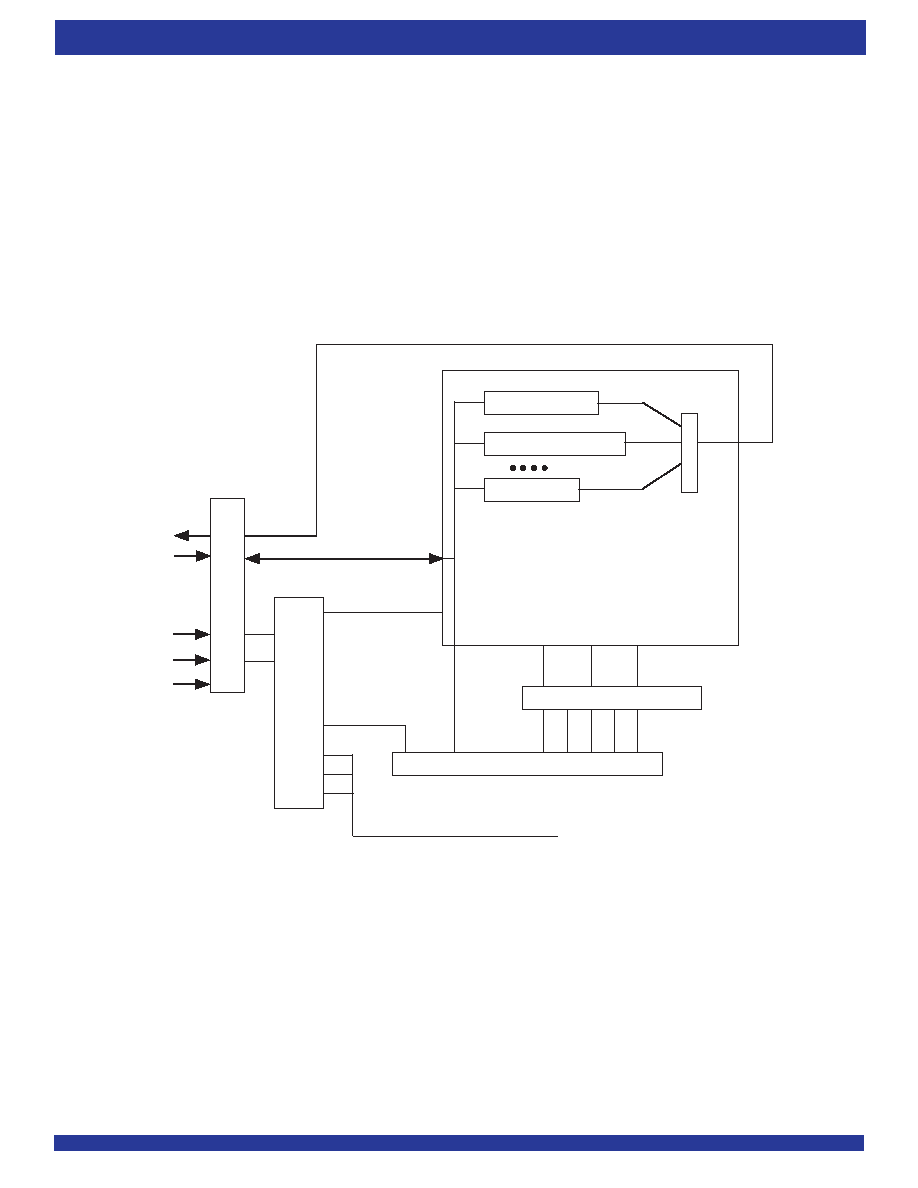

The Figure below shows the standard Boundary-Scan Architecture

Figure 32. Boundary Scan Architecture

TEST ACCESS PORT (TAP)

The Tap interface is a general-purpose port that provides access to the

internaloftheprocessor. Itconsistsoffourinputports(TCLK,TMS,TDI,

TRST)

and one output port (TDO).

THE TAP CONTROLLER

The Tap controller is a synchronous finite state machine that responds to

TMS and TCLK signals to generate clock and control signals to the Instruction

and Data Registers for capture and update of data.

T

A

P

TAP

Cont-

roller

Mux

DeviceID Reg.

Boundary Scan Reg.

Bypass Reg.

clkDR, ShiftDR

UpdateDR

TDO

TDI

TMS

TCLK

TRST

clklR, ShiftlR

UpdatelR

Instruction Register

Instruction Decode

Control Signals

6117 drw37

相关PDF资料 |

PDF描述 |

|---|---|

| MAX1293ACEG+T | IC ADC 12BIT 250KSPS 24-QSOP |

| ISL32273EFVZ | IC RCVR RS485/422 QD ESD 16TSSOP |

| MAX184BCWG+T | IC ADC 12BIT HS 24-SOIC |

| ISL32179EFRZ | IC XMITTER ESD RS422 LP 24-QFN |

| MAX1264ACEG+T | IC ADC 12BIT 400KSPS 24-QSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT72V36110L7-5BBGI8 | 功能描述:IC FIFO 131KX36 7-5NS 144BGA RoHS:是 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72V36110L7-5BBI | 功能描述:IC FIFO 131KX36 7-5NS 144BGA RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:74ABT 功能:同步,双端口 存储容量:4.6K(64 x 36 x2) 数据速率:67MHz 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:120-LQFP 裸露焊盘 供应商设备封装:120-HLQFP(14x14) 包装:托盘 产品目录页面:1005 (CN2011-ZH PDF) 其它名称:296-3984 |

| IDT72V36110L7-5PF | 功能描述:IC FIFO 131KX36 7-5NS 128QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72V36110L7-5PF8 | 功能描述:IC FIFO 131KX36 7-5NS 128QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72V36110L7-5PFGI | 功能描述:3.3V SUPERSYNC II 36BIT FIFO RoHS:是 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:74ABT 功能:同步,双端口 存储容量:4.6K(64 x 36 x2) 数据速率:67MHz 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:120-LQFP 裸露焊盘 供应商设备封装:120-HLQFP(14x14) 包装:托盘 产品目录页面:1005 (CN2011-ZH PDF) 其它名称:296-3984 |

发布紧急采购,3分钟左右您将得到回复。