- 您现在的位置:买卖IC网 > PDF目录10031 > IDT72V3613L15PF8 (IDT, Integrated Device Technology Inc)IC FIFO CLOCK 64X36 15NS 120TQFP PDF资料下载

参数资料

| 型号: | IDT72V3613L15PF8 |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 20/25页 |

| 文件大小: | 0K |

| 描述: | IC FIFO CLOCK 64X36 15NS 120TQFP |

| 标准包装: | 750 |

| 系列: | 72V |

| 功能: | 同步 |

| 存储容量: | 2.3K(64 x 36) |

| 数据速率: | 67MHz |

| 访问时间: | 15ns |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 120-LQFP |

| 供应商设备封装: | 120-TQFP(14x14) |

| 包装: | 带卷 (TR) |

| 其它名称: | 72V3613L15PF8 |

4

IDT72V3613 3.3V, CMOS CLOCKED FIFO WITH

BUS-MATCHING AND BYTE SWAPPING 64 x 36

COMMERCIALTEMPERATURERANGE

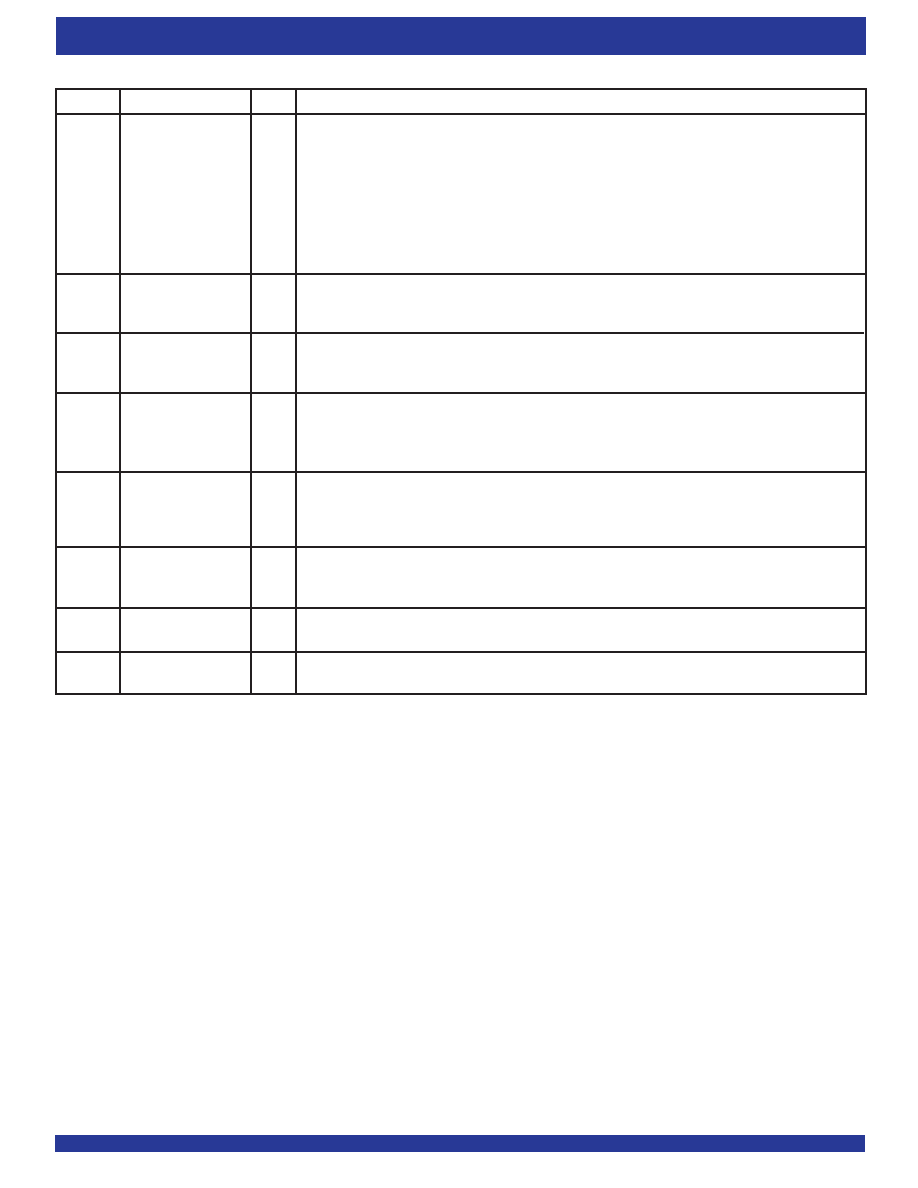

PIN DESCRIPTION (CONTINUED)

Symbol

Name

I/O

Description

PEFB

Port B Parity Error

O

When any valid byte applied to terminals B0-B35 fails parity, PEFB is LOW. Bytes are organized as

Flag

(PortB) B0-B8, B9-B17, B-18-B26, and B27-B35, with the most significant bit of each byte serving as the parity

bit. A byte is valid when it is used by the bus size selected for port B. The type of parity checked is

determined by the state of the ODD/EVEN input.

The parity trees used to check the B0-B35 inputs are shared by the mail1 register to generate parity if

parity generation is selected by PGB. Therefore, if a mail1 read with parity generation is set up by having

CSB LOW, ENB HIGH, W/RB LOW, SIZ1 and SIZ0 HIGH and PGB HIGH, the PEFB flag is forced HIGH

regardless of the state of the B0-B35 inputs.

PGA

Port A Parity

I

Parity is generated for data reads from the mail2 register when PGA is HIGH. The type of parity

Generation

generated is selected by the state of the ODD/EVEN input. Bytes are organized at A0-A8, A9-A17, A18-

A26, and A27-A35. The generated parity bits are output in the most significant bit of each byte.

PGB

Port B Parity

I

Parity is generated for data reads from port B when PGB is HIGH. The type of parity generated is

Generation

selected by the state of the ODD/EVEN input. Bytes are organized as B0-B8, B9-B17, B18-B26, and

B27-B35. The generated parity bits are output in the most significant bit of each byte.

RST

Reset

I

To reset the device, four LOW-to-HIGH transitions of CLKA and four LOW-to-HIGH transitions of CLKB

must occur while RST is LOW. This sets the AF, MBF1, and MBF2 flags HIGH and the EF, AE, and FF

flags LOW. The LOW-to-HIGH transition of RST latches the status of the FS1 and FS0 inputs to select

Almost-FullflagandAlmost-Emptyflagoffset.

SIZ0,

Port B Bus Size

I

A LOW-to-HIGH transition of CLKB latches the states of SIZ0, SIZ1, and BE, and the following LOW-to-

SIZ1

Selects

(Port B) HIGH transition of CLKB implements the latched states as a port B bus size. Port B bus sizes can be long

word, word, or byte. A HIGH on both SIZ0 and SIZ1 chooses a mailbox register for a port B 36-bit write or

read.

SW0,

Port B Byte Swap

I

At the beginning of each long word FIFO read, one of four modes of byte-order swapping is selected by

SW1

Selects

(PortB) SW0 and SW1. The four modes are no swap, byte swap, word swap, and byte-word swap. Byte-order

swapping is possible with any bus-size selection.

W/RA

PortAWrite/Read

I

A HIGH selects a write operation and a LOW selects a read operation on port A for a LOW-to-HIGH

Select

transition of CLKA. The A0-A35 outputs are in the high-impedance state when W/RA is HIGH.

W/RB

PortBWrite/Read

I

A HIGH selects a write operation and a LOW selects a read operation on port B for a LOW-to-HIGH

Select

transition of CLKB. The B0-B35 outputs are in the high-impedance state when W/RB is HIGH.

相关PDF资料 |

PDF描述 |

|---|---|

| LTC2174CUKG-14#TRPBF | IC ADC 14BIT 105MSPS QUAD 52QFN |

| LTC2153IUJ-14#TRPBF | IC ADC 14BIT DUAL 310MSPS 40QFN |

| MS3112E24-61PX | CONN RCPT 61POS BOX MNT W/PINS |

| AD679AJ | IC ADC 14BIT SAMPLING 44-JLCC |

| VI-26M-MX-F3 | CONVERTER MOD DC/DC 10V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT72V3613L15PQF | 功能描述:IC FIFO CLOCK 64X36 15NS 132PQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V3613L20PF | 功能描述:IC FIFO CLOCK 64X36 20NS 120TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V3613L20PF8 | 功能描述:IC FIFO CLOCK 64X36 20NS 120TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V3613L20PQF | 功能描述:IC FIFO CLOCK 64X36 20NS 132PQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V3614L12PF | 功能描述:IC FIFO 64X36X2 12NS 120QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

发布紧急采购,3分钟左右您将得到回复。