- 您现在的位置:买卖IC网 > PDF目录4584 > IDT72V51246L7-5BB (IDT, Integrated Device Technology Inc)IC FLOW CTRL MULTI QUEUE 256-BGA PDF资料下载

参数资料

| 型号: | IDT72V51246L7-5BB |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 14/56页 |

| 文件大小: | 0K |

| 描述: | IC FLOW CTRL MULTI QUEUE 256-BGA |

| 标准包装: | 1 |

| 类型: | 多队列流量控制 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 256-BBGA |

| 供应商设备封装: | 256-BGA(17x17) |

| 包装: | 托盘 |

| 其它名称: | 72V51246L7-5BB |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页

21

COMMERCIALANDINDUSTRIAL

TEMPERATURERANGES

IDT72V51236/72V51246/72V51256 3.3V, MULTI-QUEUE FLOW-CONTROL DEVICES

(4 QUEUES) 36 BIT WIDE CONFIGURATION 589,824, 1,179,648 and 2,359,296 bits

The packet ready logic monitors all start and end of packet markers both as

they enter respective queues via the write port and as they exit queues via

the read port. The multi-queue internal logic increments and decrements a

packet counter, which is provided for each queue. The functionality of the

packet ready logic provides status as to whether at least one full packet of data

is available within the selected queue. A partial packet in a queue is regarded

as a packet not ready and

PR (active LOW) will be HIGH. In Packet mode, no

words can be read from a queue until at least one complete packet has been

written into the queue, regardless of

REN. For example, if a TSOP has been

written and some number of words later a TEOP is written a full packet of data

is deemed to be available, and the

PR flag and OV will go active LOW.

Consequently if reads begin from a queue that has only one complete packet

and the RSOP is detected on the output port as data is being read out,

PR will

go inactive HIGH.

OV willremainLOWindicatingthereisstillvaliddatabeing

read out of that queue until the REOP is read. The user may proceed with the

reading operation until the current packet has been read out and no further

completepacketsareavailable.Ifduringthattimeanothercompletepackethas

been written into the queue and the

PR flagwillagaingoneactive,thenreads

from the new packet may follow after the current packet has been completely

read out.

The packet counters therefore look for start of packet markers followed by

end of packet markers and regard data in between the TSOP and TEOP as

a full packet of data. The packet monitoring has no limitation as to how many

packets are written into a queue, the only constraint is the depth of the queue.

Note, there is a minimum allowable packet size of four words, inclusive of the

TSOP marker and TEOP marker.

The packet logic does expect a TSOP marker to be followed by a TEOP

marker.

If a second TSOP marker is written after a first, it is ignored and the logic

regards data between the first TSOP and the first subsequent TEOP as the full

packet. The same is true for TEOP; a second consecutive TEOP mark is

ignored. On the read side the user should regard a packet as being between

the first RSOP and the first subsequent REOP and disregard consecutive

RSOP markers and/or REOP markers. This is why a TEOP may be written

twice, using the second TEOP as the filler word.

As an example, the user may also wish to implement the use of an “Almost

End of Packet”(AEOP) marker. For example, the AEOP can be assigned to

data input bit D33. The purpose of this AEOP marker is to provide an indicator

that the end of packet is a fixed (known) number of reads away from the end

of packet. This is a useful feature when due to latencies within the system,

monitoring the REOP marker alone does not prevent “over reading” of the data

from the queue selected. For example, an AEOP marker set 4 writes before

the TEOP marker provides the device connected to the read port with and

“almost end of packet” indication 4 cycles before the end of packet.

TheAEOPcanbesetanynumberofwordsbeforetheendofpacketdetermined

by user requirements or latencies involved in the system.

See Figure 17, Reading in Packet Mode during a Queue Change, Figure

18, Data Input (Transmit) Packet Mode of Operation and Figure 19, Data

Output (Receive) Packet Mode of Operation.

PACKET MODE – MODULO OPERATION

The internal packet ready control logic performs no operation on these

modulo bits, they are only informational bits that are passed through with the

respective data byte(s).

When utilizing the multi-queue flow-control device in packet mode, the user

may also want to consider the implementation of “Modulo” operation or “valid

byte marking”. Modulo operation may be useful when the packets being

transferred through a queue are in a specific byte arrangement even though

thedatabuswidthis36bits.InModulooperationtheusercanconcatenatebytes

toformaspecificdatastringthroughthemulti-queuedevice.Apossiblescenario

is where a limited number of bytes are extracted from the packet for either

analysis or filtered for security protection. This will only occur when the first 36

bit word of a packet is written in and the last 36 bit word of packet is written in.

The modulo operation is a means by which the user can mark and identify

specific data within the Queue.

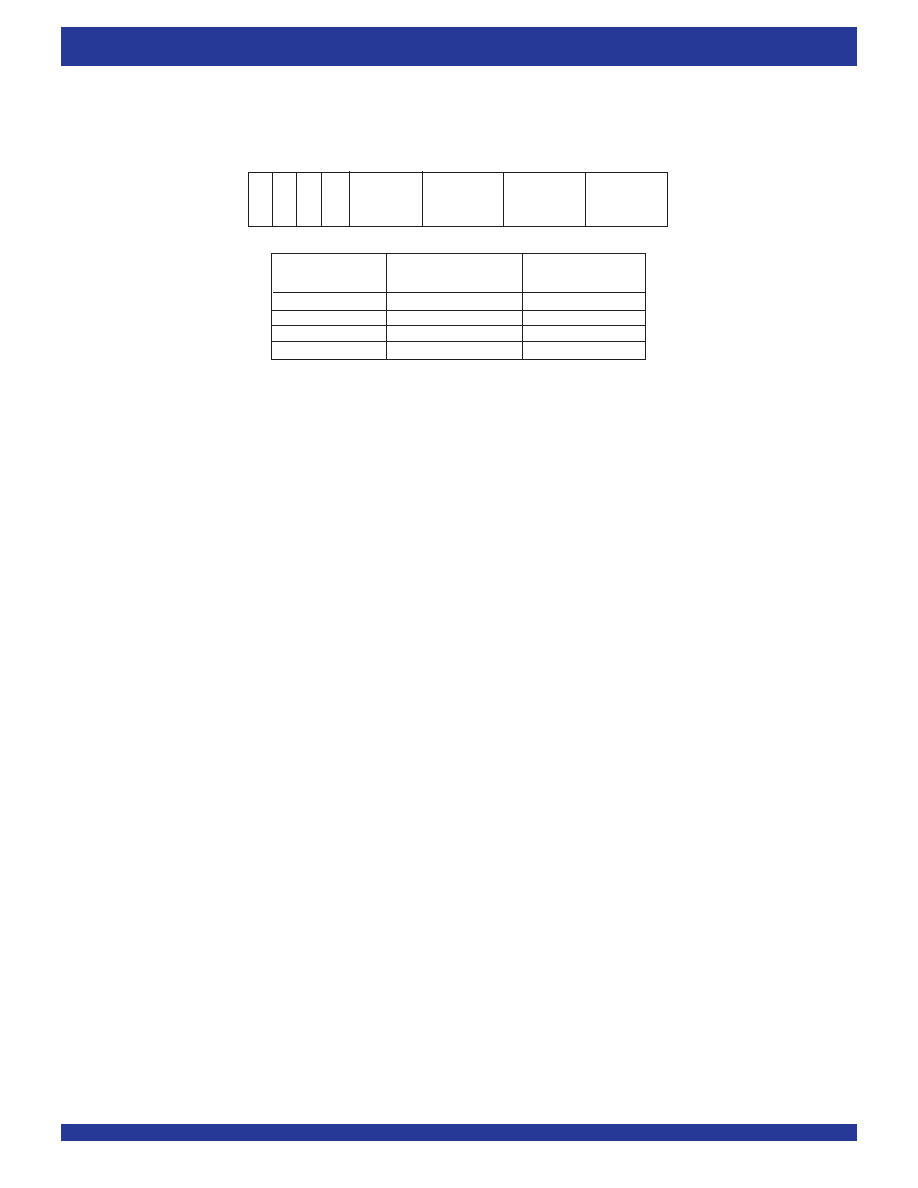

On the write port data input bits, D32 (transmit modulo bit 2, TMOD2) and

D33(transmitmodulobit1,TMOD1)canbeusedasdatamarkers.Anexample

of this could be to use D32 and D33 to code which bytes of a word are part

of the packet that is also being marked as the “Start of Marker” or “End of

Marker”. Conversely on the read port when reading out these marked words,

data outputs Q32 (receive modulo bit 2, RMOD2) and Q33 (receive modulo

bit 1, RMOD1) will pass on the byte validity information for that word. Refer to

Table 5 for one example of how the modulo bits may be setup and used. See

Figure 18, Data Input (Transmit) Packet Mode of Operation and Figure 19,

Data Output (Receive) Packet Mode of Operation.

BYTE A

BYTE B

BYTE C

BYTE D

D0/Q0

D35/Q35

TMOD1 (D33)

RMOD1 (Q33)

TMOD2 (D32)

RMOD2 (Q32)

VALID BYTES

0

A, B, C, D

01A

1

0

A, B

1

A, B, C

D15/Q15

D23/Q23

D31/Q31

D34/Q34

D33/Q33

D32/Q32

MOD

2

MOD

1

SOP

EOP

D7/Q7

5937 drw07

TABLE 5 — PACKET MODE VALID BYTE

NOTE:

Packet Mode is only available when the Input Port and Output Port are 36 bits wide.

相关PDF资料 |

PDF描述 |

|---|---|

| MIC5322-PNYMT TR | IC REG LDO 3V/2.85V .15A 6MLF |

| IDT72V51446L7-5BB8 | IC FLOW CTRL MULTI QUEUE 256-BGA |

| LFECP10E-3FN484I | IC FPGA 10.2KLUTS 484FPBGA |

| LFECP10E-4FN484C | IC FPGA 10.2KLUTS 484FPBGA |

| LFEC10E-3FN484I | IC FPGA 10.2KLUTS 484FPBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT72V51246L7-5BB8 | 功能描述:IC FLOW CTRL MULTI QUEUE 256-BGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT72V51246L7-5BBI | 功能描述:IC FLOW CTRL MULTI QUEUE 256-BGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT72V51253L6BB | 功能描述:IC FLOW CTRL MULTI QUEUE 256-BGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT72V51253L6BB8 | 功能描述:IC FLOW CTRL MULTI QUEUE 256-BGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT72V51253L6BBG | 功能描述:IC FLOW CTRL MULTI QUEUE 256-BGA RoHS:是 类别:集成电路 (IC) >> 专用 IC 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

发布紧急采购,3分钟左右您将得到回复。