- 您现在的位置:买卖IC网 > PDF目录2077 > IDT72V73273BBG (IDT, Integrated Device Technology Inc)IC DGTL SW 32768X32768 208-BGA PDF资料下载

参数资料

| 型号: | IDT72V73273BBG |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 17/36页 |

| 文件大小: | 0K |

| 描述: | IC DGTL SW 32768X32768 208-BGA |

| 标准包装: | 12 |

| 系列: | 72V |

| 类型: | 多路复用器 |

| 电路: | 8 x 1:1 |

| 电压电源: | 单电源 |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 208-BGA |

| 供应商设备封装: | 208-PBGA(17x17) |

| 包装: | 托盘 |

| 其它名称: | 72V73273BBG |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

24

INDUSTRIAL TEMPERATURERANGE

IDT72V73273 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH WITH RATE MATCHING 32,768 x 32,768 CHANNELS

JTAG SUPPORT

TheIDT72V73273JTAGinterfaceconformstotheBoundary-Scanstandard

IEEE-1149.1.Thisstandardspecifiesadesign-for-testabilitytechniquecalled

Boundary-Scan test (BST). The operation of the boundary-scan circuitry is

controlled by an external test access port (TAP) Controller.

TEST ACCESS PORT (TAP)

The Test Access Port (TAP) provides access to the test functions of the

IDT72V73273. It consists of three input pins and one output pin.

Test Clock Input (TCK)

TCKprovidestheclockforthetestlogic.TheTCKdoesnotinterferewithany

on-chipclockandthusremainsindependent.TheTCKpermitsshiftingoftest

data into or out of the Boundary-Scan register cells concurrently with the

operationofthedeviceandwithoutinterferingwiththeon-chiplogic.

Test Mode Select Input (TMS)

The logic signals received at the TMS input are interpreted by the TAP

Controllertocontrolthetestoperations.TheTMSsignalsaresampledatthe

risingedgeoftheTCKpulse. ThispinisinternallypulledtoVCCwhenitisnot

driven from an external source.

Test Data Input (TDI)

Serialinputdataappliedtothisportisfedeitherintotheinstructionregisteror

intoatestdataregister,dependingonthesequencepreviouslyappliedtothe

TMSinput.Bothregistersaredescribedinasubsequentsection.Thereceived

inputdataissampledattherisingedgeofTCKpulses.Thispinisinternallypulled

to VCC when it is not driven from an external source.

TestDataOutput(TDO)

DependingonthesequencepreviouslyappliedtotheTMSinput,thecontents

ofeithertheinstructionregisterordataregisterareseriallyshiftedoutthrough

the TDO pin on the falling edge of each TCK pulse. When no data is shifted

through the boundary scan cells, the TDO driver is set to a High-Impedance

state.

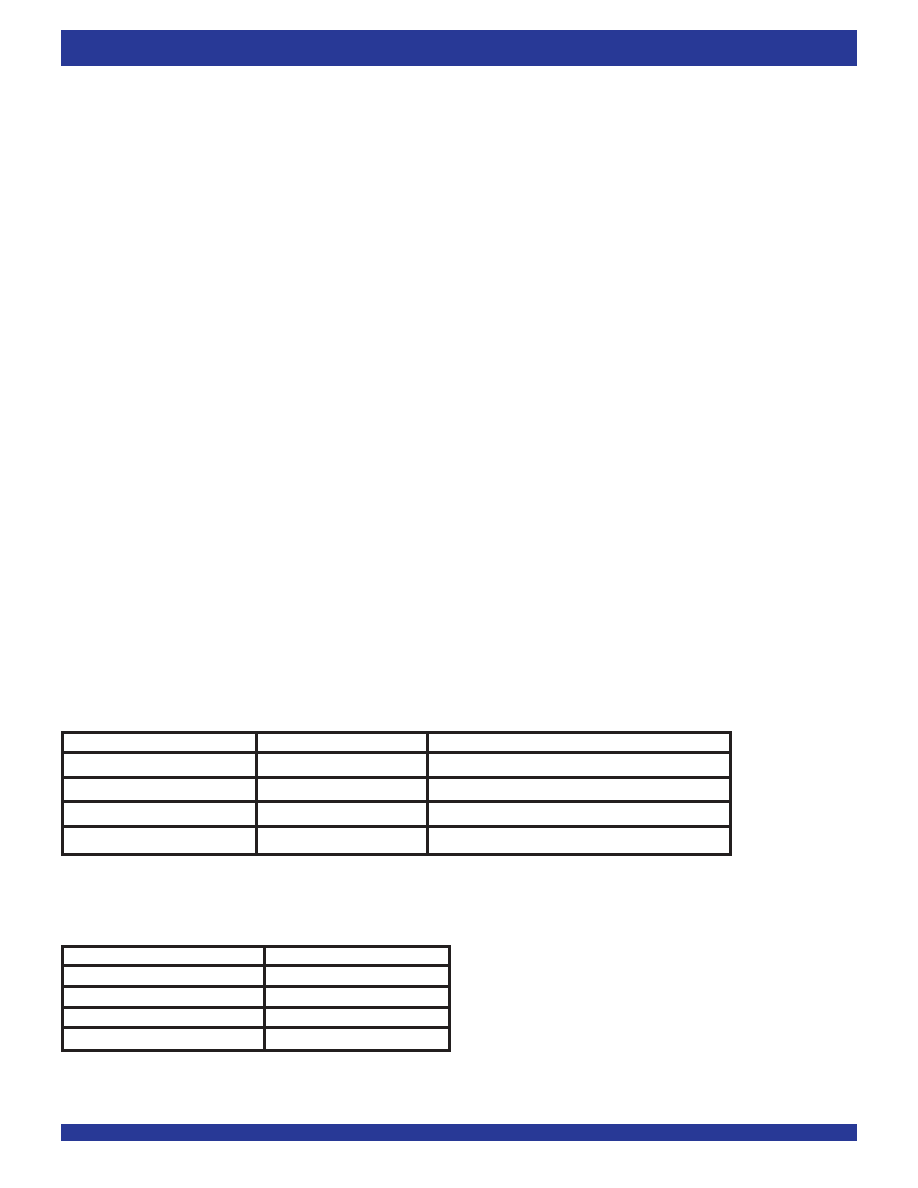

TABLE 17—IDENTIFICATION REGISTER DEFINITIONS

INSTRUCTION FIELD

VALUE

DESCRIPTION

RevisionNumber(31:28)

0x0

Reservedforversionnumber

IDT Device ID (27:12)

0x0430

DefinesIDTpartnumber

IDT JEDEC ID (11:1)

0x33

AllowsuniqueidentificationofdevicevendorasIDT

ID Register Indicator Bit (Bit 0)

1

IndicatesthepresenceofanIDregister

REGISTER NAME

BIT SIZE

Instruction(IR)

4

Bypass (BYR)

1

Identification(IDR)

32

Boundary Scan (BSR)

Note(1)

TABLE 18 — SCAN REGISTER SIZES

NOTES:

1. The Boundary Scan Descriptive Language (BSDL) file for this device is available on

the IDT website (www.idt.com), or by contacting your local IDT sales representative.

Test Reset (TRST)

ResettheJTAGscanstructure.ThispinisinternallypulledtoVCCwhenit

is not driven from an external source.

INSTRUCTION REGISTER

InaccordancewiththeIEEE-1149.1standard,theIDT72V73273usespublic

instructions.TheIDT72V73273JTAGinterfacecontainsafour-bitinstruction

register.InstructionsareseriallyloadedintotheinstructionregisterfromtheTDI

whentheTAPControllerisinitsshift-IRstate.Subsequently,theinstructionsare

decodedtoachievetwobasicfunctions:toselectthetestdataregisterthatmay

operatewhiletheinstructioniscurrent,andtodefinetheserialtestdataregister

path, which is used to shift data between TDI and TDO during data register

scanning. See Table 12 for Instruction decoding.

TESTDATAREGISTER

AsspecifiedinIEEE-1149.1,theIDT72V73273JTAGInterfacecontainstwo

testdataregisters:

The Boundary-Scan register

The Boundary-Scan register consists of a series of Boundary-Scan cells

arranged to form a scan path around the boundary of the IDT72V73273 core

logic.

The Bypass Register

TheBypassregisterisasinglestageshiftregisterthatprovidesaone-bitpath

from TDI to TDO. The IDT72V73273 boundary scan register bits are shown

inTable14.Bit0isthefirstbitclockedout.Allthree-stateenablebitsareactive

HIGH.

ID CODE REGISTER

AsspecifiedinIEEE-1149.1,thisinstructionloadstheIDRwiththeRevision

Number, Device ID, JEDEC ID, and ID Register Indicator Bit. See Table 10.

相关PDF资料 |

PDF描述 |

|---|---|

| IDT72V845L10PF | IC FIFO SYNC 4096X18 128QFP |

| IDT72V851L10TFG | IC FIFO 8192X9 DUAL SYNC 64TQFP |

| IDT72V85L15PAG | IC FIFO ASYNCH 4096X18 56TSSOP |

| IDT72V8980PVG | IC DGTL SW 256X256 48-SSOP |

| IDT72V8981JG | IC DGTL SW 128X128 44-PLCC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT72V801L10PF | 功能描述:IC SYNC FIFO 256X9 10NS 64QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V801L10PF8 | 功能描述:IC SYNC FIFO 256X9 10NS 64QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V801L10PFG | 功能描述:IC FIFO 256X9 SYNC DUAL 64TQFP RoHS:是 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V801L10PFG8 | 制造商:Integrated Device Technology Inc 功能描述:IC SYNC FIFO 256X9 10NS 64QFP |

| IDT72V801L10TF | 功能描述:IC SYNC FIFO 256X9 10NS 64QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

发布紧急采购,3分钟左右您将得到回复。