- 您现在的位置:买卖IC网 > PDF目录1924 > IDT79RC32T351-133DHG (IDT, Integrated Device Technology Inc)IC MPU 32BIT CORE 133MHZ 208-QFP PDF资料下载

参数资料

| 型号: | IDT79RC32T351-133DHG |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 39/42页 |

| 文件大小: | 0K |

| 描述: | IC MPU 32BIT CORE 133MHZ 208-QFP |

| 产品变化通告: | Product Discontinuation 07/Dec/2009 |

| 标准包装: | 24 |

| 系列: | Interprise™ |

| 处理器类型: | RISC 32-位 |

| 速度: | 133MHz |

| 电压: | 2.5V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 208-BFQFP |

| 供应商设备封装: | 208-PQFP(28x28) |

| 包装: | 托盘 |

| 其它名称: | 79RC32T351-133DHG |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页当前第39页第40页第41页第42页

6 of 42

May 25, 2004

IDT 79RC32351

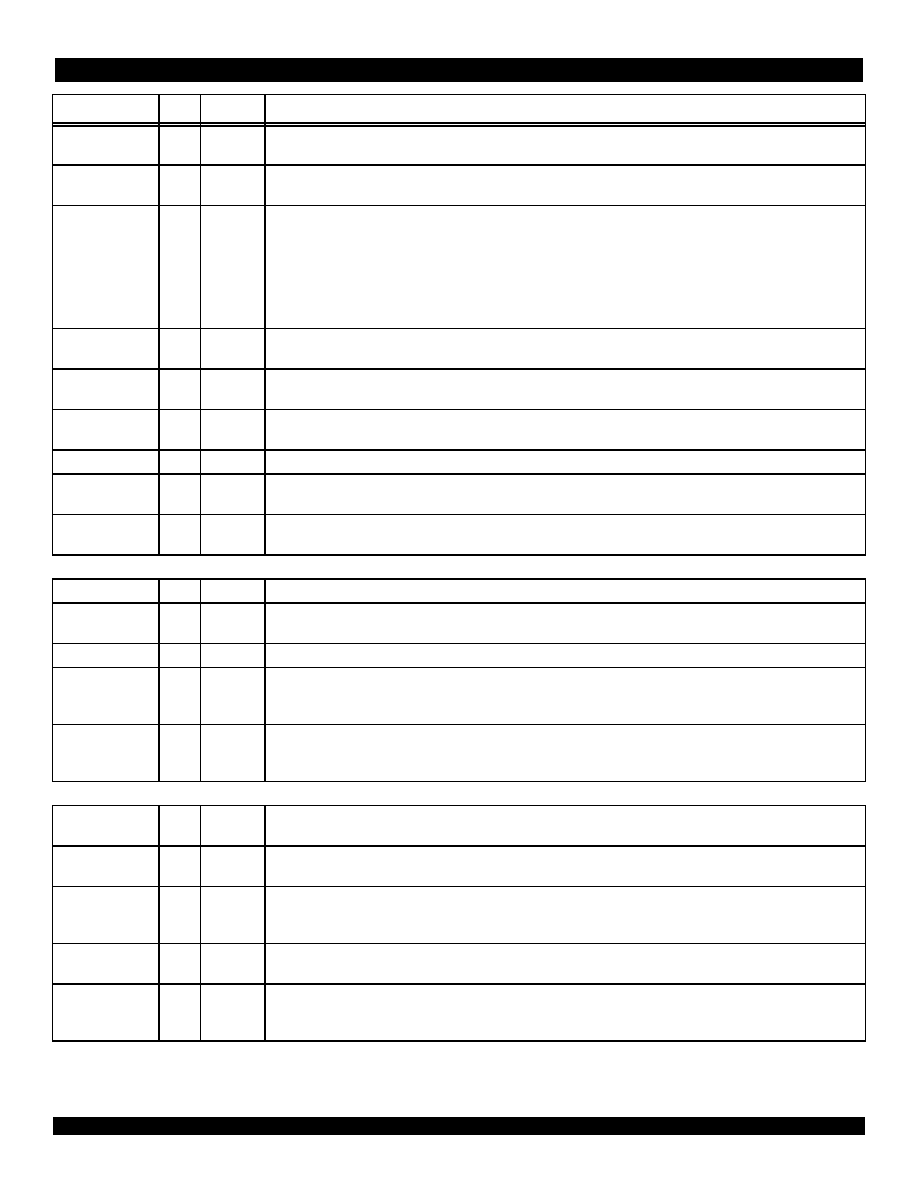

RWN

O

High Drive Read or Write. This signal indicates if the transaction on the memory and peripheral bus is a read transaction or a write

transaction. A high level indicates a read from an external device, a low level indicates a write to an external device.

OEN

O

High Drive Output Enable. This signal is asserted low when data should be driven by an external device during device read transac-

tions on the memory and peripheral bus.

BWEN[3:0]

O

High Drive SDRAM Byte Enable Mask or Memory and I/O Byte Write Enables. These signals are used as data input/output masks

during SDRAM transactions and as byte write enable signals during device controller transactions on the memory and

peripheral bus. They are active low.

BWEN[0] corresponds to byte lane MDATA[7:0].

BWEN[1] corresponds to byte lane MDATA[15:8].

BWEN[2] corresponds to byte lane MDATA[23:16].

BWEN[3] corresponds to byte lane MDATA[31:24].

SDCSN[1:0]

O

High Drive SDRAM Chip Select. These signals are used to select the SDRAM device on the memory and peripheral bus. Each bit is

asserted low during an access to the selected SDRAM.

RASN

O

High Drive SDRAM Row Address Strobe. The row address strobe asserted low during memory and peripheral bus SDRAM transac-

tions.

CASN

O

High Drive SDRAM Column Address Strobe. The column address strobe asserted low during memory and peripheral bus SDRAM

transactions.

SDWEN

O

High Drive SDRAM Write Enable. Asserted low during memory and peripheral bus SDRAM write transactions.

CKENP

O

Low Drive SDRAM Clock Enable. Asserted high during active SDRAM clock cycles.

Primary function: General Purpose I/O, GPIOP[21].

SDCLKINP

I

STI

SDRAM Clock Input. This clock input is a delayed version of SYSCLKP. SDRAM read data is sampled into the RC32351

on the rising edge of this clock.

ATM Interface

ATMINP[11:0]

I

STI

ATM PHY Inputs. These pins are the inputs for the ATM interface.

ATMIOP[1:0]

I/O

Low Drive

with STI

ATM PHY Bidirectional Signals. These pins are the bidirectional pins for the ATM interface.

ATMOUTP[9:0]

O

Low Drive ATM PHY Outputs. These pins are the outputs for the ATM interface.

TXADDR[1:0]

O

Low Drive ATM Transmit Address [1:0]. 2-bit address bus used for transmission in Utopia-2 mode.

TXADDR[0] Primary function: General purpose I/O, GPIOP[22].

TXADDR[1] Primary function: General purpose I/O, GPIOP[23].

RXADDR[1:0]

O

Low Drive ATM Receive Address [1:0]. 2-bit address bus for receiving in Utopia-2 mode.

RXADDR[0] Primary function: General purpose I/O, GPIOP[24].

RXADDR[1] Primary function: General purpose I/O, GPIOP[25].

General Purpose Input/Output

GPIOP[0]

I/O

Low Drive

with STI

General Purpose I/O. This pin can be configured as a general purpose I/O pin.

Alternate function: UART channel 0 serial output, U0SOUTP.

GPIOP[1]

I/O

Low Drive

with STI

General Purpose I/O. This pin can be configured as a general purpose I/O pin.

Alternate function: UART channel 0 serial input, U0SINP.

GPIOP[2]

I/O

Low Drive

with STI

General Purpose I/O. This pin can be configured as a general purpose I/O pin.

1st Alternate function: UART channel 0 ring indicator, U0RIN.

2nd Alternate function: JTAG boundary scan tap controller reset, JTAG_TRST_N.

GPIOP[3]

I/O

Low Drive

with STI

General Purpose I/O. This pin can be configured as a general purpose I/O pin.

Alternate function: UART channel 0 data carrier detect, U0DCRN.

GPIOP[4]

I/O

Low Drive

with STI

General Purpose I/O. This pin can be configured as a general purpose I/O pin.

1st Alternate function: UART channel 0 data terminal ready, U0DTRN.

2nd Alternate function: CPU or DMA transaction indicator, CPUP.

Name

Type I/O Type

Description

Table 1 Pin Descriptions (Part 2 of 7)

相关PDF资料 |

PDF描述 |

|---|---|

| IDT79RC32V332-150DHG | IC PROC 32BIT CPU 150MHZ 208-QFP |

| IDT79RC32V333-150DHG | IC PROC 32BIT CPU 150MHZ 208-QFP |

| IDT79RC64T575-250DP | IC MPU 64BIT EMB 250MHZ 208-QFP |

| IDT79RC64V475-200DP | IC MPU 64BIT EMB 200MHZ 208-QFP |

| IDT82P20416DBFG | IC LIU T1/E1/J1 16CH SH 484BGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT79RC32T355-100DHGI | 制造商:Integrated Device Technology Inc 功能描述:IC MPU 32BIT CORE 100MHZ 208-QFP |

| IDT79RC32T355-133DH | 功能描述:IC MPU 32BIT CORE 133MHZ 208-QFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - 微处理器 系列:Interprise™ 标准包装:2 系列:MPC8xx 处理器类型:32-位 MPC8xx PowerQUICC 特点:- 速度:133MHz 电压:3.3V 安装类型:表面贴装 封装/外壳:357-BBGA 供应商设备封装:357-PBGA(25x25) 包装:托盘 |

| IDT79RC32T355-133DHG | 功能描述:IC MPU 32BIT CORE 133MHZ 208-QFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - 微处理器 系列:Interprise™ 标准包装:2 系列:MPC8xx 处理器类型:32-位 MPC8xx PowerQUICC 特点:- 速度:133MHz 电压:3.3V 安装类型:表面贴装 封装/外壳:357-BBGA 供应商设备封装:357-PBGA(25x25) 包装:托盘 |

| IDT79RC32T355133DHGI | 制造商:IDT 功能描述:Pb Free |

| IDT79RC32T355-133DHGI | 制造商:Integrated Device Technology Inc 功能描述:IC MPU 32BIT CORE 133MHZ 208-QFP |

发布紧急采购,3分钟左右您将得到回复。