- 您现在的位置:买卖IC网 > PDF目录9973 > IDT82V2041EPP8 (IDT, Integrated Device Technology Inc)IC LIU T1/J1/E1 1CH 44-TQFP PDF资料下载

参数资料

| 型号: | IDT82V2041EPP8 |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 24/75页 |

| 文件大小: | 0K |

| 描述: | IC LIU T1/J1/E1 1CH 44-TQFP |

| 标准包装: | 1,250 |

| 类型: | 线路接口装置(LIU) |

| 规程: | E1 |

| 电源电压: | 3.13 V ~ 3.47 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 44-LQFP |

| 供应商设备封装: | 44-TQFP(10x10) |

| 包装: | 带卷 (TR) |

| 其它名称: | 82V2041EPP8 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页

IDT82V2041E

SINGLE CHANNEL T1/E1/J1 SHORT HAUL LINE INTERFACE UNIT

Functional Description

30

December 9, 2005

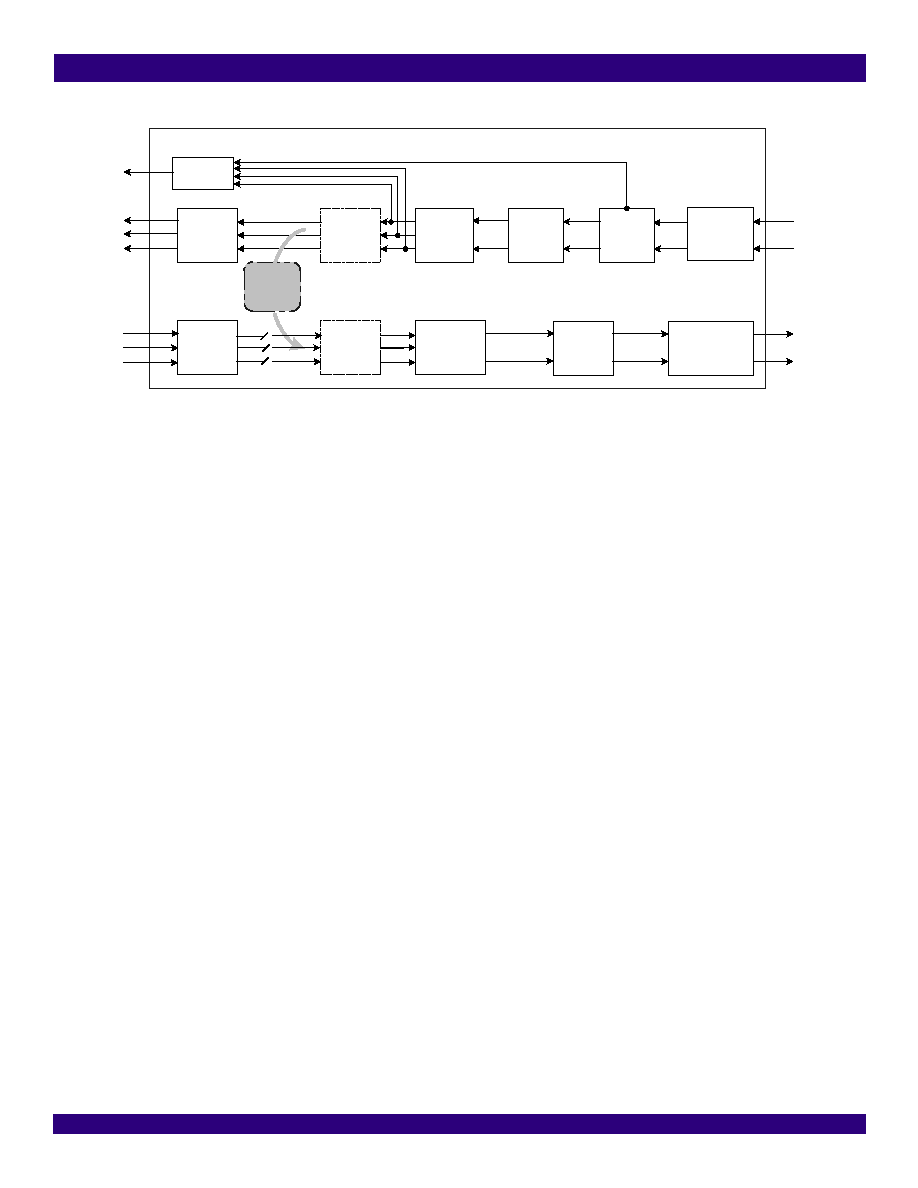

Figure-15 Remote Loopback

3.8.4

INBAND LOOPBACK

When PATT[1:0] bits (MAINT0, 0DH) are set to ‘11’, the IDT82V2041E

isconfiguredinInbandLoopbackmode.Inthismode,anunframedactivate/

Deactivate Loopback Code is generated repeatedly in transmit direction

per ANSI T1. 403 which overwrite the transmit signals. In receive direction,

theframedorunframedcodeisdetectedperANSIT1.403,eveninthepres-

ence of 10-2 bit error rate.

If the Automatic Remote Loopback is enabled by setting ARLP bit

(MAINT1, 0EH) to ‘1’, the chip will establish/demolish the Remote Loop-

back based on the reception of the Activate Loopback Code/Deactivate

Loopback Code for 5.1 s. If the ARLP bit (MAINT1, 0EH) is set to ‘0’, the

Remote Loopback can also be demolished forcedly.

3.8.4.1 TRANSMIT ACTIVATE/DEACTIVATE LOOPBACK CODE

The pattern of the transmit Activate/Deactivate Loopback Code is

defined by the TIBLB[7:0] bits (MAINT3, 10H). Whether the code repre-

sentsanActivateLoopbackCodeoraDeactivateLoopbackCodeisjudged

by the far end receiver. The length of the pattern ranges from 5 bits to 8 bits,

as selected by the TIBLB_L[1:0] bits (MAINT2, 0FH). The pattern can be

programmed to 6-bit-long or 8-bit-long by repeating itself respectively if it

is 3-bit-long or 4-bit-long. When the PATT[1:0] bits (MAINT0, 0DH) are set

to ‘11’, the transmission of the Activate/Deactivate Loopback Code is initi-

ated. If the PATT_CLK bit (MAINT0, 0DH) is set to ‘0’ and the PATT[1:0]

bits (MAINT0, 0DH) are set to ‘00’, the transmission of the Activate/Deac-

tivate Loopback Code will stop.

The local transmit activate/deactivate code setting should be the same

as the receive code setting in the remote end. It is the same thing for the

other way round.

3.8.4.2 RECEIVE ACTIVATE/DEACTIVATE LOOPBACK CODE

The pattern of the receive Activate Loopback Code is defined by the

RIBLBA[7:0] bits (MAINT4, 11H). The length of this pattern ranges from 5

bits to 8 bits, as selected by the RIBLBA_L [1:0] bits (MAINT2, 0FH). The

pattern can be programmed to 6-bit-long or 8-bit-long respectively by

repeating itself if it is 3-bit-long or 4-bit-long.

The pattern of the receive Deactivate Loopback Code is defined by the

RIBLBD[7:0] bits (MAINT5, 12H). The length of the receive Deactivate

Loopback Code ranges from 5 bits to 8 bits, as selected by the

RIBLBD_L[1:0] bits (MAINT2, 0FH). The pattern can be programmed to 6-

bit-long or 8-bit-long respectively by repeating itself if it is 3-bit-long or 4-

bit-long.

After the Activate Loopback Code has been detected in the receive data

for more than 30 ms (in E1 mode) / 40 ms (in T1/J1 mode), the IBLBA_S

bit (STAT0, 17H) will be set to ‘1’ to declare the reception of the Activate

Loopback Code.

After the Deactivate Loopback Code has been detected in the receive

dataformorethan30ms(InE1mode)/40ms(InT1/J1mode),theIBLBD_S

bit (STAT0, 17H) will be set to ‘1’ to declare the reception of the Deactivate

Loopback Code.

When the IBLBA_IES bit (INTES, 16H) is set to ‘0’, only the ‘0’ to ‘1’ tran-

sition of the IBLBA_S bit will generate an interrupt and set the IBLBA_IS bit

(INTS0, 19H) to ‘1’. When the IBLBA_IES bit is set to ‘1’, any changes of

the IBLBA_S bit will generate an interrupt and set the IBLBA_IS bit (INTS0,

19H) to ‘1’. The IBLBA_IS bit will be reset to ‘0’ after being read.

When the IBLBD_IES bit (INTES, 16H) is set to ‘0’, only the ‘0’ to ‘1’ tran-

sition of the IBLBD_S bit will generate an interrupt and set the IBLBD_IS

bit (INTS0, 19H) to ‘1’. When the IBLBD_IES bit is set to ‘1’, any changes

of the IBLBD_S bit will generate an interrupt and set the IBLBD_IS bit

(INTS0, 19H) to ‘1’. The IBLBD_IS bit will be reset to ‘0’ after being read.

B8ZS/

HDB3/AMI

Encoder

Jitter

Attenuator

B8ZS/

HDB3/AMI

Decoder

Jitter

Attenuator

Data

Slicer

Adaptive

Equalizer

LOS/AIS

Detection

Clock and

Data

Recovery

Receiver

Internal

Termination

TCLK

TDN

TD/TDP

RCLK

CV/RDN

LOS

RD/RDP

RRING

TTIP

TRING

RTIP

Remote

Loopback

Line

Driver

Waveform

Shaper

Transmitter

Internal

Termination

相关PDF资料 |

PDF描述 |

|---|---|

| VE-B5B-IV-F1 | CONVERTER MOD DC/DC 95V 150W |

| VE-26W-IX-B1 | CONVERTER MOD DC/DC 5.5V 75W |

| MS3100E28-10S | CONN RCPT 7POS WALL MNT W/SCKT |

| IDT72605L25PF | IC FIFO BI SYNC 256X18 64-TQFP |

| MS3100E22-20P | CONN RCPT 9POS WALL MNT W/PINS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT82V2041EPPG | 功能描述:IC LIU T1/J1/E1 1CH 44-TQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:250 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| IDT82V2041EPPG8 | 功能描述:IC LIU T1/J1/E1 1CH 44-TQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:250 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| IDT82V2042EPF | 功能描述:IC LIU T1/J1/E1 2CH SHORT 80TQFP RoHS:否 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:250 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| IDT82V2042EPF8 | 功能描述:IC LIU T1/J1/E1 2CH SHORT 80TQFP RoHS:否 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:250 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| IDT82V2042EPFG | 功能描述:IC LIU T1/J1/E1 2CH SHORT 80TQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:250 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。