参数资料

| 型号: | IP80C88-2 |

| 厂商: | Intersil |

| 文件页数: | 18/38页 |

| 文件大小: | 0K |

| 描述: | IC CPU 8/16BIT 5V 8MHZ 40-DIP |

| 标准包装: | 99 |

| 处理器类型: | 80C88 8/16-位 |

| 速度: | 8MHz |

| 电压: | 4.75 V ~ 5.25 V |

| 安装类型: | 通孔 |

| 封装/外壳: | 40-DIP(0.600",15.24mm) |

| 供应商设备封装: | 40-DIP |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页当前第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页

25

FN2949.4

February 22, 2008

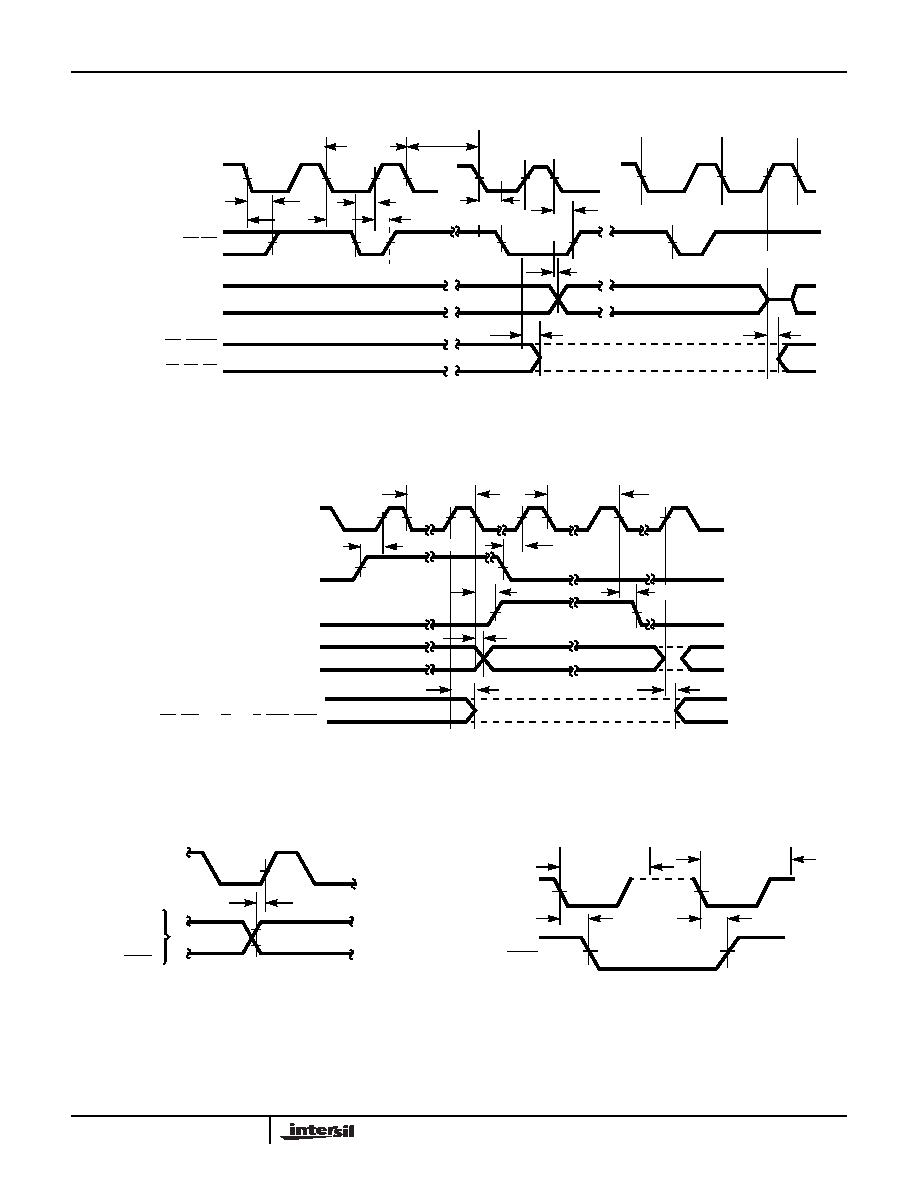

FIGURE 13. REQUEST/GRANT SEQUENCE TIMING (MAXIMUM MODE ONLY)

NOTE: The coprocessor may not drive the busses outside the region shown without risking contention.

FIGURE 14. HOLD/HOLD ACKNOWLEDGE TIMING (MINIMUM MODE ONLY)

NOTE:

Setup requirements for asynchronous signals only to guarantee recognition at next CLK.

FIGURE 15. ASYNCHRONOUS SIGNAL RECOGNITION

NOTE:

Setup requirements for asynchronous signals only to

guarantee recognition at next CLK.

FIGURE 16. BUS LOCK SIGNAL TIMING (MAXIMUM MODE

ONLY)

Waveforms (Continued)

CLK

TCLGH

RQ/GT

PREVIOUS GRANT

AD7-AD0

RD, LOCK

A19/S6-A16/S3

S2, S1, S0

TCLCL

ANY

CLK

CYCLE

> 0-CLK

CYCLES

PULSE 2

80C88

TGVCH (14)

TCHGX (15)

TCLGH (44)

PULSE 1

COPROCESSOR

RQ

TCLAZ (25)

80C88 GT

PULSE 3

COPROCESSOR

RELEASE

(SEE NOTE)

TCHSZ (26)

(1)

TCLGL

(43)

COPROCESSOR

TCHSV (21)

(44)

CLK

HOLD

HLDA

A15-A8

A19/S6-A16/S3

RD, WR, I/O/M, DT/R, DEN, SSO

80C88

THVCH (13)

TCLHAV (36)

≥ 1CL

1 OR 2

CYCLES

TCLAZ (19)

COPROCESSOR

80C88

TCLHAV (36)

CYCLE

TCHSZ (20)

THVCH (13)

TCHSV (21)

(SEE NOTE)

AD7-AD0

NMI

INTR

TEST

CLK

SIGNAL

TINVCH (SEE NOTE)

(13)

ANY CLK CYCLE

CLK

LOCK

TCLAV

ANY CLK CYCLE

(23)

TCLAV

(23)

80C88

相关PDF资料 |

PDF描述 |

|---|---|

| IS80C286-20 | IC CPU 16BIT 5V 20MHZ 68-PLCC |

| ISL1532IRZ | IC LINE DRIVER DUAL 24-QFN |

| ISL1536IRZ | IC LINE DRVR DUAL ADSL2+ 16-QFN |

| ISL1539AIRZ | IC VDSL2 LINE DVR AMP 24QFN |

| ISL1539IVEZ | IC VDSL2 LINE DVR AMP 24HTTSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IP80C88-2/+ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:16-Bit Microprocessor |

| IP80C88-2S2064 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| IP80C88S2064 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| IP8101-032 | 制造商:SMC Corporation of America 功能描述:POSITIONER |

| IP8101-032-DH | 制造商:SMC Corporation of America 功能描述:Positioner, IP8000/8100 |

发布紧急采购,3分钟左右您将得到回复。