- 您现在的位置:买卖IC网 > PDF目录383110 > IP82C237 (HARRIS SEMICONDUCTOR) CMOS High Performance Programmable DMA Controller PDF资料下载

参数资料

| 型号: | IP82C237 |

| 厂商: | HARRIS SEMICONDUCTOR |

| 元件分类: | DMA控制器 |

| 英文描述: | CMOS High Performance Programmable DMA Controller |

| 中文描述: | 4 CHANNEL(S), 8 MHz, DMA CONTROLLER, PDIP40 |

| 文件页数: | 13/25页 |

| 文件大小: | 158K |

| 代理商: | IP82C237 |

4-160

registers to operate as in normal mode (Data-Width register

not accessible) until 16-bit transfer mode is again entered.

The four mask bits may also be cleared simultaneously by

using the Clear Mask Register command (see software com-

mands section). This command has no effect on the data-

width bits.

Temporary Register -

The internal Temporary register is

used to hold data during memory-to-memory transfers. Fol-

lowing the completion of the transfers, the last byte moved

can be read by the microprocessor. In the case of 16-bit

transfers, only the least significant 8-bits of the last word

transferred are stored in this register. The Temporary regis-

ter always contains the last byte transferred in the previous

memory-to-memory operation, unless cleared by a RESET

or Master Clear.

Software Commands Affected by

16-Bit Mode

Master Clear -

This software instruction has the same effect

as the hardware RESET. The Command, Status, Request,

and Temporary registers, and Internal First/Last Flip-Flop

and mode register counter are cleared and the Mask register

is set. When the Master Clear instruction occurs while in 16-

bit transfer mode, the 82C237 enters normal (8-bit) transfer

mode in the Idle cycle.

Clear Mask Register -

This command clears the mask bits

of all four channels, enabling them to accept DMA requests.

This command has no effect on data-width bits in 16-bit

transfer mode.

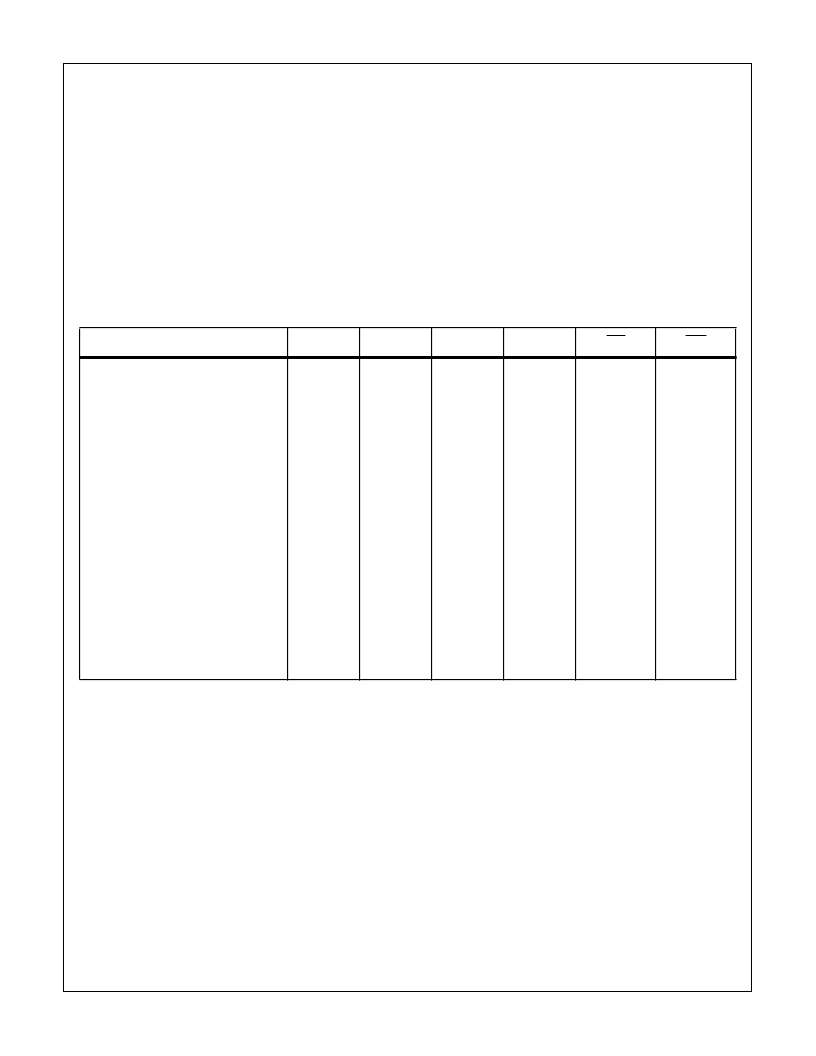

OPERATION

A3

A2

A1

A0

IOR

IOW

Read Status Register

1

0

0

0

0

1

Write Command Register

1

0

0

0

1

0

Read Request Register

1

0

0

1

0

1

Write Request Register

1

0

0

1

1

0

Read Command Register

1

0

1

0

0

1

Write Single Mask Bit (Note 1)

1

0

1

0

1

0

Write All Data-Width Bits (Notes 1, 2)

1

0

1

0

1

0

Read Mode Register

1

0

1

1

0

1

Write Mode Register

1

0

1

1

1

0

Set First/Last F/F

1

1

0

0

0

1

Clear First/Last F/F

1

1

0

0

1

0

Read Temporary Register

1

1

0

1

0

1

Master Clear

1

1

0

1

1

0

Clear Mode Reg. Counter

1

1

1

0

0

1

Clear Mask Register

1

1

1

0

1

0

Read All Mask/Data-Width Bits (Note 2)

1

1

1

1

0

1

Write All Mask Bits

1

1

1

1

1

0

NOTES:

1. The register to be written is determined by data bit 3.

2. Data-Width bits exist in 82C237, 16-bit mode only.

FIGURE 5. 16-BIT MODE SOFTWARE COMMAND CODES AND REGISTER CODES

82C237

相关PDF资料 |

PDF描述 |

|---|---|

| IP82C237-12 | CMOS High Performance Programmable DMA Controller |

| IP82C54-10Z | CMOS Programmable Intervel Timer |

| IP82C54Z | CMOS Programmable Intervel Timer |

| IP82C54-12 | CMOS Programmable Interval Timer |

| IP82C54 | CMOS Programmable Interval Timer |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IP82C237-12 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:CMOS High Performance Programmable DMA Controller |

| IP82C37A | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Harris Corporation 功能描述: |

| IP82C37A/+ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:DMA Controller |

| IP82C37A-12 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| IP82C37A-5 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Harris Corporation 功能描述: |

发布紧急采购,3分钟左右您将得到回复。