- 您现在的位置:买卖IC网 > PDF目录383110 > IP82C237 (HARRIS SEMICONDUCTOR) CMOS High Performance Programmable DMA Controller PDF资料下载

参数资料

| 型号: | IP82C237 |

| 厂商: | HARRIS SEMICONDUCTOR |

| 元件分类: | DMA控制器 |

| 英文描述: | CMOS High Performance Programmable DMA Controller |

| 中文描述: | 4 CHANNEL(S), 8 MHz, DMA CONTROLLER, PDIP40 |

| 文件页数: | 19/25页 |

| 文件大小: | 158K |

| 代理商: | IP82C237 |

4-166

82C237

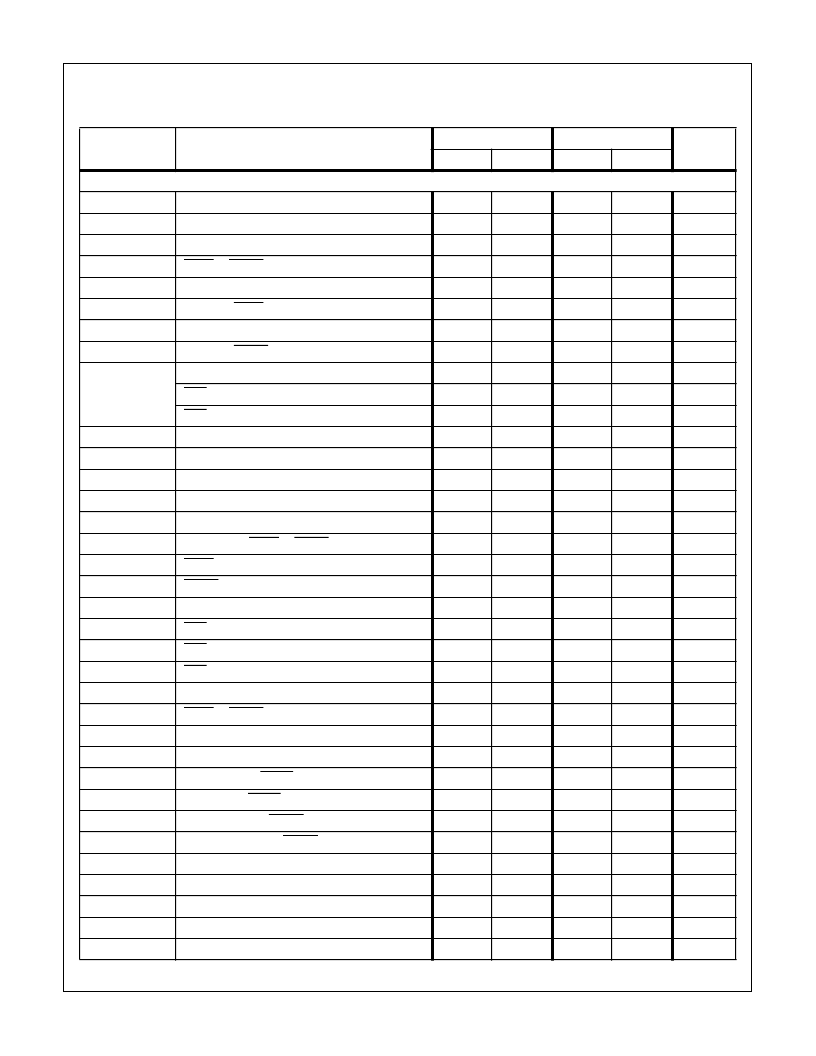

AC Electrical Specifications

V

CC

= +5.0V

±

10%, GND = 0V, T

A

= 0

o

C to +70

o

C (C82C237),

T

A

= -40

o

C to +85

o

C (I82C237),

T

A

= -55

o

C to +125

o

C (M82C237)

SYMBOL

PARAMETER

82C237

82C237-12

UNITS

MIN

MAX

MIN

MAX

DMA (MASTER) MODE

(1)TAEL

AEN HIGH from CLK LOW (S1) Delay Time

-

105

-

50

ns

(2)TAET

AEN LOW from CLK HIGH (SI) Delay Time

-

80

-

50

ns

(3)TAFAB

ADR Active to Float Delay from CLK HIGH

-

55

-

55

ns

(4)TAFC

READ or WRITE Float Delay from CLK HIGH

-

75

-

50

ns

(5)TAFDB

DB Active to Float Delay from CLK HIGH

-

135

-

90

ns

(6)TAHR

ADR from READ HIGH Hold Time

TCY-75

-

TCY-65

-

ns

(7)TAHS

DB from ADSTB LOW Hold Time

TCL-18

-

TCL-18

-

ns

(8)TAHW

ADR from WRITE HIGH Hold Time

TCY-65

-

TCY-50

-

ns

(9)TAK

DACK Valid from CLK LOW Delay Time

-

105

-

69

ns

EOP HIGH from CLK HIGH Delay Time

-

105

-

90

ns

EOP LOW from CLK HIGH Delay Time

-

60

-

35

ns

(10)TASM

ADR Stable from CLK HIGH

-

60

-

50

ns

(11)TASS

DB to ADSTB LOW Setup Time

TCH-20

-

TCH-20

-

ns

(12)TCH

CLK HIGH Time (Transitions 10ns)

55

-

30

-

ns

(13)TCL

CLK LOW Time (Transitions 10ns)

43

-

30

-

ns

(14)TCY

CLK Cycle Time

125

-

80

-

ns

(15)TDCL

CLK HIGH to READ or WRITE LOW Delay

-

130

-

120

ns

(16)TDCTR

READ HIGH from CLK HIGH (S4) Delay Time

-

115

-

80

ns

(17)TDCTW

WRITE HIGH from CLK HIGH (S4) Delay Time

-

80

-

70

ns

(18)TDQ

HRQ Valid from CLK HIGH Delay Time

-

75

-

30

ns

(19)TEPH

EOP Hold Time from CLK LOW (S2)

90

-

50

-

ns

(20)TEPS

EOP LOW to CLK LOW Setup Time

25

-

0

-

ns

(21)TEPW

EOP Pulse Width

135

-

50

-

ns

(22)TFAAB

ADR Valid Delay from CLK HIGH

-

60

-

50

ns

(23)TFAC

READ or WRITE Active from CLK HIGH

-

90

-

50

ns

(24)TFADB

DB Valid Delay from CLK HIGH

-

60

-

45

ns

(25)THS

HLDA Valid to CLK HIGH Setup Time

45

-

10

-

ns

(26)TIDH

Input Data from MEMR HIGH Hold Time

0

-

0

-

ns

(27)TIDS

Input Data to MEMR HIGH Setup Time

90

-

45

-

ns

(28)TODH

Output Data from MEMW HIGH Hold Time

15

-

TCY-50

-

ns

(29)TODV

Output Data Valid to MEMW HIGH

TCY-35

-

TCY-10

-

ns

(30)TQS

DREQ to CLK LOW (SI, S4) Setup Time

0

-

0

-

ns

(31)TRH

CLK to READY LOW Hold Time

20

-

10

-

ns

(32)TRS

READY to CLK LOW Setup Time

35

-

15

-

ns

(33)TCLSH

ADSTB HIGH from CLK LOW Delay Time

-

70

-

70

ns

(34)TCLSL

ADSTB LOW from CLK LOW Delay Time

-

120

-

60

ns

相关PDF资料 |

PDF描述 |

|---|---|

| IP82C237-12 | CMOS High Performance Programmable DMA Controller |

| IP82C54-10Z | CMOS Programmable Intervel Timer |

| IP82C54Z | CMOS Programmable Intervel Timer |

| IP82C54-12 | CMOS Programmable Interval Timer |

| IP82C54 | CMOS Programmable Interval Timer |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IP82C237-12 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:CMOS High Performance Programmable DMA Controller |

| IP82C37A | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Harris Corporation 功能描述: |

| IP82C37A/+ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:DMA Controller |

| IP82C37A-12 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| IP82C37A-5 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Harris Corporation 功能描述: |

发布紧急采购,3分钟左右您将得到回复。