- 您现在的位置:买卖IC网 > PDF目录383110 > IP82C237 (HARRIS SEMICONDUCTOR) CMOS High Performance Programmable DMA Controller PDF资料下载

参数资料

| 型号: | IP82C237 |

| 厂商: | HARRIS SEMICONDUCTOR |

| 元件分类: | DMA控制器 |

| 英文描述: | CMOS High Performance Programmable DMA Controller |

| 中文描述: | 4 CHANNEL(S), 8 MHz, DMA CONTROLLER, PDIP40 |

| 文件页数: | 9/25页 |

| 文件大小: | 158K |

| 代理商: | IP82C237 |

4-156

82C237

Current Word Count Register

- Each channel has a 16-Bit

Current Word Count register. This register determines the

number of transfers to be performed. The actual number of

transfers will be one more than the number programmed in

the Current Word Count register (i.e., programming a count

of 100 will result in 101 transfers). The word count is

decremented after each transfer. When the value in the

register goes from zero to FFFFH, a TC will be generated.

This register is loaded or read in successive 8-bit bytes by

the microprocessor in the Program Condition. See Figure 6

for programming information. Following the end of a DMA

service it may also be reinitialized by an Autoinitialization

back to its original value. Autoinitialization can occur only

when an EOP occurs. If it is not Autoinitialized, this register

will have a count of FFFFH after TC.

Base Address and Base Word Count Registers

- Each

Channel has a pair of Base Address and Base Word Count

registers. These 16-bit registers store the original value of

their associated current registers. During Autoinitialize these

values are used to restore the current registers to their

original values. The base registers are written simulta-

neously with their corresponding current register in 8-bit

bytes in the Program Condition by the microprocessor. See

Figure 6 for programming information. These registers can-

not be read by the microprocessor.

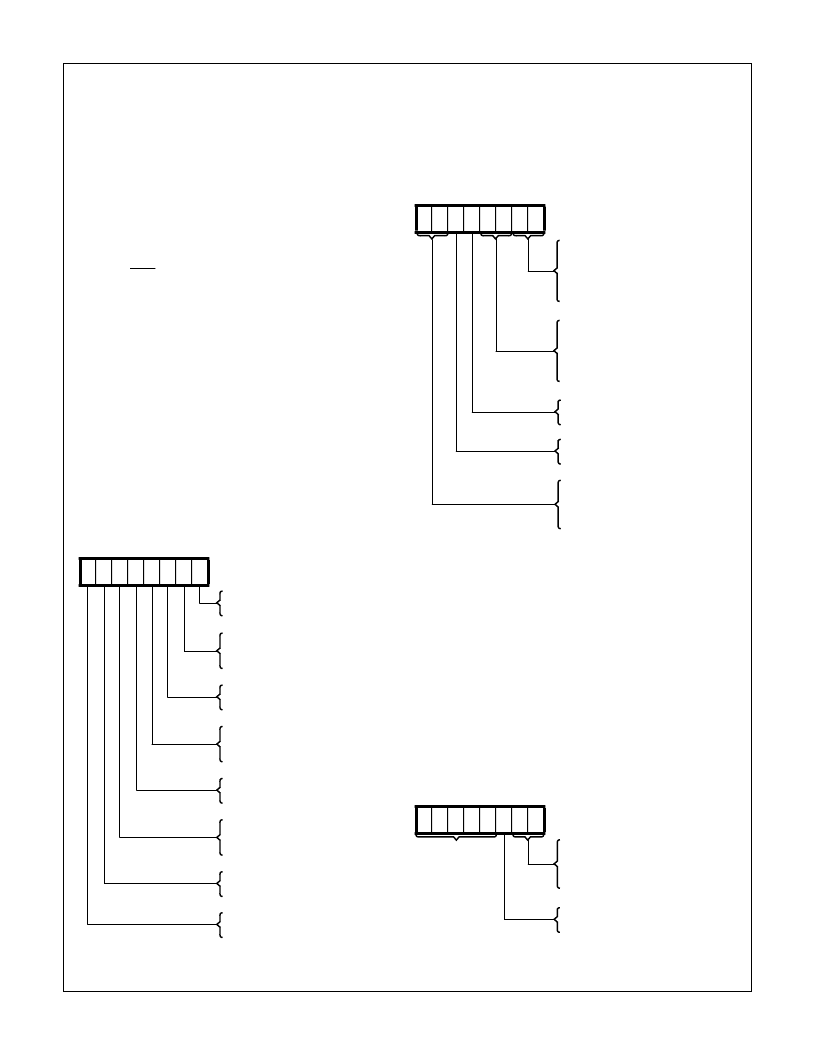

Command Register

- This 8-bit register controls the opera-

tion of the 82C237. It is programmed by the microprocessor

and is cleared by RESET or a Master Clear instruction. The

following diagram lists the function of the Command register

bits. See Figure 4 for Read and Write addresses.

Command Register

Mode Register

- Each channel has a 6-bit Mode register

associated with it. When the register is being written to by

the microprocessor in the Program condition, bits 0 and 1

determine which channel Mode register is to be written.

When the processor reads a Mode register, bits 0 and 1 will

both be ones. See the following diagram and Figure 4 for

Mode register functions and addresses.

Mode Register

Request Register

- The 82C237 can respond to requests

for DMA service which are initiated by software as well as by

a DREQ. Each channel has a request bit associated with it in

the 4-bit Request register. These are non-maskable and

subject to prioritization by the Priority Encoder network.

Each register bit is set or reset separately under software

control. The entire register is cleared by a RESET or Master

Clear instruction. To set or reset a bit, the software loads the

proper form of the data word. See Figure 4 for register

address coding, and the following diagram for Request

register format. A software request for DMA operation can

be made in block or single modes. For memory-to-memory

transfers, the software request for channel 0 should be set.

When reading the Request register, bits 4-7 will always read

as ones, and bits 0-3 will display the request bits of channels

0-3 respectively.

Mode Register

7

6

5

4

3

2

1

0

BIT NUMBER

0

1

Memory-to-memory disable

Memory-to-memory enable

0

1

X

Channel 0 address hold disable

Channel 0 address hold enable

If bit 0 = 0

0

1

Controller enable

Controller disable

0

1

X

Normal timing

Compressed timing

If bit 0 = 1

0

1

Fixed priority

Rotating priority

0

1

X

Late write selection

Extended write selection

If bit 3 = 1

0

1

DREQ sense active high

DREQ sense active low

0

1

DACK sense active low

DACK sense active high

7

6

5

4

3

2

1

0

BIT NUMBER

00

01

10

11

XX

Channel 0 select

Channel 1 select

Channel 2 select

Channel 3 select

Readback

00

01

10

11

XX

Verify transfer

Write transfer

Read transfer

Illegal

If bits 6 and 7 = 11

0

1

Autoinitialization disable

Autoinitialization enable

0

1

Address increment select

Address decrement select

00

01

10

11

Demand mode select

Single mode select

Block mode select

Cascade mode select

7

6

5

4

3

2

1

0

BIT NUMBER

00

01

10

11

Select Channel 0

Select Channel 1

Select Channel 2

Select Channel 3

0

1

Reset request bit

Set request bit

Don’t Care,

Write

Bits 4-7

All Ones,

Read

相关PDF资料 |

PDF描述 |

|---|---|

| IP82C237-12 | CMOS High Performance Programmable DMA Controller |

| IP82C54-10Z | CMOS Programmable Intervel Timer |

| IP82C54Z | CMOS Programmable Intervel Timer |

| IP82C54-12 | CMOS Programmable Interval Timer |

| IP82C54 | CMOS Programmable Interval Timer |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IP82C237-12 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:CMOS High Performance Programmable DMA Controller |

| IP82C37A | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Harris Corporation 功能描述: |

| IP82C37A/+ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:DMA Controller |

| IP82C37A-12 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| IP82C37A-5 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Harris Corporation 功能描述: |

发布紧急采购,3分钟左右您将得到回复。