- 您现在的位置:买卖IC网 > PDF目录383110 > IP82C88 (HARRIS SEMICONDUCTOR) CMOS Bus Controller PDF资料下载

参数资料

| 型号: | IP82C88 |

| 厂商: | HARRIS SEMICONDUCTOR |

| 元件分类: | 外设及接口 |

| 英文描述: | CMOS Bus Controller |

| 中文描述: | 8 MHz, CONTROL AND CMD SIG GEN, PDIP20 |

| 文件页数: | 3/10页 |

| 文件大小: | 129K |

| 代理商: | IP82C88 |

4-335

Functional Description

The command logic decodes the three 80C86, 8086, 80C88,

8088, 80186, 80188 or 8089 status lines (S0, S1, S2) to

determine what command is to be issued (see Table 1).

I/O Bus Mode

The 82C88 is in the I/O Bus mode if the IOB pin is strapped

HIGH. In the I/O Bus mode, all I/O command lines IORC,

IOWC, AIOWC, INTA) are always enabled (i.e., not depen-

dent on AEN). When an I/O command is initiated by the pro-

cessor, the 82C88 immediately activates the command lines

using PDEN and DT/R to control the I/O bus transceiver. The

I/O command lines should not be used to control the system

bus in this configuration because no arbitration is present.

This mode allows one 82C88 Bus Controller to handle two

external busses. No waiting is involved when the CPU wants

to gain access to the I/O bus. Normal memory access

requires a “Bus Ready” signal (AEN LOW) before it will pro-

ceed. It is advantageous to use the IOB mode if I/O or

peripherals dedicated to one processor exist in a multi-pro-

cessor system.

System Bus Mode

The 82C88 is in the System Bus mode if the IOB pin is

strapped LOW. In this mode, no command is issued until a

specified time period after the AEN line is activated (LOW).

This mode assumes bus arbitration logic will inform the bus

controller (on the AEN line) when the bus is free for use.

Both memory and I/O commands wait for bus arbitration.

This mode is used when only one bus exists. Here, both I/O

and memory are shared by more than one processor.

Command Outputs

The advanced write commands are made available to initiate

write procedures early in the machine cycle. This signal can

be used to prevent the processor from entering an unneces-

sary wait state.

AIOWC

12

O

ADVANCED I/O WRITE COMMAND: The AIOWC issues an I/O Write Command earlier in the machine

cycle to give I/O devices an early indication of a write instruction. Its timing is the same as a read com-

mand signal. AIOWC is active LOW.

IOWC

11

O

I/O WRITE COMMAND: This command line instructs an I/O device to read the data on the data bus. The

signal is active LOW.

IORC

13

O

I/O READ COMMAND: This command line instructs an I/O device to drive its data onto the data bus. This

signal is active LOW.

AMWC

8

O

ADVANCED MEMORY WRITE COMMAND: The AMWC issues a memory write command earlier in the

machine cycle to give memory devices an early indication of a write instruction. Its timing is the same as

a read command signal. AMWC is active LOW.

MWTC

9

O

MEMORY WRITE COMMAND: This command line instructs the memory to record the data present on

the data bus. This signal is active LOW.

MRDC

7

O

MEMORY READ COMMAND: This command line instructs the memory to drive its data onto the data

bus. MRDC is active LOW.

INTA

14

O

INTERRUPT ACKNOWLEDGE: This command line tells an interrupting device that its interrupt has been

acknowledged and that it should drive vectoring information onto the data bus. This signal is active LOW.

MCE/PDEN

17

O

This is a dual function pin. MCE (IOB IS TIED LOW) Master Cascade Enable occurs during an interrupt

sequence and serves to read a Cascade Address from a master 82C59A Priority Interrupt Controller onto

the data bus. The MCE signal is active HIGH. PDEN (IOB IS TIED HIGH): Peripheral Data Enable enables

the data bus transceiver for the I/O bus that DEN performs for the system bus. PDEN is active LOW.

Pin Description

(Continued)

PIN

SYMBOL

NUMBER

TYPE

DESCRIPTION

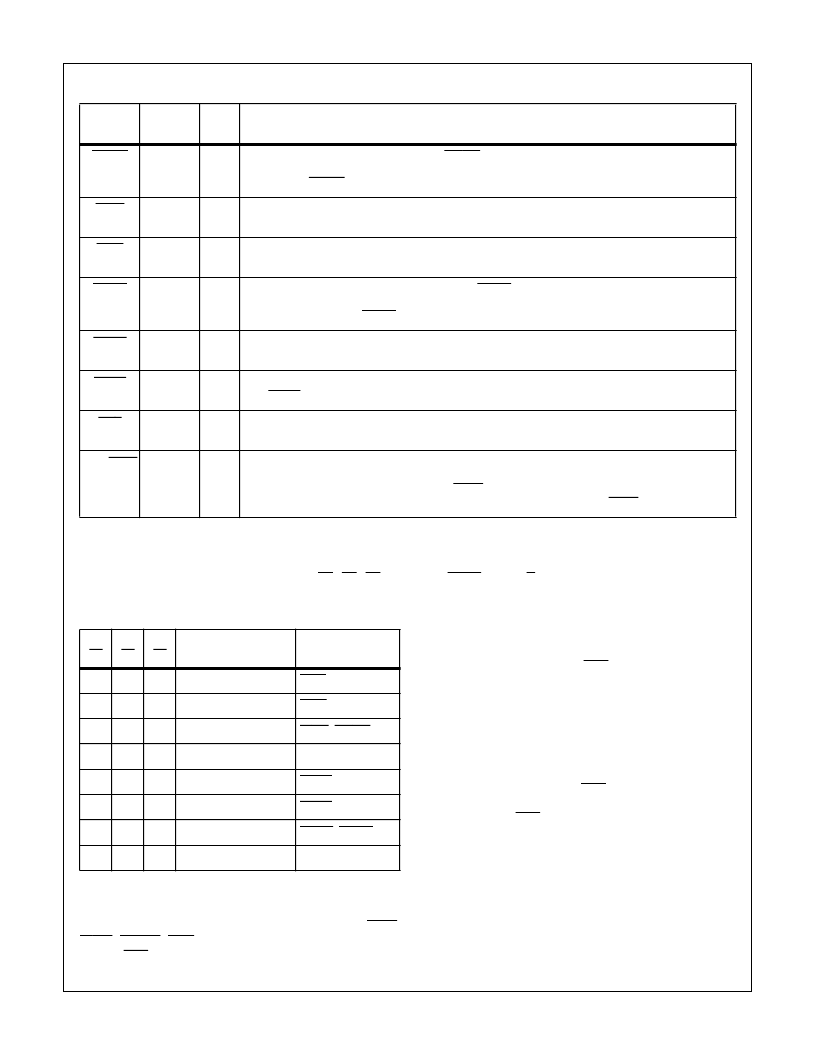

TABLE 1. COMMAND DECODE DEFINITION

S2

S1

S0

PROCESSOR STATE

82C88

COMMAND

0

0

0

Interrupt Acknowledge

INTA

0

0

1

Read I/O Port

IORC

0

1

0

Write I/O Port

IOWC, AIOWC

0

1

1

Halt

None

1

0

0

Code Access

MRDC

1

0

1

Read Memory

MRDC

1

1

0

Write Memory

MWTC, AMWC

1

1

1

Passive

None

82C88

相关PDF资料 |

PDF描述 |

|---|---|

| IP82C89 | CMOS Bus Arbiter |

| IPA60R125CP | CoolMOS Power Transistor |

| IPA60R165CP | CoolMOS Power Transistor |

| IPA60R199CP | CoolMOS Power Transistor |

| IPA60R299CP | CoolMOS Power Transistor |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IP82C89 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| IP8327A-4 | 制造商:AMD 制造商全称:Advanced Micro Devices 功能描述:Multimode DMA Controller |

| IP8327A-4B | 制造商:AMD 制造商全称:Advanced Micro Devices 功能描述:Multimode DMA Controller |

| IP8327A-5 | 制造商:AMD 制造商全称:Advanced Micro Devices 功能描述:Multimode DMA Controller |

| IP8327A-5B | 制造商:AMD 制造商全称:Advanced Micro Devices 功能描述:Multimode DMA Controller |

发布紧急采购,3分钟左右您将得到回复。