- 您现在的位置:买卖IC网 > PDF目录79605 > IQ80C154-12R (ATMEL CORP) 8-BIT, 12 MHz, MICROCONTROLLER, CQFP44 PDF资料下载

参数资料

| 型号: | IQ80C154-12R |

| 厂商: | ATMEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, 12 MHz, MICROCONTROLLER, CQFP44 |

| 封装: | CERAMIC, QFP-44 |

| 文件页数: | 107/109页 |

| 文件大小: | 10824K |

| 代理商: | IQ80C154-12R |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页当前第107页第108页第109页

809

32117D–AVR-01/12

AT32UC3C

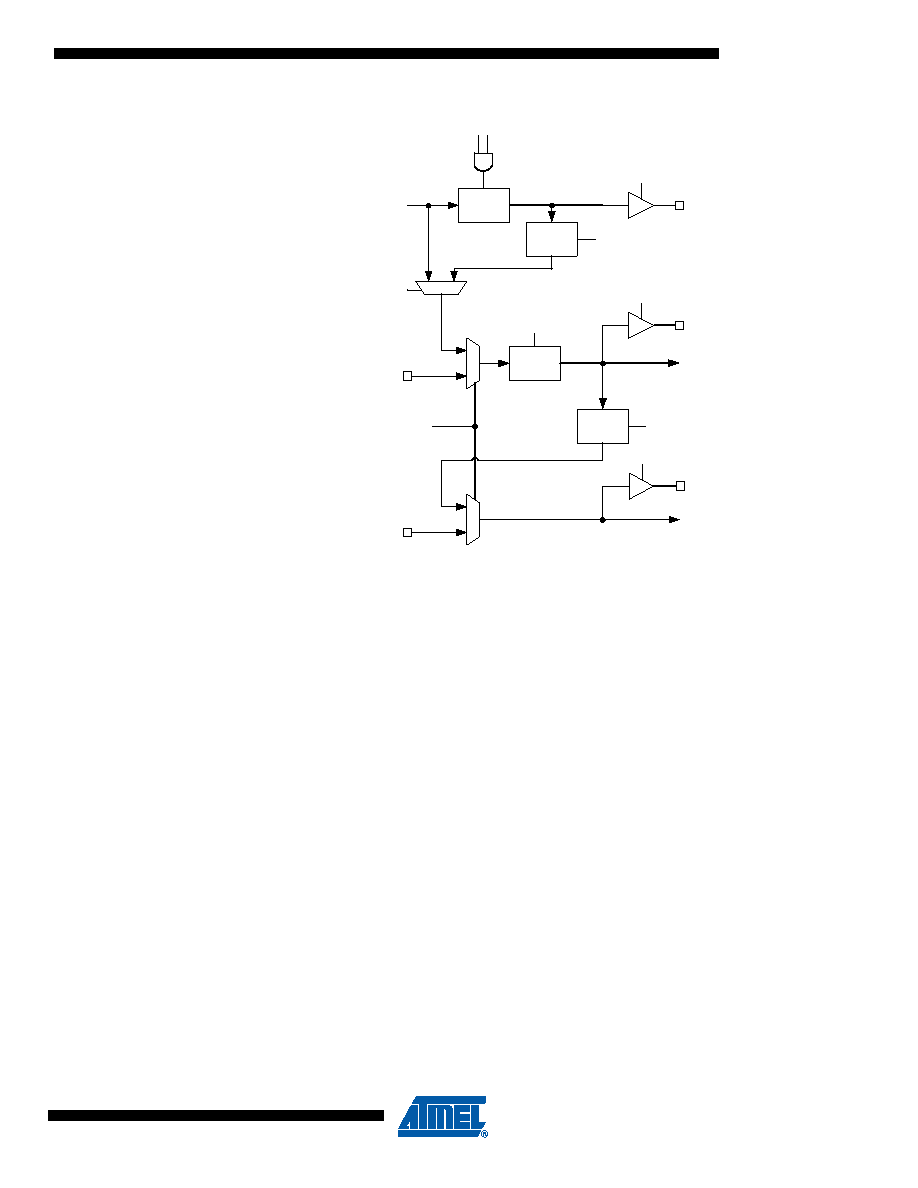

Figure 30-4. IISC Clocks Generation

30.6.7

Mono

When the Transmit Mono (TXMONO) in the Mode Register is set, data written to the left channel

is duplicated to the right output channel. In TDM mode with more than two channels, numbered

from 0, data written to the even-numbered channels is duplicated to the following odd-numbered

channel.

When the Receive Mono (RXMONO) in the Mode Register is set, data received from the left

channel is duplicated to the right channel. In TDM mode with more than two channels, num-

bered from 0, data received from the even-numbered channels is duplicated to the following

odd-numbered channel.

30.6.8

Holding Registers

The IISC user interface includes a Receive Holding Register (RHR) and a Transmit Holding

Register (THR). RHR and THR are used to access audio samples for all audio channels.

When a new data word is available in the RHR register, the Receive Ready bit (RXRDY) in the

Status Register (SR) is set. Reading the RHR register will clear this bit.

A receive overrun condition occurs if a new data word becomes available before the previous

data word has been read from the RHR register. Then, the Receive Overrun bit in the Status

Register will be set and bit i of the RXORCH field in the Status Register is set, where i is the cur-

rent receive channel number.

When the THR register is empty, the Transmit Ready bit (TXRDY) in the Status Register (SR) is

set. Writing into the THR register will clear this bit.

A transmit underrun condition occurs if a new data word needs to be transmitted before it has

been written to the THR register. Then, the Transmit Underrun bit in the Status Register will be

MR.MODE = SLAVE

Clock

divider

MR.DATALENGTH

GCLK_IISC

Clock

enable

Clock

divider

CR.CKEN/CKDIS

MR.IMCKMODE

MR.DATALENGTH

MR.IMCKFS

MR.IMCKMODE

1

0

IMCK pin output

Clock

enable

CR.CKEN/CKDIS

Internal

bit clock

ISCK pin input

1

0

ISCK pin output

Internal

word clock

IWS pin input

1

0

IWS pin output

相关PDF资料 |

PDF描述 |

|---|---|

| IF183C154XXX-12R | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, PQFP44 |

| IT83C154DCXXX-12R | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, PQFP44 |

| IF183C154CXXX-L16 | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP44 |

| IQ83C154CXXX-16 | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, CQFP44 |

| IF283C154DTXXX-L16D | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP44 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IQ80C154-16 | 制造商:TEMIC 制造商全称:TEMIC Semiconductors 功能描述:CMOS 0 to 36 MHz Single Chip 8-bit Microcontroller |

| IQ80C154-20 | 制造商:TEMIC 制造商全称:TEMIC Semiconductors 功能描述:CMOS 0 to 36 MHz Single Chip 8-bit Microcontroller |

| IQ80C154-25 | 制造商:TEMIC 制造商全称:TEMIC Semiconductors 功能描述:CMOS 0 to 36 MHz Single Chip 8-bit Microcontroller |

| IQ80C154-30 | 制造商:TEMIC 制造商全称:TEMIC Semiconductors 功能描述:CMOS 0 to 36 MHz Single Chip 8-bit Microcontroller |

| IQ80C154-36 | 制造商:TEMIC 制造商全称:TEMIC Semiconductors 功能描述:CMOS 0 to 36 MHz Single Chip 8-bit Microcontroller |

发布紧急采购,3分钟左右您将得到回复。