- 您现在的位置:买卖IC网 > PDF目录79605 > IQ80C154-12R (ATMEL CORP) 8-BIT, 12 MHz, MICROCONTROLLER, CQFP44 PDF资料下载

参数资料

| 型号: | IQ80C154-12R |

| 厂商: | ATMEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, 12 MHz, MICROCONTROLLER, CQFP44 |

| 封装: | CERAMIC, QFP-44 |

| 文件页数: | 87/109页 |

| 文件大小: | 10824K |

| 代理商: | IQ80C154-12R |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页当前第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页

64

ATtiny20 [DATASHEET]

8235E–AVR–03/2013

A change of the COM0x[1:0] bits state will have effect at the first Compare Match after the bits are written. For non-PWM

modes, the action can be forced to have immediate effect by using the Force Output Compare bits. See “TCCR0B –

11.7

Modes of Operation

The mode of operation, i.e., the behavior of the Timer/Counter and the Output Compare pins, is defined by the

combination of the Waveform Generation mode (WGM[2:0]) and Compare Output mode (COM0x[1:0]) bits. The

Compare Output mode bits do not affect the counting sequence, while the Waveform Generation mode bits do. The

COM0x[1:0] bits control whether the PWM output generated should be inverted or not (inverted or non-inverted PWM).

For non-PWM modes the COM0x[1:0] bits control whether the output should be set, cleared, or toggled at a Compare

Match (See “Modes of Operation” on page 64).

For detailed timing information refer to Figure 11-8 on page 68, Figure 11-9 on page 68, Figure 11-10 on page 69 and

11.7.1 Normal Mode

The simplest mode of operation is the Normal mode (WGM0[2:0] = 0). In this mode the counting direction is always up

(incrementing), and no counter clear is performed. The counter simply overruns when it passes its maximum 8-bit value

(TOP = 0xFF) and then restarts from the bottom (0x00). In normal operation the Timer/Counter Overflow Flag (TOV0) will

be set in the same timer clock cycle as the TCNT0 becomes zero. The TOV0 Flag in this case behaves like a ninth bit,

except that it is only set, not cleared. However, combined with the timer overflow interrupt that automatically clears the

TOV0 Flag, the timer resolution can be increased by software. There are no special cases to consider in the Normal

mode, a new counter value can be written anytime.

The Output Compare Unit can be used to generate interrupts at some given time. Using the Output Compare to generate

waveforms in Normal mode is not recommended, since this will occupy too much of the CPU time.

11.7.2 Clear Timer on Compare Match (CTC) Mode

In Clear Timer on Compare or CTC mode (WGM0[2:0] = 2), the OCR0A Register is used to manipulate the counter

resolution. In CTC mode the counter is cleared to zero when the counter value (TCNT0) matches the OCR0A. The

OCR0A defines the top value for the counter, hence also its resolution. This mode allows greater control of the Compare

Match output frequency. It also simplifies the operation of counting external events.

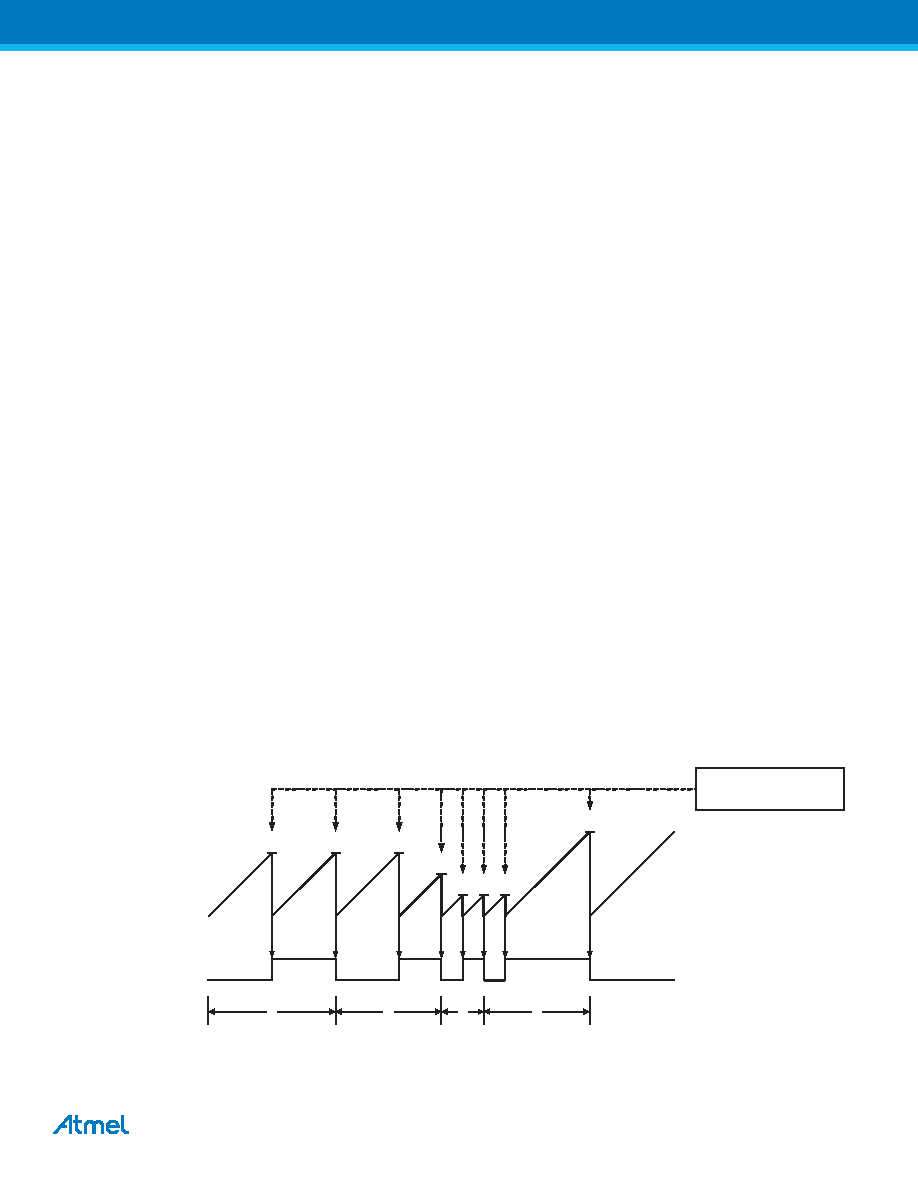

The timing diagram for the CTC mode is shown in Figure 11-5 on page 64. The counter value (TCNT0) increases until a

Compare Match occurs between TCNT0 and OCR0A, and then counter (TCNT0) is cleared.

Figure 11-5. CTC Mode, Timing Diagram

An interrupt can be generated each time the counter value reaches the TOP value by using the OCF0A Flag. If the

interrupt is enabled, the interrupt handler routine can be used for updating the TOP value. However, changing TOP to a

TCNTn

OCnA

(Toggle)

OCnx Interrupt Flag Set

1

4

Period

2

3

(COMnA[1:0] = 1)

相关PDF资料 |

PDF描述 |

|---|---|

| IF183C154XXX-12R | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, PQFP44 |

| IT83C154DCXXX-12R | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, PQFP44 |

| IF183C154CXXX-L16 | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP44 |

| IQ83C154CXXX-16 | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, CQFP44 |

| IF283C154DTXXX-L16D | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP44 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IQ80C154-16 | 制造商:TEMIC 制造商全称:TEMIC Semiconductors 功能描述:CMOS 0 to 36 MHz Single Chip 8-bit Microcontroller |

| IQ80C154-20 | 制造商:TEMIC 制造商全称:TEMIC Semiconductors 功能描述:CMOS 0 to 36 MHz Single Chip 8-bit Microcontroller |

| IQ80C154-25 | 制造商:TEMIC 制造商全称:TEMIC Semiconductors 功能描述:CMOS 0 to 36 MHz Single Chip 8-bit Microcontroller |

| IQ80C154-30 | 制造商:TEMIC 制造商全称:TEMIC Semiconductors 功能描述:CMOS 0 to 36 MHz Single Chip 8-bit Microcontroller |

| IQ80C154-36 | 制造商:TEMIC 制造商全称:TEMIC Semiconductors 功能描述:CMOS 0 to 36 MHz Single Chip 8-bit Microcontroller |

发布紧急采购,3分钟左右您将得到回复。