- 您现在的位置:买卖IC网 > PDF目录377557 > IS61C64B (Integrated Silicon Solution, Inc.) 8K x 8 HIGH-SPEED CMOS STATIC RAM PDF资料下载

参数资料

| 型号: | IS61C64B |

| 厂商: | Integrated Silicon Solution, Inc. |

| 英文描述: | 8K x 8 HIGH-SPEED CMOS STATIC RAM |

| 中文描述: | 8K的× 8高速CMOS静态RAM |

| 文件页数: | 1/9页 |

| 文件大小: | 52K |

| 代理商: | IS61C64B |

IS61C64B

8K x 8 HIGH-SPEED CMOS STATIC RAM

ISSI

Integrated Silicon Solution, Inc. — www.issi.com —

1-800-379-4774

Rev. D

07/01/02

Copyright 2002 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI

assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device

specification before relying on any published information and before placing orders for products.

FEATURES

High-speed access time: 10, 12, and 15 ns

Automatic power-down when chip is

deselected

CMOS low power operation

— 450 mW (typical) operating

— 250 μW (typical) standby

TTL compatible interface levels

Single 5V power supply

Fully static operation: no clock or refresh

required

Three state outputs

One Chip Enables (

CE

) for increased speed

DESCRIPTION

The

ISSI

IS61C64B is a very high-speed, low power,

8192-word by 8-bit static RAM. It is fabricated using

ISSI

's high-

performance CMOS technology. This highly reliable process

coupled with innovative circuit design techniques, yields ac-

cess times as fast as 10 ns with low power consumption.

When

CE

is HIGH (deselected), the device assumes a standby

mode at which the power dissipation can be reduced down to

250 μW (typical) with CMOS input levels.

Easy memory expansion is provided by using one Chip Enable

input,

CE

. The active LOW Write Enable (

WE

) controls both

writing and reading of the memory.

The IS61C64B is packaged in the JEDEC standard 28-pin,

300-mil SOJ, and TSOP.

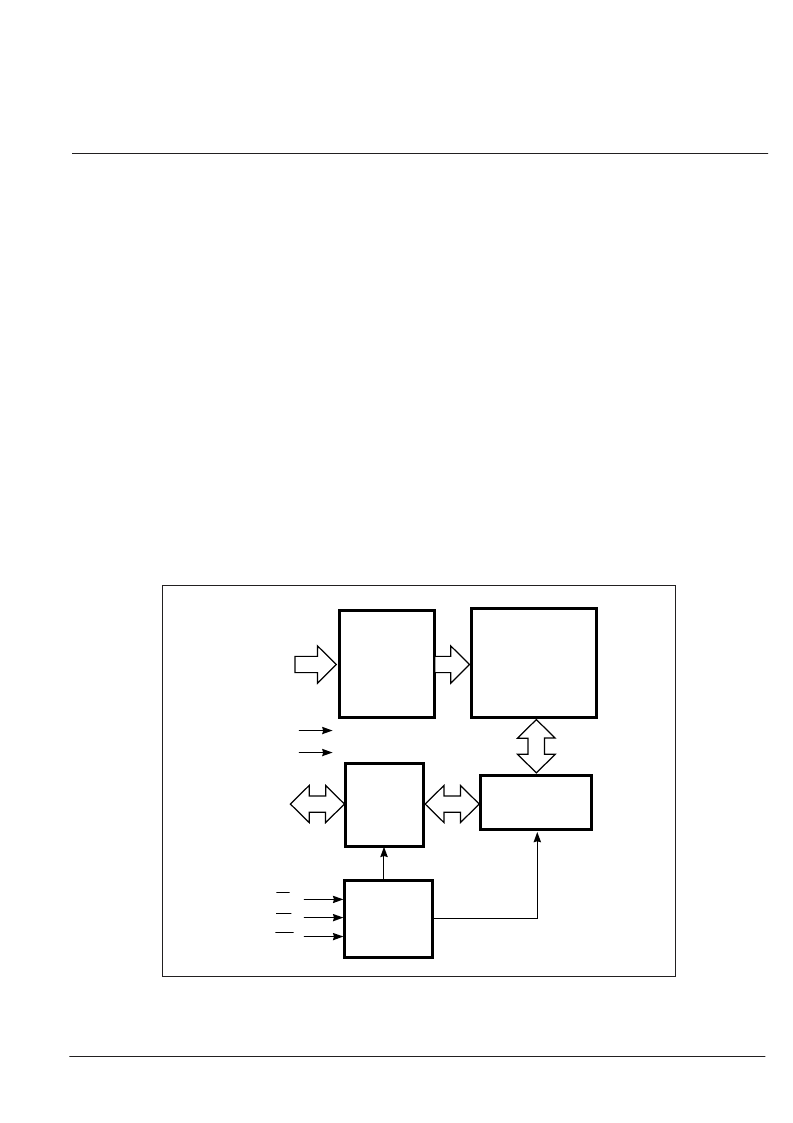

FUNCTIONAL BLOCK DIAGRAM

A0-A12

CE

OE

WE

256 X 256

MEMORY ARRAY

DECODER

COLUMN I/O

CONTROL

CIRCUIT

GND

VCC

I/O

DATA

CIRCUIT

I/O0-I/O7

July 2002

相关PDF资料 |

PDF描述 |

|---|---|

| IS61C67-15N | 16K X 1 HIGH SPEED CMOS STATIC RAM |

| IS61C67-20N | 16K X 1 HIGH SPEED CMOS STATIC RAM |

| IS61C67-25N | 16K X 1 HIGH SPEED CMOS STATIC RAM |

| IS61C67-L15N | 16K X 1 HIGH SPEED CMOS STATIC RAM |

| IS61C67-L20N | 16K X 1 HIGH SPEED CMOS STATIC RAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IS61C64B-10J | 制造商:ISSI 制造商全称:Integrated Silicon Solution, Inc 功能描述:8K x 8 HIGH-SPEED CMOS STATIC RAM |

| IS61C64B-10N | 制造商:未知厂家 制造商全称:未知厂家 功能描述:x8 SRAM |

| IS61C64B-10T | 制造商:未知厂家 制造商全称:未知厂家 功能描述:x8 SRAM |

| IS61C64B-12J | 制造商:ISSI 制造商全称:Integrated Silicon Solution, Inc 功能描述:8K x 8 HIGH-SPEED CMOS STATIC RAM |

| IS61C64B-12N | 制造商:未知厂家 制造商全称:未知厂家 功能描述:x8 SRAM |

发布紧急采购,3分钟左右您将得到回复。