参数资料

| 型号: | ISL12020MIRZ-T7A |

| 厂商: | Intersil |

| 文件页数: | 9/34页 |

| 文件大小: | 0K |

| 描述: | IC RTC/CALENDAR TEMP SNSR 20DFN |

| 产品培训模块: | Solutions for Industrial Control Applications |

| 标准包装: | 250 |

| 类型: | 时钟/日历 |

| 特点: | 警报器,夏令时,闰年,SRAM |

| 存储容量: | 128B |

| 时间格式: | HH:MM:SS(12/24 小时) |

| 数据格式: | YY-MM-DD-dd |

| 接口: | I²C,2 线串口 |

| 电源电压: | 2.7 V ~ 5.5 V |

| 电压 - 电源,电池: | 1.8 V ~ 5.5 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-LFDFN 裸露焊盘 |

| 供应商设备封装: | 20-DFN(5.5x4.0) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页

ISL12020M

17

FN6667.5

December 13, 2011

Interrupt Control Register (INT)

AUTOMATIC RESET BIT (ARST)

This bit enables/disables the automatic reset of the ALM, LVDD,

LBAT85, and LBAT75 status bits only. When ARST bit is set to “1”,

these status bits are reset to “0” after a valid read of the

respective status register (with a valid STOP condition). When the

ARST is cleared to “0”, the user must manually reset the ALM,

LVDD, LBAT85, and LBAT75 bits.

WRITE RTC ENABLE BIT (WRTC)

The WRTC bit enables or disables write capability into the RTC

Timing Registers. The factory default setting of this bit is “0”.

Upon initialization or power-up, the WRTC must be set to “1” to

enable the RTC. Upon the completion of a valid write (STOP), the

RTC starts counting. The RTC internal 1Hz signal is synchronized

to the STOP condition during a valid write cycle.

INTERRUPT/ALARM MODE BIT (IM)

This bit enables/disables the interrupt mode of the alarm

function. When the IM bit is set to “1”, the alarm will operate in

the interrupt mode, where an active low pulse width of 250ms

will appear at the IRQ/FOUT pin when the RTC is triggered by the

alarm, as defined by the alarm registers (0Ch to 11h). When the

IM bit is cleared to “0”, the alarm will operate in standard mode,

where the IRQ/FOUT pin will be set low until the ALM status bit is

cleared to “0”.

FREQUENCY OUTPUT AND INTERRUPT BIT (FOBATB)

This bit enables/disables the IRQ/FOUT pin during

battery-backup mode (i.e. VBAT power source active). When the

FOBATB is set to “1”, the IRQ/FOUT pin is disabled during battery-

backup mode. This means that both the frequency output and

alarm output functions are disabled. When the FOBATB is cleared

to “0”, the IRQ/FOUT pin is enabled during battery-backup mode.

Note that the open drain IRQ/FOUT pin will need a pull-up to the

battery voltage to operate in battery-backup mode.

FREQUENCY OUT CONTROL BITS (FO<3:0>)

These bits enable/disable the frequency output function and

frequency selection. Default for the ISL12020M is FO<3:0> = 1h,

or 32.768kHz output (FOUT is ON). When the frequency mode is

enabled, it will override the alarm mode at the IRQ/FOUT pin.

POWER SUPPLY CONTROL REGISTER (PWR_VDD)

Clear Time Stamp Bit (CLRTS)

This bit clears Time Stamp VDD to Battery (TSV2B) and Time

Stamp Battery to VDD Registers (TSB2V). The default setting is 0

(CLRTS = 0) and the Enabled setting is 1 (CLRTS = 1).

VDD Brownout Trip Voltage BITS (VDDTrip<2:0>)

These bits set the trip level for the VDD alarm, indicating that VDD

has dropped below a preset level. In this event, the LVDD bit in

the Status Register is set to “1”. See Table 7.

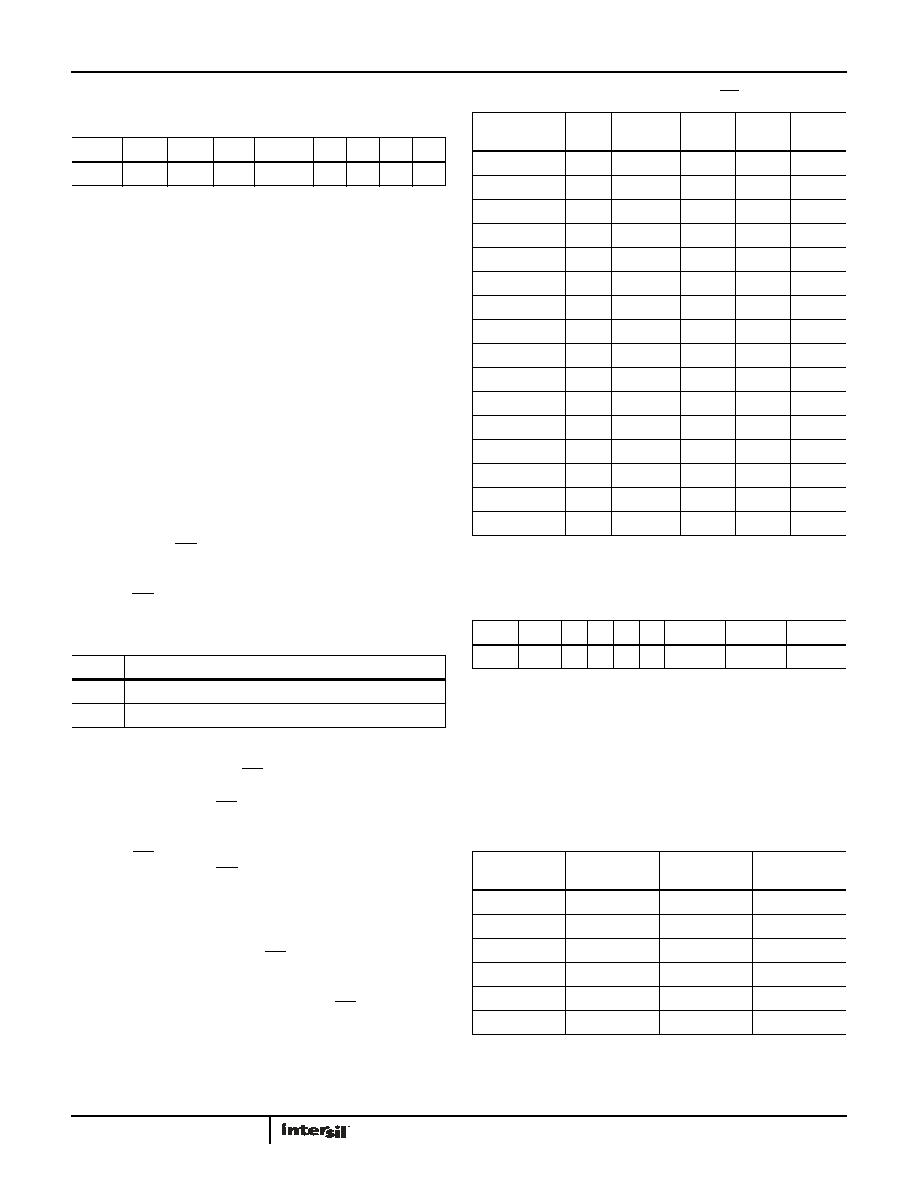

TABLE 3. INTERRUPT CONTROL REGISTER (INT)

ADDR

7

6

5

4

321

0

08h

ARST

WRTC

IM

FOBATB

FO3 FO2 FO1 FO0

TABLE 4.

IM BIT

INTERRUPT/ALARM FREQUENCY

0

Single Time Event Set By Alarm

1

Repetitive/Recurring Time Event Set By Alarm

TABLE 5. FREQUENCY SELECTION OF IRQ/FOUT PIN

FREQUENCY,

FOUT

UNITS

FO3

FO2

FO1

FO0

0

Hz

0

000

32768

Hz

0

001

4096

Hz

0

1

0

1024

Hz

0

011

64

Hz

0

100

32

Hz

0

101

16

Hz

0

110

8

Hz

0

111

4

Hz

1

000

2

Hz

1

001

1

Hz

1

010

1/2

Hz

1

011

1/4

Hz

1

100

1/8

Hz

1

101

1/16

Hz

1

110

1/32

Hz

1

TABLE 6.

ADDR

7

6

5

4

3

2

1

0

09h

CLRTS

0

VDDTrip2 VDDTrip1 VDDTrip0

TABLE 7. VDD TRIP LEVELS

VDDTrip2

VDDTrip1

VDDTrip0

TRIP VOLTAGE

(V)

00

0

2.295

00

1

2.550

01

0

2.805

01

1

3.060

10

0

4.250

10

1

4.675

相关PDF资料 |

PDF描述 |

|---|---|

| ISL12022IBZ-T7A | IC RTC/CALENDAR TEMP SNSR 8SOIC |

| ISL12022MAIBZ | IC RTC/CALENDAR TEMP SNSR 20SOIC |

| ISL12022MIBZ-T7A | IC RTC/CALENDAR TEMP SNSR 20SOIC |

| ISL12022MIBZR5421 | IC RTC/CALENDAR TEMP SNSR 20SOIC |

| ISL12023IVZ | IC RTC/CLDR TEMP SNSR 14-TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL12021 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Real Time Clock with On Chip Temp Compensation 【5ppm |

| ISL12021CVZ | 功能描述:IC RTC LP BATT BACK SRAM 14TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 实时时钟 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- 类型:时钟/日历 特点:警报器,闰年,SRAM 存储容量:- 时间格式:HH:MM:SS(12/24 小时) 数据格式:YY-MM-DD-dd 接口:SPI 电源电压:2 V ~ 5.5 V 电压 - 电源,电池:- 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:8-WDFN 裸露焊盘 供应商设备封装:8-TDFN EP 包装:管件 |

| ISL12021IVZ | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Real Time Clock with On Chip Temp Compensation 【5ppm |

| ISL12022 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Real Time Clock with On Chip ±5ppm Temp Compensation |

| ISL12022IBZ | 功能描述:实时时钟 REAL TIME CLK/CLNDR W/TEMP COMP 8 L RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube |

发布紧急采购,3分钟左右您将得到回复。