- 您现在的位置:买卖IC网 > PDF目录383128 > ISL1219 (Intersil Corporation) Low Power RTC with Battery Backed SRAM and Event Detection(具有电池供电的SRAM和事件检测功能的低功率RTC) PDF资料下载

参数资料

| 型号: | ISL1219 |

| 厂商: | Intersil Corporation |

| 英文描述: | Low Power RTC with Battery Backed SRAM and Event Detection(具有电池供电的SRAM和事件检测功能的低功率RTC) |

| 中文描述: | 低功耗RTC与电池供电的SRAM和事件检测(具有电池供电的SRAM的和事件检测功能的低功率实时时钟) |

| 文件页数: | 14/25页 |

| 文件大小: | 373K |

| 代理商: | ISL1219 |

14

FN6314.1

August 14, 2006

1Hz signal is synchronized to the STOP condition during a

valid write cycle.

CRYSTAL OSCILLATOR ENABLE BIT (XTOSCB)

This bit enables/disables the internal crystal oscillator. When

the XTOSCB is set to “1”, the oscillator is disabled, and the

X1 pin allows for an external 32kHz signal to drive the RTC.

The XTOSCB bit is set to “0” on power up.

AUTO RESET ENABLE BIT (ARST)

This bit enables/disables the automatic reset of the BAT and

ALM, EVT status bits only. When ARST bit is set to “1”, these

status bits are reset to “0” after a valid read of the Status

Register (with a valid STOP condition). When the ARST is

cleared to “0”, the user must manually reset the BAT, ALM,

and EVT bits.

INTERRUPT CONTROL REGISTER (INT)

The interrupt control register contains Frequency Output,

Alarm, and Battery switchover control bits.

NOTE: Writing to register 08h has restrictions. If V

BAT

>V

DD

, then no

byte writes to register 08h are allowed, only page writes beginning

with register 07h. If V

DD

>V

BAT

, then a byte write to register 08h IS

allowed, as well as page writes.

FREQUENCY OUT CONTROL BITS (FO <3:0>)

These bits enable/disable the frequency output function and

select the output frequency at the IRQ/F

OUT

pin. See

Table 8 for frequency selection. When the frequency mode is

enabled, it will override the alarm mode at the IRQ/F

OUT

pin.

FREQUENCY OUTPUT AND INTERRUPT BIT (FOBATB)

This bit enables/disables the F

OUT

/IRQ pin during battery

backup mode (i.e. V

BAT

power source active). When the

FOBATB is set to “1” the F

OUT

/IRQ pin is disabled during

battery backup mode. This means that both the frequency

output and alarm output functions are disabled. When the

FOBATB is cleared to “0”, the F

OUT

/IRQ pin is enabled

during battery backup mode.

LOW POWER MODE BIT (LPMODE)

This bit enables/disables low power mode. With

LPMODE = “0”, the device will be in normal mode and the

V

BAT

supply will be used when V

DD

< V

BAT

- V

BATHYS

and

V

DD

< V

TRIP

. With LPMODE = “1”, the device will be in low

power mode and the V

BAT

supply will be used when

V

DD

< V

BAT

- V

BATHYS

. There is a supply current saving of

about 600nA when using LPMODE = “1” with V

DD

= 5V.

(See Typical Performance Curves: I

DD

vs V

DD

with

LPMODE ON & OFF.)

It should be noted that any writes to the LPMODE bit that

may put the device into Low Power Mode should be avoided

if V

DD

<V

BAT

, as the device will no longer communicate over

the I2C interface (until V

DD

rises above V

BAT

).

ALARM ENABLE BIT (ALME)

This bit enables/disables the alarm function. When the ALME

bit is set to “1”, the alarm function is enabled. When the ALME

is cleared to “0”, the alarm function is disabled. The alarm

function can operate in either a single event alarm or a periodic

interrupt alarm (see IM bit).

NOTE: When the frequency output mode is enabled, the alarm function

is disabled.

INTERRUPT/ALARM MODE BIT (IM)

This bit enables/disables the interrupt mode of the alarm

function. When the IM bit is set to “1”, the alarm will operate

in the interrupt mode, where an active low pulse width of

250ms will appear at the IRQ/F

OUT

pin when the RTC is

triggered by the alarm as defined by the alarm registers (0Ch

to 11h). When the IM bit is cleared to “0”, the alarm will

operate in standard mode, where the IRQ/F

OUT

pin will be

tied low until the ALM status bit is cleared to “0”.

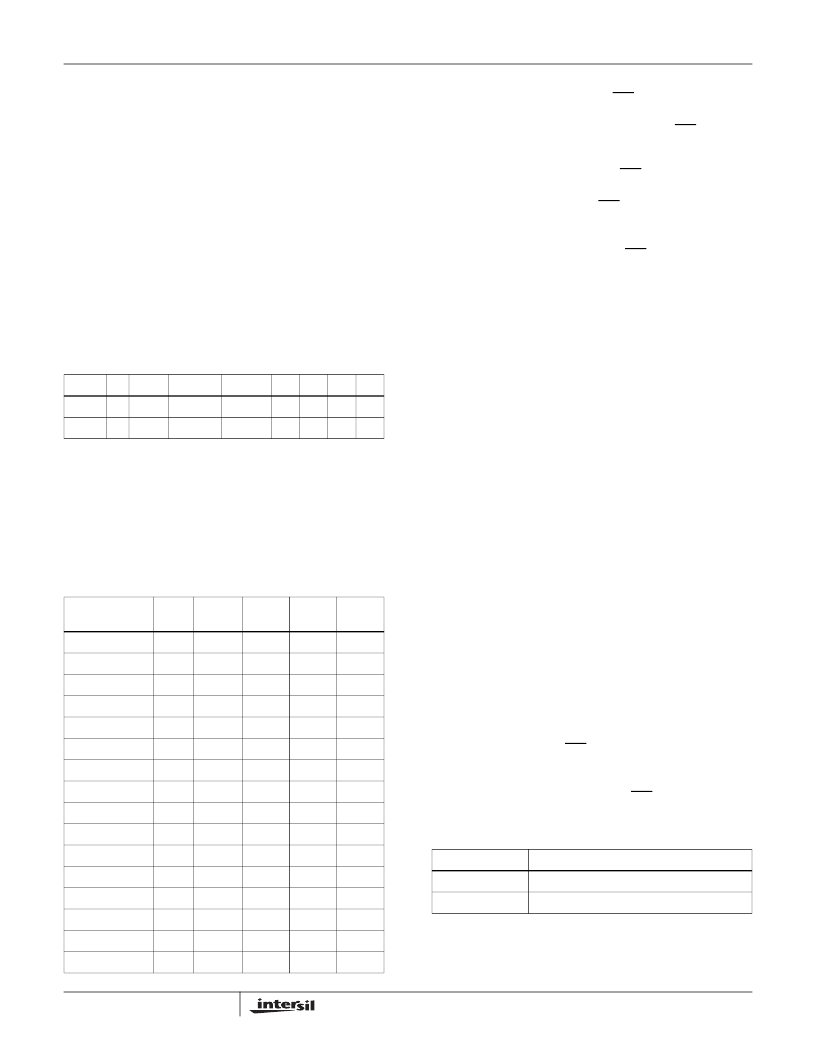

TABLE 7. INTERRUPT CONTROL REGISTER (INT)

ADDR

7

6

5

4

3

2

1

0

08h

IM

ALME

LPMODE FOBATB FO3 FO2 FO1 FO0

Default

0

0

0

0

0

0

0

0

TABLE 8. FREQUENCY SELECTION OF F

OUT

PIN

FREQUENCY,

F

OUT

UNITS

FO3

FO2

FO1

FO0

0

Hz

0

0

0

0

32768

Hz

0

0

0

1

4096

Hz

0

0

1

0

1024

Hz

0

0

1

1

64

Hz

0

1

0

0

32

Hz

0

1

0

1

16

Hz

0

1

1

0

8

Hz

0

1

1

1

4

Hz

1

0

0

0

2

Hz

1

0

0

1

1

Hz

1

0

1

0

1/2

Hz

1

0

1

1

1/4

Hz

1

1

0

0

1/8

Hz

1

1

0

1

1/16

Hz

1

1

1

0

1/32

Hz

1

1

1

1

TABLE 9.

IM BIT

INTERRUPT/ALARM FREQUENCY

0

Single Time Event Set By Alarm

1

Repetitive/Recurring Time Event Set By Alarm

ISL1219

相关PDF资料 |

PDF描述 |

|---|---|

| ISL1220 | Low Power RTC with 8 Bytes of Battery Backed SRAM and Separate FOUT(具有电池供电的8位SRAM和独立输出的低功率RTC) |

| ISL1221 | Low Power RTC with Battery Backed SRAM and Event Detection(具有电池供电的SRAM和事件检测功能的低功率RTC) |

| ISL21009 | High Voltage Input Precision, Low Noise FGA Voltage References(高电压输入精度,低噪声FGA电压基准) |

| ISL21400 | Programmable Temperature Slope Voltage Reference(可编程温度斜率电压基准) |

| ISL22316 | Low Noise, Low Power I2C Bus, 128 Taps(低噪声,低功率,I2C总线, 128抽头电位器) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL1219IUZ | 功能描述:实时时钟 REAL TIME CLKRTC IN RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube |

| ISL1219IUZ-T | 功能描述:实时时钟 REAL TIME CLKRTC IN RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube |

| ISL1220 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:I2C㈢ Real Time Clock/Calendar with Frequency Output |

| ISL1220IUZ | 功能描述:实时时钟 REAL TIME CLKRTC IN RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube |

| ISL1220IUZ-T | 功能描述:实时时钟 REAL TIME CLKRTC IN RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube |

发布紧急采购,3分钟左右您将得到回复。