- 您现在的位置:买卖IC网 > Datasheet目录333 > ISL6210CRZ (Intersil)IC MOSFET DRIVER DUAL SYNC 16QFN Datasheet资料下载

参数资料

| 型号: | ISL6210CRZ |

| 厂商: | Intersil |

| 文件页数: | 7/10页 |

| 文件大小: | 0K |

| 描述: | IC MOSFET DRIVER DUAL SYNC 16QFN |

| 标准包装: | 75 |

| 配置: | 高端和低端,同步 |

| 输入类型: | PWM |

| 延迟时间: | 26ns |

| 电流 - 峰: | 2A |

| 配置数: | 2 |

| 输出数: | 4 |

| 高端电压 - 最大(自引导启动): | 36V |

| 电源电压: | 4.5 V ~ 5.5 V |

| 工作温度: | -10°C ~ 100°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-VQFN 裸露焊盘 |

| 供应商设备封装: | 16-QFN-EP(4x4) |

| 包装: | 管件 |

�� �

�

�

�ISL6210�

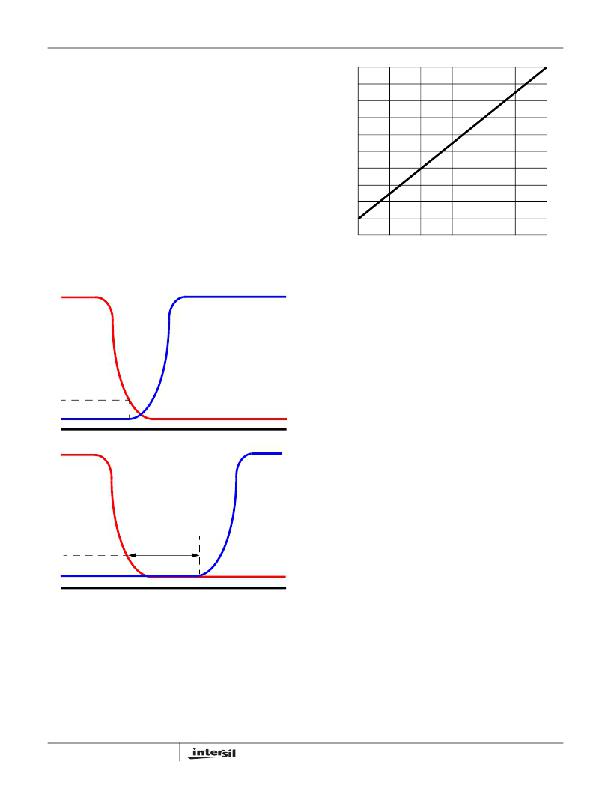

�During� turn-off� of� the� lower� MOSFET,� the� LGATE� voltage� is�

�monitored� until� it� reaches� a� 1V� threshold,� at� which� time� the�

�UGATE� is� released� to� rise.� Adaptive� shoot-through� circuitry�

�monitors� the� upper� MOSFET� gate-to-source� voltage� during�

�UGATE� turn-off.� Once� the� upper� MOSFET� gate-to-source�

�voltage� has� dropped� below� a� threshold� of� 1V,� the� LGATE� is�

�allowed� to� rise.�

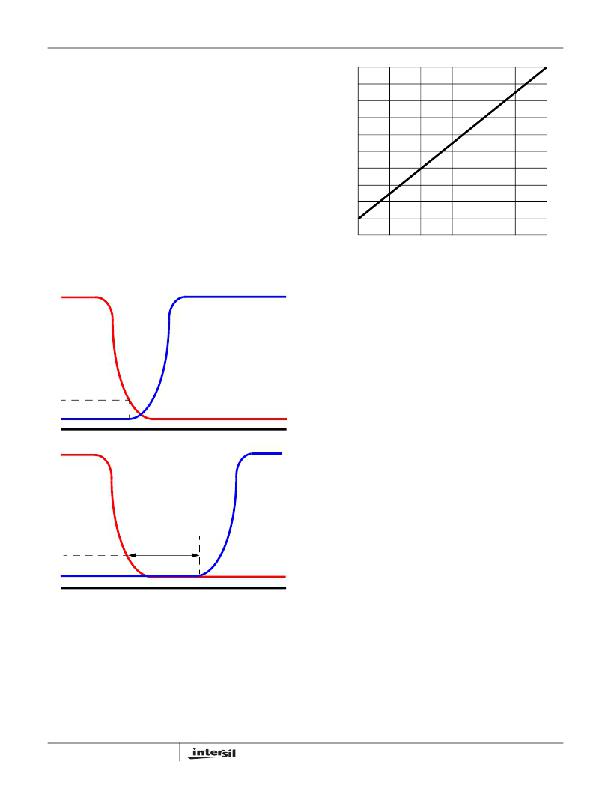

�50�

�45�

�40�

�35�

�30�

�In� addition� to� gate� threshold� monitoring,� a� programmable�

�delay� between� MOSFET� switching� can� be� accomplished� by�

�placing� a� resistor� in� series� with� the� FCCM� input.� This� delay�

�allows� for� maximum� design� flexibility� over� MOSFET�

�selection.� The� delay� can� be� programmed� from� 5ns� to� 50ns�

�and� is� obtained� from� the� absolute� value� of� the� current�

�flowing� into� the� FCCM� pin.� If� no� resistor� is� used,� the�

�25�

�20�

�15�

�10�

�5�

�t� DELAY�

�minimum� 5ns� delay� is� selected.� Gate� threshold� monitoring� is�

�not� affected� by� the� addition� or� removal� of� the� additional�

�dead-time.� Refer� to� Figure� 2� and� Figure� 3� for� more� detail.�

�0�

�0�

�167�

�333�

�500�

�R� DELAY� (k� Ω� )�

�667�

�833�

�1000�

�FIGURE� 3.� ISL6210� PROGRAMMABLE� DEAD-TIME� vs�

�FCCM� =� VCC� or� GND�

�DELAY� RESISTOR�

�GATE� A�

�GATE B�

�The� equation� governing� the� dead-time� seen� in� Figure� 3� is�

�expressed� in� Equation� 1:�

�t� DELAY� (� ns� )� =� [� 0.045� ×� R� DELAY� (� k� Ω� )� ]� +� 5ns�

�(EQ.� 1)�

�The� equation� can� be� rewritten� to� solve� for� R� DELAY� as�

�(� t� DELAY� (� ns� )� –� 5ns� )�

�1V�

�ADAPTIVE� SHOOT-THROUGH�

�PROTECTION�

�follows:�

�0.045�

�R� DELAY� (� k� Ω� )� =� ----------------------------------------------------�

�(EQ.� 2)�

�Internal� Bootstrap� Diode�

�This� driver� features� an� internal� bootstrap� diode.� Simply�

�FCCM� =� RESISTOR� to� VCC� or� GND�

�adding� an� external� capacitor� across� the� BOOT� and� PHASE�

�C� BOOT_CAP� ≥� --------------------------------------�

�Q� G1� ?� PVCC�

�Q� GATE� =� ------------------------------------� ?� N� Q1�

�1V�

�GATE� A�

�ADAPTIVE� PROTECTION�

�WITH� DELAY�

�t� DELAY� =� 5n� -� 50ns�

�GATE� B�

�pins� completes� the� bootstrap� circuit.�

�Equation� 3� helps� select� a� proper� bootstrap� capacitor� size:�

�Q� GATE�

�Δ� V� BOOT_CAP�

�(EQ.� 3)�

�V� GS1�

�where� Q� G1� is� the� amount� of� gate� charge� per� upper� MOSFET�

�at� V� GS1� gate-source� voltage� and� N� Q1� is� the� number� of�

�control� MOSFETs.� The� Δ� V� BOOT_CAP� term� is� defined� as� the�

�allowable� droop� in� the� rail� of� the� upper� gate� drive.�

�FIGURE� 2.� PROGRAMMABLE� DEAD-TIME�

�7�

�As� an� example,� suppose� two� IRLR7821� FETs� are� chosen� as�

�the� upper� MOSFETs.� The� gate� charge,� Q� G� ,� from� the� data�

�sheet� is� 10nC� at� 4.5V� (V� GS� )� gate-source� voltage.� Then� the�

�Q� GATE� is� calculated� to� be� 22nC� at� PVCC� level.� We� will�

�assume� a� 200mV� droop� in� drive� voltage� over� the� PWM�

�cycle.� We� find� that� a� bootstrap� capacitance� of� at� least�

�0.110μF� is� required.� The� next� larger� standard� value�

�capacitance� is� 0.22μF.� A� good� quality� ceramic� capacitor� is�

�recommended.�

�FN6392.1�

�December� 9,� 2008�

�相关PDF资料 |

PDF描述 |

|---|---|

| ISL6244EVAL1 | EVALUATION BOARD ISL6244 |

| ISL6261AEVAL1Z | EVAL BOARD 1 FOR ISL6261A |

| ISL6261EVAL1Z | EVAL BOARD FOR ISL6261 1 QFN |

| ISL6271AEVAL1 | EVALUATION BOARD FOR ISL6271A |

| ISL62882CEVAL2Z | EVAL BOARD FOR ISL62882C |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6210CRZ-T | 功能描述:IC MOSFET DRIVER DUAL SYNC 16QFN RoHS:是 类别:集成电路 (IC) >> PMIC - MOSFET,电桥驱动器 - 外部开关 系列:- 标准包装:50 系列:- 配置:高端 输入类型:非反相 延迟时间:200ns 电流 - 峰:250mA 配置数:1 输出数:1 高端电压 - 最大(自引导启动):600V 电源电压:12 V ~ 20 V 工作温度:-40°C ~ 125°C 安装类型:通孔 封装/外壳:8-DIP(0.300",7.62mm) 供应商设备封装:8-DIP 包装:管件 其它名称:*IR2127 |

| ISL6211 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Crusoe⑩ Processor Core-Voltage Regulator |

| ISL6211CA | 制造商:Rochester Electronics LLC 功能描述:CPU REGULATOR FOR TRANSMETA,SINGLE CORE - Bulk 制造商:Intersil Corporation 功能描述: |

| ISL6211CA WAF | 制造商:Intersil Corporation 功能描述: |

| ISL6211CA-T | 制造商:Rochester Electronics LLC 功能描述:CPU REGULATOR FOR TRANSMETA,SINGLE CORE - Tape and Reel 制造商:Intersil Corporation 功能描述: |

发布紧急采购,3分钟左右您将得到回复。