- 您现在的位置:买卖IC网 > Datasheet目录333 > ISL6261EVAL1Z (Intersil)EVAL BOARD FOR ISL6261 1 QFN Datasheet资料下载

参数资料

| 型号: | ISL6261EVAL1Z |

| 厂商: | Intersil |

| 文件页数: | 11/34页 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD FOR ISL6261 1 QFN |

| 标准包装: | 1 |

| 系列: | * |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页

�� �

�

�

�ISL6261�

�Theory� of� Operation�

�The� ISL6261� is� a� single-phase� regulator� implementing� Intel� ?�

�IMVP-6� ?� protocol� and� includes� an� integrated� gate� driver� for�

�VDD�

�reduced� system� cost� and� board� area.� The� ISL6261� IMVP-6� ?�

�solution� provides� optimum� steady� state� and� transient�

�performance� for� microprocessor� core� voltage� regulation�

�applications� up� to� 25A.� Implementation� of� diode� emulation�

�mode� (DEM)� operation� further� enhances� system� efficiency.�

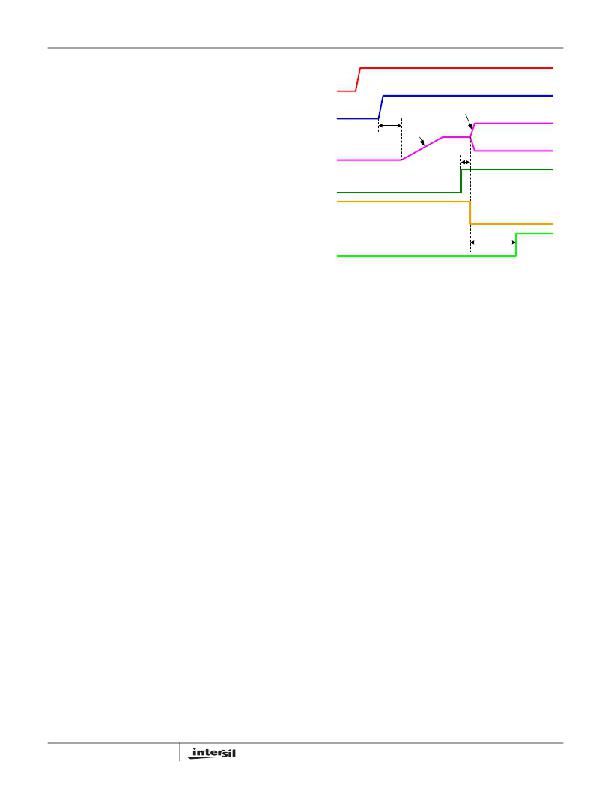

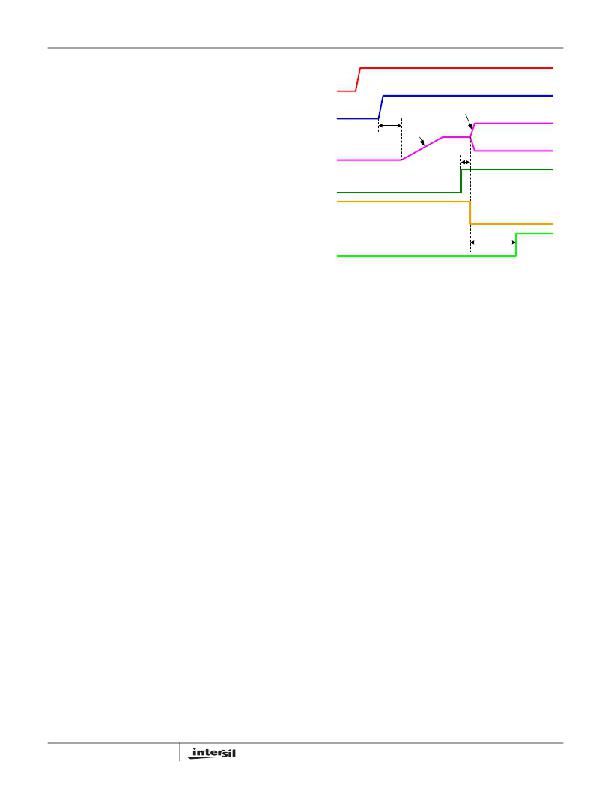

�VR_ON�

�100us�

�SOFT� &VO�

�10mV/us�

�2mV/us� Vboot�

�The� heart� of� the� ISL6261� is� the� patented�

�R� 3�

�Technology?,�

�~20us�

�Intersil’s� Robust� Ripple� Regulator� modulator.� The� R� 3� ?�

�modulator� combines� the� best� features� of� fixed� frequency� and�

�hysteretic� PWM� controllers� while� eliminating� many� of� their�

�shortcomings.� The� ISL6261� modulator� internally� synthesizes�

�an� analog� of� the� inductor� ripple� current� and� uses� hysteretic�

�comparators� on� those� signals� to� establish� PWM� pulses.�

�Operating� on� the� large-amplitude� and� noise-free� synthesized�

�signals� allows� the� ISL6261� to� achieve� lower� output� ripple�

�and� lower� phase� jitter� than� either� conventional� hysteretic� or�

�fixed� frequency� PWM� controllers.� Unlike� conventional�

�hysteretic� converters,� the� ISL6261� has� an� error� amplifier� that�

�allows� the� controller� to� maintain� 0.5%� voltage� regulation�

�accuracy� throughout� the� VID� range� from� 0.75V� to� 1.5V.�

�The� hysteretic� window� voltage� is� with� respect� to� the� error�

�amplifier� output.� Therefore� the� load� current� transient� results�

�in� increased� switching� frequency,� which� gives� the� R� 3� ?�

�regulator� a� faster� response� than� conventional� fixed�

�frequency� PWM� regulators.�

�Start-up� Timing�

�With� the� controller� ’s� VDD� pin� voltage� above� the� POR�

�threshold,� the� start-up� sequence� begins� when� VR_ON�

�exceeds� the� 3.3V� logic� HIGH� threshold.� In� approximately�

�100� μ� s,� SOFT� and� VO� start� ramping� to� the� boot� voltage� of�

�1.2V.� At� startup,� the� regulator� always� operates� in� continuous�

�current� mode� (CCM),� regardless� of� the� control� signals.�

�During� this� interval,� the� SOFT� cap� is� charged� by� a� 41� μ� A�

�current� source.� If� the� SOFT� capacitor� is� 20nF,� the� SOFT�

�ramp� will� be� 2mV/� μ� s� for� a� soft-start� time� of� 600� μ� s.� Once� VO�

�is� within� 10%� of� the� boot� voltage� and� PGD_IN� is� HIGH� for� six�

�PWM� cycles� (20μs� for� 300kHz� switching� frequency),�

�CLK_EN#� is� pulled� LOW,� and� the� SOFT� cap� is�

�charged/discharged� by� approximate� 200μA� and� VO� slews� at�

�10mV/� μ� s� to� the� voltage� set� by� the� VID� pins.� In� approximately�

�7ms,� PGOOD� is� asserted� HIGH.� Figure� 4� shows� typical�

�startup� timing.�

�PGD_IN� Latch�

�It� should� be� noted� that� PGD_IN� going� low� will� cause� the�

�converter� to� latch� off.� Toggling� PGD_IN� won’t� clear� the� latch.�

�Toggling� VR_ON� will� clear� it.� This� feature� allows� the�

�converter� to� respond� to� other� system� voltage� outages�

�immediately.�

�11�

�PGD_IN�

�CLK_EN#�

�~7ms�

�IMVP-VI� PGOOD�

�FIGURE� 4.� SOFT-START� WAVEFORMS� USING� A� 20nF� SOFT�

�CAPACITOR�

�Static� Operation�

�After� the� startup� sequence,� the� output� voltage� will� be�

�regulated� to� the� value� set� by� the� VID� inputs� per� Table� 1,�

�which� is� presented� in� the� lntel� ?� IMVP-6� ?� specification.� The�

�ISL6261� regulates� the� output� voltage� with� ±0.5%� accuracy�

�over� the� range� of� 0.7V� to� 1.5V.�

�A� true� differential� amplifier� remotely� senses� the� core� voltage�

�to� precisely� control� the� voltage� at� the� microprocessor� die.�

�VSEN� and� RTN� pins� are� the� inputs� to� the� differential�

�amplifier.�

�As� the� load� current� increases� from� zero,� the� output� voltage�

�droops� from� the� VID� value� proportionally� to� achieve� the�

�IMVP-6� ?� load� line.� The� ISL6261� can� sense� the� inductor�

�current� through� the� intrinsic� series� resistance� of� the�

�inductors,� as� shown� in� Figure� 2,� or� through� a� precise� resistor�

�in� series� with� the� inductor,� as� shown� in� Figure� 3.� The�

�inductor� current� information� is� fed� to� the� VSUM� pin,� which� is�

�the� non-inverting� input� to� the� droop� amplifier.� The� DROOP�

�pin� is� the� output� of� the� droop� amplifier,� and� DROOP-VO�

�voltage� is� a� high-bandwidth� analog� representation� of� the�

�inductor� current.� This� voltage� is� used� as� an� input� to� a�

�differential� amplifier� to� achieve� the� IMVP-6� ?� load� line,� and�

�also� as� the� input� to� the� overcurrent� protection� circuit.�

�When� using� inductor� DCR� current� sensing,� an� NTC�

�thermistor� is� used� to� compensate� the� positive� temperature�

�coefficient� of� the� copper� winding� resistance� to� maintain� the�

�load-line� accuracy.�

�The� switching� frequency� of� the� ISL6261� controller� is� set� by�

�the� resistor� R� FSET� between� pins� VW� and� COMP,� as� shown� in�

�Figures� 2� and� 3.�

�FN9251.1�

�September� 27,� 2006�

�相关PDF资料 |

PDF描述 |

|---|---|

| ISL6271AEVAL1 | EVALUATION BOARD FOR ISL6271A |

| ISL62882CEVAL2Z | EVAL BOARD FOR ISL62882C |

| ISL62883CEVAL2Z | EVAL BOARD FOR ISL62883C |

| ISL62883EVAL2Z | EVALUATION BOARD FOR ISL62883 |

| ISL62884CEVAL2Z | EVAL BOARD FOR ISL62884C |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6261IR7Z | 功能描述:IC DC/DC BUCK CTRLR 1PH 48-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,000 系列:- 应用:电源,ICERA E400,E450 输入电压:4.1 V ~ 5.5 V 输出数:10 输出电压:可编程 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:42-WFBGA,WLCSP 供应商设备封装:42-WLP 包装:带卷 (TR) |

| ISL6261IR7Z-T | 功能描述:IC DC/DC BUCK CTRLR 1PH 48-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 标准包装:43 系列:- 应用:控制器,Intel VR11 输入电压:5 V ~ 12 V 输出数:1 输出电压:0.5 V ~ 1.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-VFQFN 裸露焊盘 供应商设备封装:48-QFN(7x7) 包装:管件 |

| ISL6261IRZ | 功能描述:IC DC/DC BUCK CTRLR 1PH 40-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,000 系列:- 应用:电源,ICERA E400,E450 输入电压:4.1 V ~ 5.5 V 输出数:10 输出电压:可编程 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:42-WFBGA,WLCSP 供应商设备封装:42-WLP 包装:带卷 (TR) |

| ISL6261IRZ-T | 功能描述:IC DC/DC BUCK CTRLR 1PH 40-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 标准包装:43 系列:- 应用:控制器,Intel VR11 输入电压:5 V ~ 12 V 输出数:1 输出电压:0.5 V ~ 1.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-VFQFN 裸露焊盘 供应商设备封装:48-QFN(7x7) 包装:管件 |

| ISL6262A | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Two-Phase Core Controller Santa Rosa, IMVP-6 |

发布紧急采购,3分钟左右您将得到回复。