参数资料

| 型号: | ISL6263CHRZ-T |

| 厂商: | Intersil |

| 文件页数: | 13/18页 |

| 文件大小: | 0K |

| 描述: | IC VOLT REG 1PH 5BIT VID 32-QFN |

| 标准包装: | 6,000 |

| 应用: | 转换器,GPU 内核电源 |

| 输入电压: | 5 V ~ 25 V |

| 输出数: | 1 |

| 输出电压: | 0.41 V ~ 1.29 V |

| 工作温度: | -10°C ~ 100°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-VFQFN 裸露焊盘 |

| 供应商设备封装: | 32-QFN(5x5) |

| 包装: | 带卷 (TR) |

�� �

�

�

�ISL6263C�

�Internal� Bootstrap� Diode�

�The� ISL6263C� has� an� integrated� boot-strap� Schottky� diode�

�connected� from� the� PVCC� pin� to� the� BOOT� pin.� Simply�

�adding� an� external� capacitor� across� the� BOOT� and� PHASE�

�pins� completes� the� bootstrap� circuit.�

�2.0�

�output� voltage� is� commanded� to� rise,� and� discharging�

�C� SOFT� when� the� output� voltage� is� commanded� to� fall.�

�The� GPU� voltage� regulator� may� require� a� minimum� voltage�

�slew� rate,� which� will� be� guaranteed� by� the� value� of� C� SOFT� .�

�For� example,� if� the� regulator� requires� 10mV/μs� slew� rate,� the�

�value� of� C� SOFT� can� be� calculated� using� Equation� 4:�

�C� SOFT� =� -------------------------� =� ------------------� =� 0.018� μ� F�

�?� ----------------� ?�

�1.8�

�1.6�

�1.4�

�I� DVIDmin� 180� μ� A�

�?� μ� s� ?�

�10mV� 10K�

�(EQ.� 4)�

�1.2�

�1.0�

�0.8�

�0.6�

�0.4�

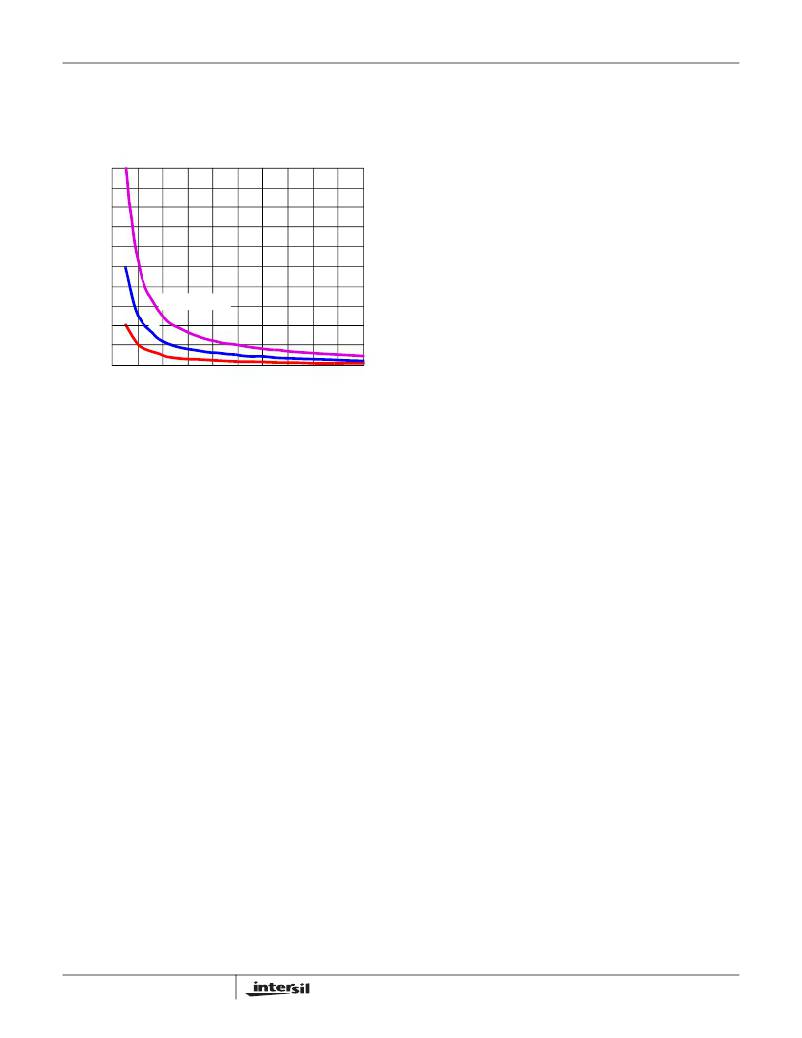

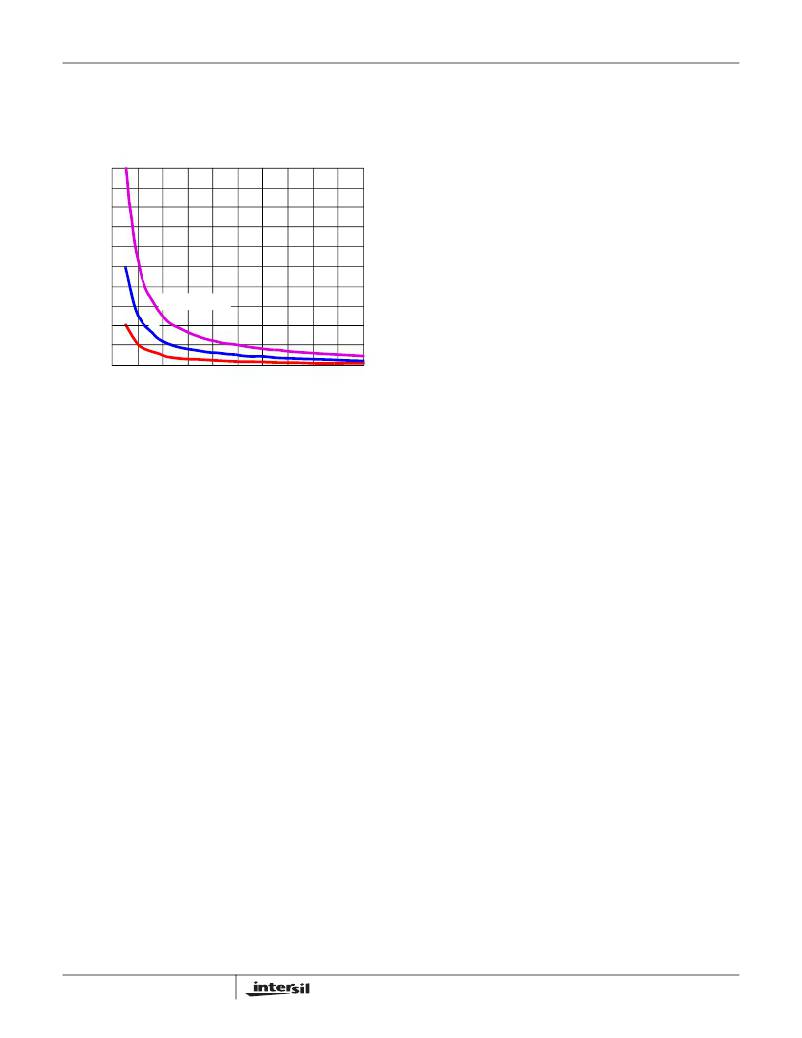

�Q� GATE� =� 100nC�

�I� DVID� is� the� soft-dynamic� VID� current� source,� and� its�

�minimum� value� is� specified� in� the� “Electrical� Specifications”�

�table� on� page� 5.� Choosing� the� next� lower� standard�

�component� value� of� 0.015μF� will� guarantee� 10mV/μs� slew�

�rate.� This� choice� of� C� SOFT� controls� the� startup� slew-rate� as�

�well.� One� should� expect� the� output� voltage� during� soft-start�

�20nC�

�dV� SOFT� I� SS� 42� μ� A� 2.8mV�

�0.015� μ� F�

�μ� s�

�-----------------------� =� -------------------� =� -----------------------� ≈� ------------------�

�C� SOFT�

�0.2�

�0.0�

�0.0� 0.1�

�0.2�

�0.3�

�0.4� 0.5� 0.6�

�Δ� V� BOOT_CAP� (V)�

�0.7�

�0.8�

�0.9�

�1.0�

�to� slew� to� the� voltage� commanded� by� the� VID� settings� at� a�

�nominal� rate� given� by� Equation� 5:�

�dt� (EQ.� 5)�

�FIGURE� 7.� BOOTSTRAP� CAPACITANCE� vs� BOOT� RIPPLE�

�VOLTAGE�

�The� minimum� value� of� the� bootstrap� capacitor� can� be�

�Note� that� the� slew� rate� is� the� average� rate� of� change�

�between� the� initial� and� final� voltage� values.�

�C� BOOT� ≥� ------------------------�

�calculated� using� Equation� 3:�

�Q� GATE�

�Δ� V� BOOT�

�(EQ.� 3)�

�It� is� worth� it� to� mention� that� the� surge� current� charges� the�

�output� capacitors� when� the� output� voltage� is� commanded� to�

�rise.� This� surge� current� could� be� high� enough� to� trigger� the�

�OC� protection� circuit� if� the� voltage� slew� rate� is� too� high,�

�where� Q� GATE� is� the� amount� of� gate� charge� required� to� fully�

�charge� the� gate� of� the� upper� MOSFET.� The� Δ� V� BOOT� term� is�

�defined� as� the� allowable� droop� in� the� rail� of� the� upper� drive.�

�As� an� example,� suppose� an� upper� MOSFET� has� a� gate�

�charge,� Q� GATE� ,� of� 25nC� at� 5V� and� also� assume� the� droop� in�

�the� drive� voltage� at� the� end� of� a� PWM� cycle� is� 200mV.� One�

�will� find� that� a� bootstrap� capacitance� of� at� least� 0.125μF� is�

�required.� The� next� larger� standard� value� capacitance� is�

�0.15μF.� A� good� quality� ceramic� capacitor� is� recommended.�

�Soft-Start� and� Soft� Dynamic� VID� Slew� Rates�

�The� output� voltage� of� the� converter� tracks� V� SOFT,� the�

�voltage� across� the� SOFT� and� VSS� pins.� Shown� in� Figure� 1,�

�the� SOFT� pin� is� connected� to� the� output� of� the� VID� DAC�

�through� the� unidirectional� soft-start� current� source� I� SS� or� the�

�bidirectional� soft-dynamic� VID� current� source� I� DVID� ,� and� the�

�non-inverting� input� of� the� error� amplifier.� Current� is� sourced�

�from� the� SOFT� pin� when� I� SS� is� active.� The� SOFT� pin� can�

�both� source� and� sink� current� when� I� DVID� is� active.� The�

�soft-start� capacitor� C� SOFT� changes� voltage� at� a� rate�

�proportional� to� I� SS� or� I� DVID� .� The� ISL6263C� automatically�

�selects� I� SS� for� the� soft-start� sequence� so� that� the� inrush�

�current� through� the� output� capacitors� is� maintained� below�

�the� OCP� threshold.� Once� soft-start� has� completed,� I� DVID� is�

�automatically� selected� for� output� voltage� changes�

�commanded� by� the� VID� inputs,� charging� C� SOFT� when� the�

�13�

�or/and� the� output� capacitance� is� too� large.� The� overcurrent�

�set� point� should� guarantee� the� VID� code� transition�

�successful.�

�RBIAS� Current� Reference�

�The� RBIAS� pin� is� internally� connected� to� a� 1.545V� reference�

�through� a� 3k� ?� resistance.� A� bias� current� is� established� by�

�connecting� a� ±1%� tolerance,� 150k� ?� resistor� between� the�

�RBIAS� and� VSS� pins.� This� bias� current� is� mirrored,� creating� the�

�reference� current� I� OCSET� that� is� sourced� from� the� OCSET� pin.�

�Do� not� connect� any� other� components� to� this� pin,� as� they� will�

�have� a� negative� impact� on� the� performance� of� the� IC.�

�Setting� the� PWM� Switching� Frequency�

�The� R� 3� modulator� scheme� is� not� a� fixed-frequency�

�architecture,� lacking� a� fixed-frequency� clock� signal� to�

�produce� PWM.� The� switching� frequency� increases� during�

�the� application� of� a� load� to� improve� transient� performance.�

�The� static� PWM� frequency� varies� slightly� depending� on� the�

�input� voltage,� output� voltage,� and� output� current,� but� this�

�variation� is� normally� less� than� 10%� in� continuous� conduction�

�mode.�

�Refer� to� Figure� 2� and� find� that� resistor� R� FSET� is� connected�

�between� the� V� W� and� COMP� pins.� A� current� is� sourced� from�

�VW� through� R� FSET� creating� the� synthetic� ripple� window�

�voltage� signal� V� W� ,� which� determines� the� PWM� switching�

�frequency.� The� relationship� between� the� resistance� of� R� FSET�

�FN6745.1�

�July� 8,� 2010�

�相关PDF资料 |

PDF描述 |

|---|---|

| ISL6263CRZ | IC VREG CORE 5BIT 1PHASE 32-QFN |

| ISL6263DHRZ | IC VREG 3BIT 1PHASE 32-QFN |

| ISL6264CRZ | IC CORE CTRLR TWO-PHASE 40-QFN |

| ISL6265AHRTZ-T | IC CTRLR MULTI-OUTPUT 48-TQFN |

| ISL6265CHRTZ | IC CTRLR MULTI-OUTPUT 48TQFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6263CRZ | 功能描述:直流/直流开关调节器 1 PHS INT DC/DC BUCK CNTRLR FOR INTEL RoHS:否 制造商:International Rectifier 最大输入电压:21 V 开关频率:1.5 MHz 输出电压:0.5 V to 0.86 V 输出电流:4 A 输出端数量: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:PQFN 4 x 5 |

| ISL6263CRZ-T | 功能描述:直流/直流开关调节器 1 PHS INT DC/DC BUCK CNTRLR FOR INTEL RoHS:否 制造商:International Rectifier 最大输入电压:21 V 开关频率:1.5 MHz 输出电压:0.5 V to 0.86 V 输出电流:4 A 输出端数量: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:PQFN 4 x 5 |

| ISL6263DEVAL1Z | 功能描述:EVAL BAORD 1 FOR ISL6263D RoHS:是 类别:编程器,开发系统 >> 评估板 - DC/DC 与 AC/DC(离线)SMPS 系列:* 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:True Shutdown™ 主要目的:DC/DC,步升 输出及类型:1,非隔离 功率 - 输出:- 输出电压:- 电流 - 输出:1A 输入电压:2.5 V ~ 5.5 V 稳压器拓扑结构:升压 频率 - 开关:3MHz 板类型:完全填充 已供物品:板 已用 IC / 零件:MAX8969 |

| ISL6263DHRZ | 功能描述:IC VREG 3BIT 1PHASE 32-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,000 系列:- 应用:电源,ICERA E400,E450 输入电压:4.1 V ~ 5.5 V 输出数:10 输出电压:可编程 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:42-WFBGA,WLCSP 供应商设备封装:42-WLP 包装:带卷 (TR) |

| ISL6263DHRZ-T | 功能描述:IC VREG 3BIT 1PHASE 32-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 标准包装:43 系列:- 应用:控制器,Intel VR11 输入电压:5 V ~ 12 V 输出数:1 输出电压:0.5 V ~ 1.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-VFQFN 裸露焊盘 供应商设备封装:48-QFN(7x7) 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。