参数资料

| 型号: | ISL62881HRTZ |

| 厂商: | Intersil |

| 文件页数: | 22/35页 |

| 文件大小: | 0K |

| 描述: | IC REG PWM SGL PHASE 28TQFN |

| 标准包装: | 75 |

| 应用: | 控制器,Intel IMVP-6.5? |

| 输入电压: | 5 V ~ 25 V |

| 输出数: | 1 |

| 输出电压: | 0.013 V ~ 1.5 V |

| 工作温度: | -10°C ~ 100°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-WFQFN 裸露焊盘 |

| 供应商设备封装: | 28-TQFN-EP(4x4) |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页当前第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页

�� �

�

�

�ISL62881,� ISL62881B�

�T2(s)� is� the� voltage� loop� gain� with� closed� droop� loop.� It� has� more�

�meaning� of� output� voltage� response.�

�Design� the� compensator� to� get� stable� T1(s)� and� T2(s)� with�

�sufficient� phase� margin,� and� output� impedance� equal� or� smaller�

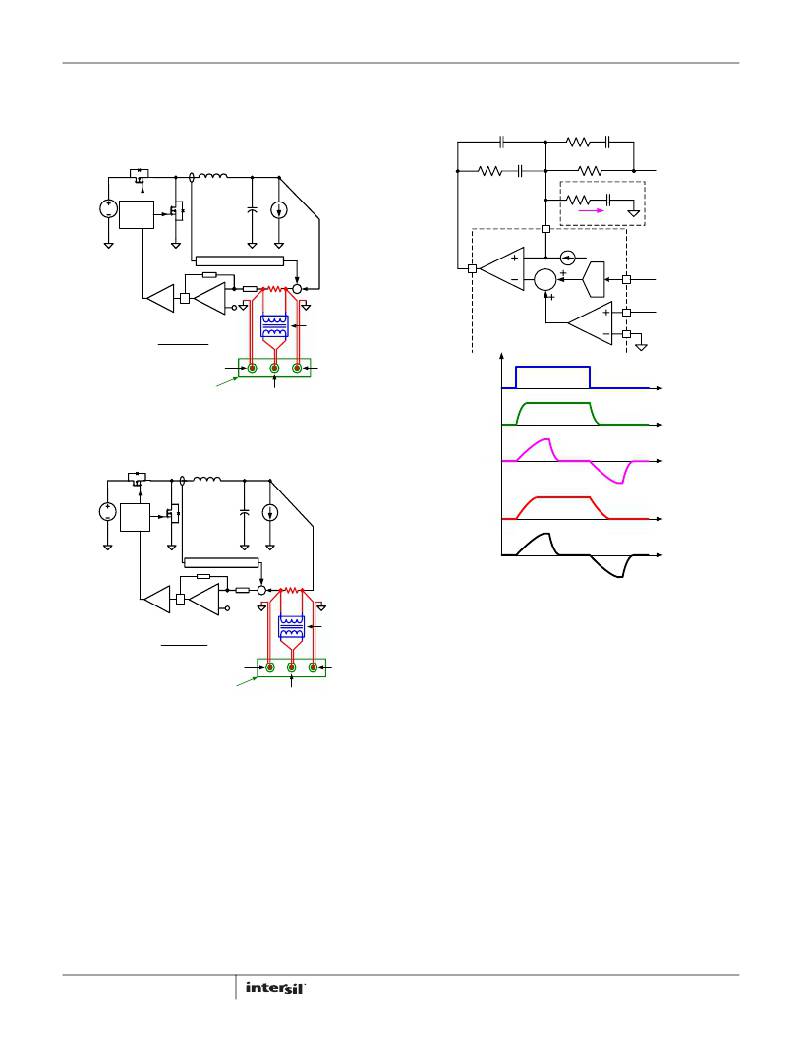

�Optional� Slew� Rate� Compensation� Circuit� For�

�1-Tick� VID� Transition�

�than� the� load� line� slope.�

�Q1�

�L�

�V� O�

�Rdroop�

�C� vid�

�R� vid�

�Vcore�

�V� IN�

�GATE� Q2�

�DRIVER�

�C� OUT�

�I� O�

�FB�

�I� vid�

�OPTIONAL�

�Idroop_vid�

�LOAD� LINE� SLOPE�

�20� Ω�

�-�

�+�

�+�

�COMP�

�E/A�

�Σ� VDAC� DAC�

�VIDs�

�VID<0:6>�

�LOOP� GAIN� =�

�MOD�

�COMP�

�CHANNEL� B�

�CHANNEL� A�

�EA�

�+�

�VID�

�ISOLATION�

�TRANSFORMER�

�INTERNAL� TO�

�IC�

�X1�

�RTN�

�VSS�

�VSS� SENSE�

�CHANNEL� A�

�CHANNEL� B�

�NETWORK�

�ANALYZER�

�EXCITATION� OUTPUT�

�VID<0:6>�

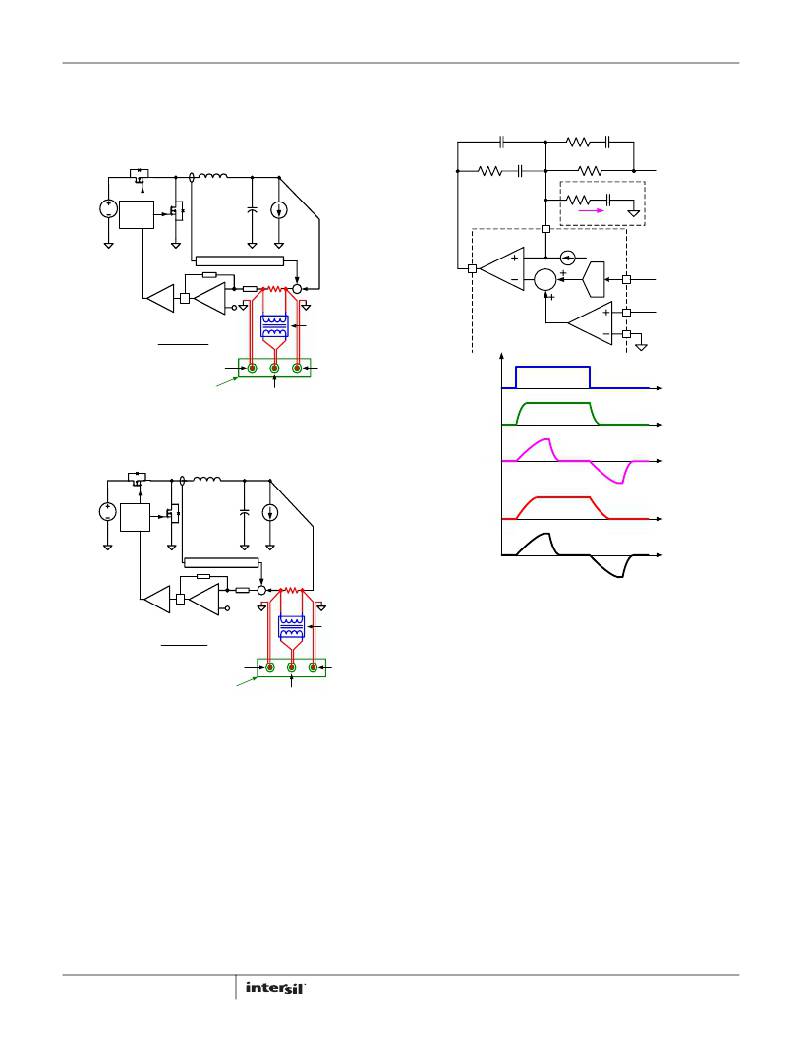

�FIGURE� 21.� LOOP� GAIN� T1(s)� MEASUREMENT� SET-UP�

�Vfb�

�Ivid�

�Q1�

�L�

�V� O�

�V� IN�

�GATE� Q2�

�DRIVER�

�C� OUT�

�I� O�

�Vcore�

�Idroop_vid�

�LOAD� LINE� SLOPE�

�MOD� EA�

�CHANNEL� B�

�LOOP� GAIN� =�

�CHANNEL� A�

�-�

�COMP� +�

�VID�

�+�

�+�

�20� Ω�

�ISOLATION�

�TRANSFORMER�

�FIGURE� 23.� OPTIONAL� SLEW� RATE� COMPENSATION� CIRCUIT�

�FOR1-TICK� VID� TRANSITION�

�During� a� large� VID� transition,� the� DAC� steps� through� the� VIDs� at� a�

�controlled� slew� rate� of� 2.5μs� or� 1.25μs� per� tick� (12.5mV),� controlling�

�output� voltage� V� core� slew� rate� at� 5mV/μs� or� 10mV/μs.�

�CHANNEL� A�

�NETWORK�

�ANALYZER�

�EXCITATION� OUTPUT�

�CHANNEL� B�

�Figure� 23� shows� the� waveforms� of� 1-tick� VID� transition.� During�

�1-tick� VID� transition,� the� DAC� output� changes� at� approximately�

�15mV/μs� slew� rate,� but� the� DAC� cannot� step� through� multiple�

�FIGURE� 22.� LOOP� GAIN� T2(s)� MEASUREMENT� SET-UP�

�VIDs� to� control� the� slew� rate.� Instead,� the� control� loop� response�

�speed� determines� V� core� slew� rate.� Ideally,� V� core� will� follow� the� FB�

�pin� voltage� slew� rate.� However,� the� controller� senses� the� inductor�

�current� increase� during� the� up� transition,� as� the� I� droop_vid�

�waveform� shows,� and� will� droop� the� output� voltage� V� core�

�accordingly,� making� V� core� slew� rate� slow.� Similar� behavior� occurs�

�during� the� down� transition.�

�To� control� V� core� slew� rate� during� 1-tick� VID� transition,� one� can�

�add� the� R� vid� -C� vid� branch,� whose� current� I� vid� cancels� I� droop_vid� .�

�When� V� core� increases,� the� time� domain� expression� of� the�

��?� ?�

�–� t�

�C� out� � LL�

�dV� core�

�� LL� ?�

�C�

�I� droop� (� t� )� =� ------------------------� ×� ------------------� ×� ?� 1� –� e� out� ?�

�R� droop�

�22�

�-------------------------�

�?� ?�

�(EQ.� 31)�

�FN6924.3�

�June� 16,� 2011�

�相关PDF资料 |

PDF描述 |

|---|---|

| ISL62882IRTZ | IC REG PWM 2PHASE BUCK 40TQFN |

| ISL62883IRTZ | IC REG PWM 3PHASE BUCK 40TQFN |

| ISL6292BCRZ | IC CHARGER LI-ION 4.2V 4X4 16QFN |

| ISL6294IBZ | IC CHRGR LI-ION SGL 8-SOIC |

| ISL6306IRZ | IC REG CTRLR BUCK PWM VM 40-QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL62881HRTZ-T | 功能描述:直流/直流开关调节器 1 PHS PWM BUCKG FOR MICROPROCESR PWR SUP RoHS:否 制造商:International Rectifier 最大输入电压:21 V 开关频率:1.5 MHz 输出电压:0.5 V to 0.86 V 输出电流:4 A 输出端数量: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:PQFN 4 x 5 |

| ISL62882 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Multiphase PWM Regulator for IMVP-6.5 Mobile CPUs and GPUs |

| ISL62882B | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Multiphase PWM Regulator for IMVP-6.5 Mobile CPUs and GPUs |

| ISL62882BHRTZ | 功能描述:直流/直流开关调节器 2 PHS PWM BUCKG FOR MICROPROC PWR SUP RoHS:否 制造商:International Rectifier 最大输入电压:21 V 开关频率:1.5 MHz 输出电压:0.5 V to 0.86 V 输出电流:4 A 输出端数量: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:PQFN 4 x 5 |

| ISL62882BHRTZR5411 | 制造商:Intersil Corporation 功能描述: |

发布紧急采购,3分钟左右您将得到回复。