参数资料

| 型号: | ISL6323BCRZ-T |

| 厂商: | Intersil |

| 文件页数: | 24/36页 |

| 文件大小: | 0K |

| 描述: | IC PWM CTRLR SYNC BUCK DL 48QFN |

| 标准包装: | 4,000 |

| 应用: | 控制器,AMD SVI |

| 输入电压: | 5 V ~ 12 V |

| 输出数: | 2 |

| 输出电压: | 最高 2V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-VFQFN 裸露焊盘 |

| 供应商设备封装: | 48-QFN(7x7) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

�� �

�

�

�ISL6323B�

�level� that� might� cause� damage� to� the� load.� The� lower�

�MOSFETs� remain� driven� ON� until� VDIFF� falls� below� 400mV.�

�The� ISL6323B� will� continue� to� protect� the� load� in� this� fashion� as�

�long� as� the� overvoltage� condition� recurs.� Once� an� overvoltage�

�condition� ends� the� ISL6323B� latches� off,� and� must� be� reset� by�

�toggling� POR,� before� a� soft-start� can� be� re-initiated.�

�Undervoltage� Detection�

�The� undervoltage� threshold� is� set� at� VDAC� -� 300mV� typical.�

�When� the� output� voltage� (VSEN-RGND)� is� below� the�

�undervoltage� threshold,� PGOOD� gets� pulled� low.� No� other�

�action� is� taken� by� the� controller.� PGOOD� will� return� high� if�

�the� output� voltage� rises� above� VDAC� -� 250mV� typical.�

�Open� Sense� Line� Protection�

�-�

�OCL�

�+�

�142μA�

�I� 1�

�In� the� case� that� either� of� the� remote� sense� lines,� VSEN� or�

�GND,� become� open,� the� ISL6323B� is� designed� to� detect� this�

�and� shut� down� the� controller.� This� event� is� detected� by�

�100μA�

�-�

�OCP�

�REPEAT� FOR� EACH�

�CORE� CHANNEL�

�monitoring� small� currents� that� are� fed� out� the� VSEN� and� RGND�

�pins.� In� the� event� of� an� open� sense� line� fault,� the� controller� will�

�I� NB�

�+�

�-�

�100μA�

�continue� to� remain� off� until� the� fault� goes� away,� at� which� point�

�OCP�

�the� controller� will� re-initiate� a� soft-start� sequence.�

�NB� ONLY�

�+�

�I� AVG�

�CORE� ONLY�

�Overcurrent� Protection�

�The� ISL6323B� takes� advantage� of� the� proportionality� between�

�SOFT-START,� FAULT�

�AND� CONTROL� LOGIC�

�the� load� current� and� the� average� current,� I� AVG� ,� to� detect� an�

�overcurrent� condition.� See� “Continuous� Current� Sampling”� on�

�page� 14� and� “Channel-Current� Balance”� on� page� 15� for� more�

�NB� ONLY�

�+�

�detail� on� how� the� average� current� is� measured.� Once� the�

�1.8V�

�-�

�OVP�

�average� current� exceeds� 100μA,� a� comparator� triggers� the�

�converter� to� begin� overcurrent� protection� procedures.� The�

�ISEN_NB+�

�-�

�UV�

�Core� regulator� and� the� North� Bridge� regulator� have� the� same�

�type� of� overcurrent� protection.�

�+�

�DAC� -� 300mV�

�The� overcurrent� trip� threshold� is� dictated� by� the� DCR� of� the�

�CORE� ONLY�

�1.8V�

�+�

�-�

�OVP�

�VDDPWRGD�

�inductors,� the� number� of� active� channels,� the� DC� gain� of� the�

�inductor� RC� filter� and� the� R� SET� resistor.� The� overcurrent� trip�

�threshold� is� shown� in� Equation� 20.�

�I� OCP� =� 100� μ� A� ?� ?� ?� ?� ----------� ?� R� SET� ?� –� ----------------------------------------� ?� ----------------�

�N� 1� 3� V� IN� –� N� ?� V� OUT� V� OUT�

�DCR� K� ?� 400�

�?�

�2� ?� L� ?� f� S�

�DAC� +� 250mV�

�-�

�+�

�OV�

�-------------� ----�

�V� IN�

�(EQ.� 20)�

�-�

�VSEN�

�+�

�UV�

�Where:�

�R� 2�

�DAC� -� 300mV�

�ISL6323B� INTERNAL� CIRCUITRY�

�K� =� ---------------------�

�R� 1� +� R� 2�

�See� “Continuous� Current� Sampling”� on�

�page� 14.�

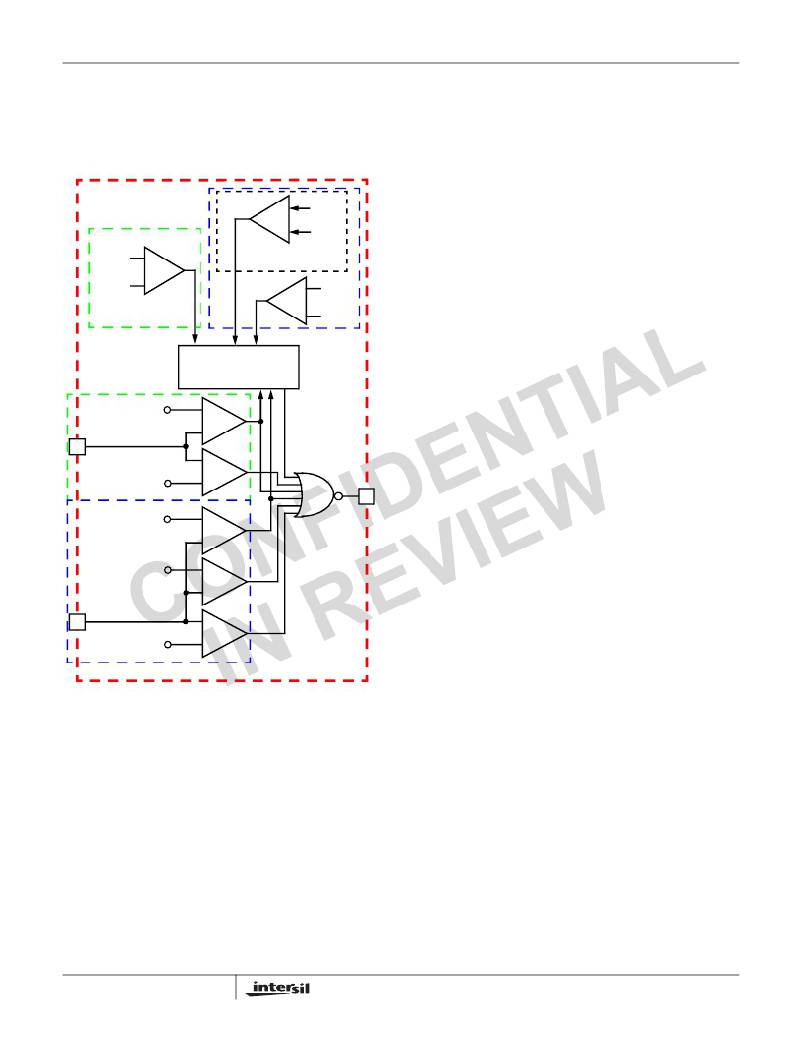

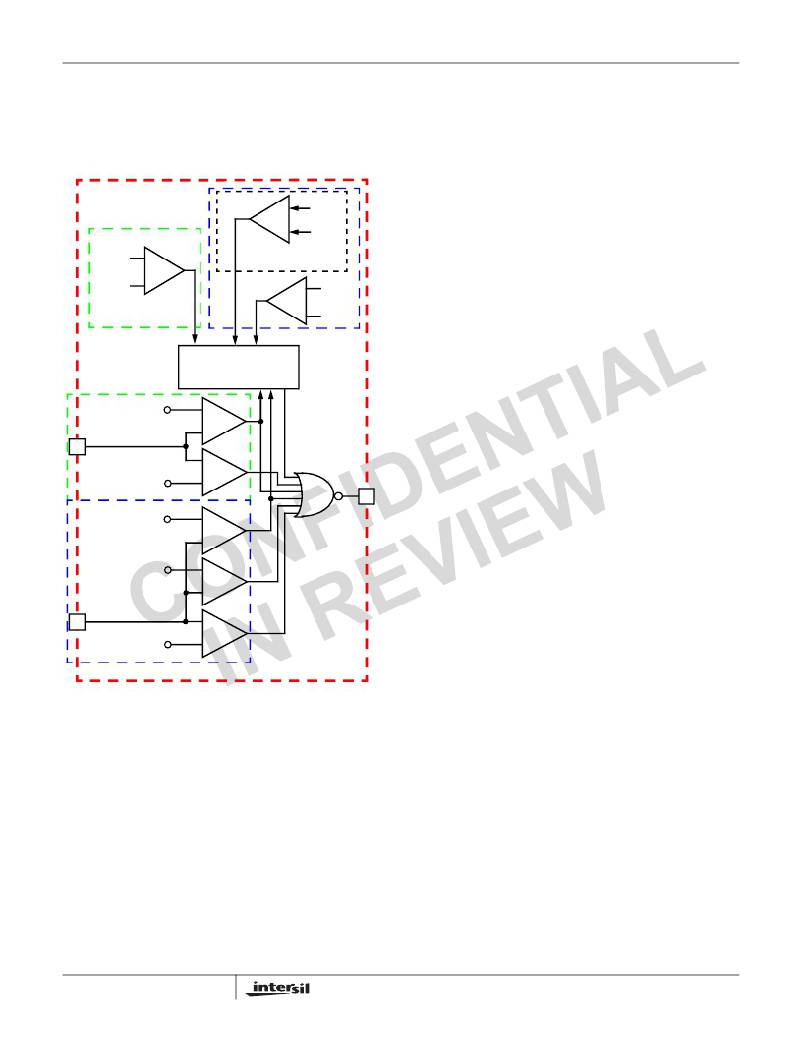

�FIGURE� 15.� POWER-GOOD� AND� PROTECTION� CIRCUITRY�

�Pre-POR� Overvoltage� Protection�

�Prior� to� PVCC� and� VCC� exceeding� their� POR� levels,� the�

�ISL6323B� is� designed� to� protect� either� load� from� any�

�overvoltage� events� that� may� occur.� This� is� accomplished� by�

�means� of� an� internal� 10k� Ω� resistor� tied� from� PHASE� to�

�LGATE,� which� turns� on� the� lower� MOSFET� to� control� the�

�output� voltage� until� the� overvoltage� event� ceases� or� the� input�

�power� supply� cuts� off.� For� complete� protection,� the� low� side�

�MOSFET� should� have� a� gate� threshold� well� below� the�

�maximum� voltage� rating� of� the� load/microprocessor.�

�In� the� event� that� during� normal� operation� the� PVCC� or� VCC�

�voltage� falls� back� below� the� POR� threshold,� the� pre-POR�

�overvoltage� protection� circuitry� reactivates� to� protect� from�

�any� more� pre-POR� overvoltage� events.�

�24�

�f� SW� =� Switching� Frequency�

�Equation� 20� is� valid� for� both� the� Core� regulator� and� the�

�North� Bridge� regulator.� This� equation� includes� the� DC� load�

�current� as� well� as� the� total� ripple� current� contributed� by� all�

�the� phases.� For� the� North� Bridge� regulator,� N� is� 1.�

�During� soft-start,� the� overcurrent� trip� point� is� boosted� by� a� factor�

�of� 1.4.� Instead� of� comparing� the� average� measured� current� to�

�100μA,� the� average� current� is� compared� to� 140μA.� Immediately�

�after� soft-start� is� over,� the� comparison� level� changes� to� 100μA.�

�This� is� done� to� allow� for� start-up� into� an� active� load� while� still�

�supplying� output� capacitor� in-rush� current.�

�CORE� REGULATOR� OVERCURRENT�

�At� the� beginning� of� overcurrent� shutdown,� the� controller� sets� all�

�of� the� UGATE� and� LGATE� signals� low,� puts� PWM3� and� PWM4�

�FN6879.1�

�May� 12,� 2010�

�相关PDF资料 |

PDF描述 |

|---|---|

| ISL6323ACRZ-T | IC PWM CTRLR SYNC BUCK DL 48QFN |

| ESM36DRSH | CONN EDGECARD 72POS DIP .156 SLD |

| LT1529CQ-3.3#PBF | IC REG LDO 3.3V 3A DDPAK-5 |

| LT1764AET-3.3#PBF | IC REG LDO 3.3V 3A TO220-5 |

| ISL6323CRZ-T | IC HYBRID CTRLR PWM MONO 48-QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6323BCRZ-TR5381 | 制造商:Intersil Corporation 功能描述:4+1 PHASE CONT. FOR CORE+NORTHBRIDGE, 2 PHASE PSI, 3.4MHZ S - Tape and Reel 制造商:Intersil Corporation 功能描述:IC PWM CTRLR SYNC BUCK DL 48QFN 制造商:Intersil 功能描述:4+1 PHS CONT CORE + NORTHBRDG PROG |

| ISL6323BCRZ-TR5453 | 制造商:Intersil Corporation 功能描述:STD. ISL6323BCRZ-T WITH GOLD BOND WIRE ONLY, T&R - Tape and Reel |

| ISL6323BIRZ | 功能描述:IC PWM CTRLR SYNC BUCK DL 48QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 标准包装:43 系列:- 应用:控制器,Intel VR11 输入电压:5 V ~ 12 V 输出数:1 输出电压:0.5 V ~ 1.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-VFQFN 裸露焊盘 供应商设备封装:48-QFN(7x7) 包装:管件 |

| ISL6323BIRZR5381 | 制造商:Intersil Corporation 功能描述:4+1 PHASE CONT. FOR CORE+NORTHBRIDGE, 2 PHASE PSI, 3.4MHZ SV - Rail/Tube 制造商:Intersil Corporation 功能描述:IC PWM CTRLR SYNC BUCK DL 48QFN 制造商:Intersil 功能描述:4+1 PHS CONT CORE + NORTHBRDG PROG |

| ISL6323BIRZ-T | 功能描述:IC PWM CTRLR SYNC BUCK DL 48QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 标准包装:43 系列:- 应用:控制器,Intel VR11 输入电压:5 V ~ 12 V 输出数:1 输出电压:0.5 V ~ 1.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-VFQFN 裸露焊盘 供应商设备封装:48-QFN(7x7) 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。