参数资料

| 型号: | ISL6323IRZ-T |

| 厂商: | Intersil |

| 文件页数: | 17/36页 |

| 文件大小: | 0K |

| 描述: | IC HYBRID CTRLR PWM MONO 48-QFN |

| 标准包装: | 4,000 |

| 应用: | 控制器,AMD SVI |

| 输入电压: | 5 V ~ 12 V |

| 输出数: | 2 |

| 输出电压: | 最高 2V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-VFQFN 裸露焊盘 |

| 供应商设备封装: | 48-QFN(7x7) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

�� �

�

�

�ISL6323�

�PRE-PWROK� METAL� VID�

�Typical� motherboard� start-up� occurs� with� the� VFIXEN� input�

�low.� The� controller� decodes� the� SVC� and� SVD� inputs� to�

�determine� the� Pre-PWROK� metal� VID� setting.� Once� the�

�POR� circuitry� is� satisfied,� the� ISL6323� begins� decoding� the�

�inputs� per� Table� 2.� Once� the� EN� input� exceeds� the� rising�

�enable� threshold,� the� ISL6323� saves� the� Pre-PWROK� metal�

�VID� value� in� an� on-board� holding� register� and� passes� this�

�internal� soft-start� circuitry� slowly� stair� steps� the� reference� up�

�to� the� target� value� and� this� results� in� a� controlled� ramp� of� the�

�power� planes.� Once� soft-start� has� ended� and� both� output�

�planes� are� within� regulation� limits,� the� VDDPWRGD� pin�

�transitions� high.� If� the� EN� input� falls� below� the� enable� falling�

�threshold,� then� the� controller� ramps� both� VDD� and� VDDNB�

�down� to� near� zero.�

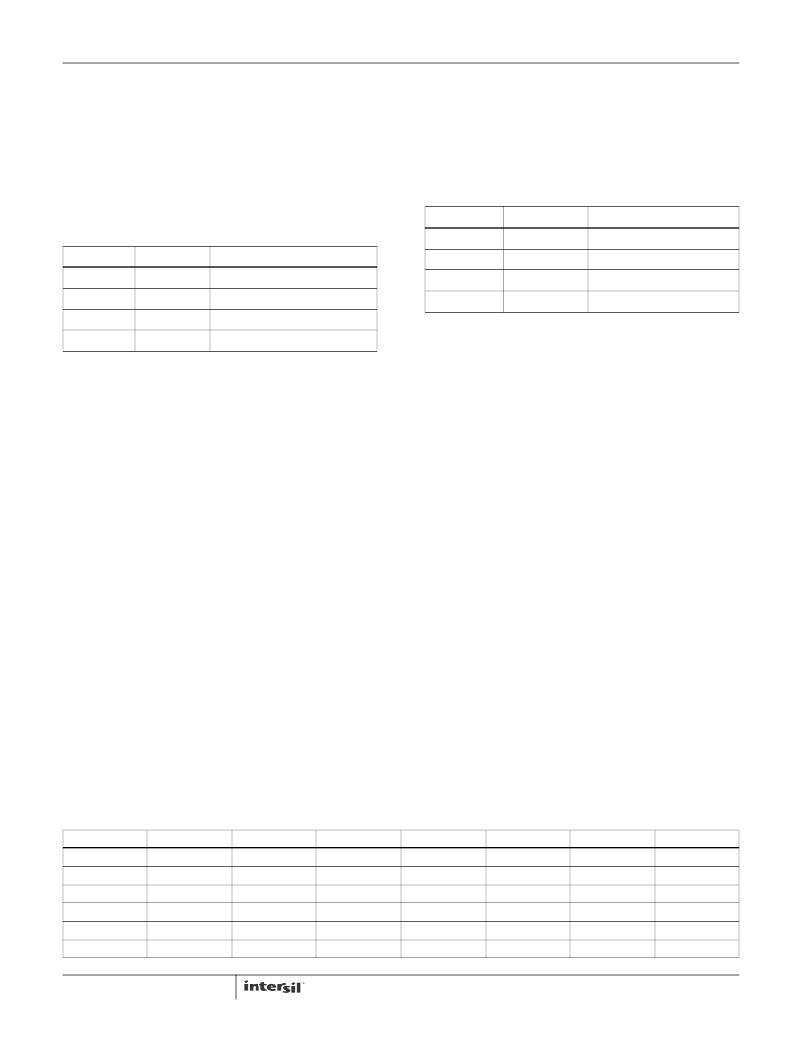

�TABLE� 3.� VFIXEN� VID� CODES�

�target� to� the� internal� DAC� circuitry.�

�TABLE� 2.� PRE-PWROK� METAL� VID� CODES�

�SVC�

�0�

�SVD�

�0�

�OUTPUT� VOLTAGE� (V)�

�1.4�

�SVC�

�0�

�0�

�SVD�

�0�

�1�

�OUTPUT� VOLTAGE� (V)�

�1.1�

�1.0�

�0�

�1�

�1�

�1�

�0�

�1�

�1.2�

�1.0�

�0.8�

�1�

�0�

�0.9�

�1�

�1�

�0.8�

�SVI� MODE�

�Once� the� controller� has� successfully� soft-started� and�

�The� Pre-PWROK� metal� VID� code� is� decoded� and� latched� on�

�the� rising� edge� of� the� enable� signal.� Once� enabled,� the�

�ISL6323� passes� the� Pre-PWROK� metal� VID� code� on� to�

�internal� DAC� circuitry.� The� internal� DAC� circuitry� begins� to�

�ramp� both� the� VDD� and� VDDNB� planes� to� the� decoded�

�Pre-PWROK� metal� VID� output� level.� The� digital� soft-start�

�circuitry� actually� stair� steps� the� internal� reference� to� the�

�target� gradually� over� a� fix� interval.� The� controlled� ramp� of�

�both� output� voltage� planes� reduces� in-rush� current� during�

�the� soft-start� interval.� At� the� end� of� the� soft-start� interval,� the�

�VDDPWRGD� output� transitions� high� indicating� both� output�

�planes� are� within� regulation� limits.�

�If� the� EN� input� falls� below� the� enable� falling� threshold,� the�

�ISL6323� ramps� the� internal� reference� voltage� down� to� near�

�zero.� The� VDDPWRGD� de-asserts� with� the� loss� of� enable.�

�The� VDD� and� VDDNB� planes� will� linearly� decrease� to� near�

�zero.�

�VFIX� MODE�

�In� VFIX� Mode,� the� SVC,� SVD� and� VFIXEN� inputs� are� fixed�

�external� to� the� controller� through� jumpers� to� either� GND� or�

�VDDIO.� These� inputs� are� not� expected� to� change,� but� the�

�ISL6323� is� designed� to� support� the� potential� change� of� state�

�of� these� inputs.� If� VFIXEN� is� high,� the� IC� decodes� the� SVC�

�and� SVD� states� per� Table� 3.�

�Once� enabled,� the� ISL6323� begins� to� soft-start� both� VDD�

�and� VDDNB� planes� to� the� programmed� VFIX� level.� The�

�VDDPWRGD� transitions� high,� the� Northbridge� SVI� interface�

�can� assert� PWROK� to� signal� the� ISL6323� to� prepare� for� SVI�

�commands.� The� controller� actively� monitors� the� SVI�

�interface� for� set� VID� commands� to� move� the� plane� voltages�

�to� start-up� VID� values.� Details� of� the� SVI� Bus� protocol� are�

�provided� in� the� AMD� Design� Guide� for� Voltage� Regulator�

�Controllers� Accepting� Serial� VID� Codes� specification.�

�Once� the� set� VID� command� is� received,� the� ISL6323�

�decodes� the� information� to� determine� which� plane� and� the�

�VID� target� required.� See� Table� 4.� The� internal� DAC� circuitry�

�steps� the� required� output� plane� voltage� to� the� new� VID� level.�

�During� this� time� one� or� both� of� the� planes� could� be� targeted.�

�In� the� event� the� core� voltage� plane,� VDD,� is� commanded� to�

�power� off� by� serial� VID� commands,� the� VDDPWRGD� signal�

�remains� asserted.� The� Northbridge� voltage� plane� must�

�remain� active� during� this� time.�

�If� the� PWROK� input� is� de-asserted,� then� the� controller� steps�

�both� VDD� and� VDDNB� planes� back� to� the� stored�

�Pre-PWROK� metal� VID� level� in� the� holding� register� from�

�initial� soft-start.� No� attempt� is� made� to� read� the� SVC� and�

�SVD� inputs� during� this� time.� If� PWROK� is� reasserted,� then�

�the� on-board� SVI� interface� waits� for� a� set� VID� command.�

�If� VDDPWRGD� deasserts� during� normal� operation,� both�

�voltage� planes� are� powered� down� in� a� controlled� fashion.�

�The� internal� DAC� circuitry� stair� steps� both� outputs� down� to�

�near� zero.�

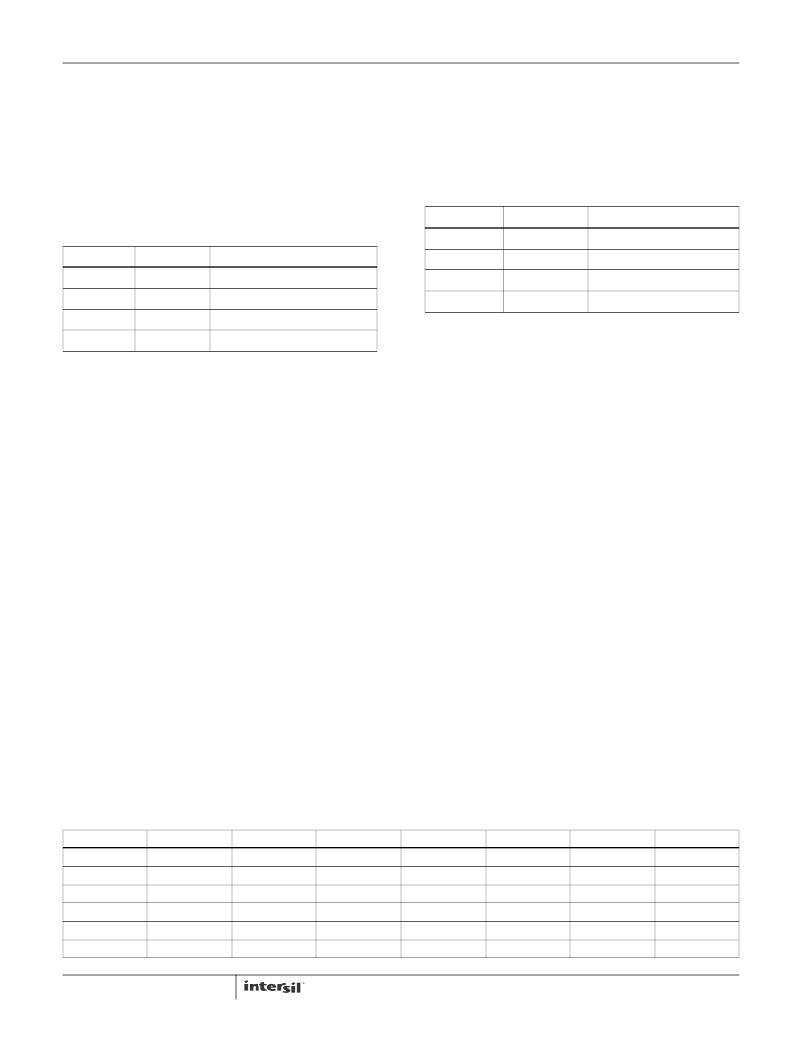

�TABLE� 4.� SERIAL� VID� CODES�

�SVID[6:0]�

�000_0000b�

�000_0001b�

�000_0010b�

�000_0011b�

�000_0100b�

�000_0101b�

�VOLTAGE� (V)�

�1.5500�

�1.5375�

�1.5250�

�1.5125�

�1.5000�

�1.4875�

�SVID[6:0]�

�010_0000b�

�010_0001b�

�010_0010b�

�010_0011b�

�010_0100b�

�010_0101b�

�VOLTAGE� (V)�

�1.1500�

�1.1375�

�1.1250�

�1.1125�

�1.1000�

�1.0875�

�SVID[6:0]�

�100_0000b�

�100_0001b�

�100_0010b�

�100_0011b�

�100_0100b�

�100_0101b�

�VOLTAGE� (V)�

�0.7500�

�0.7375�

�0.7250�

�0.7125�

�0.7000�

�0.6875�

�SVID[6:0]�

�110_0000b�

�110_0001b�

�110_0010b�

�110_0011b�

�110_0100b�

�110_0101b�

�VOLTAGE� (V)�

�0.3500*�

�0.3375*�

�0.3250*�

�0.3125*�

�0.3000*�

�0.2875*�

�17�

�FN9278.5�

�May� 17,� 2011�

�相关PDF资料 |

PDF描述 |

|---|---|

| ADP1715ARMZ-3.0-R7 | IC REG LDO 3V .5A 8-MSOP |

| ISL62882IRTZ-T | IC REG PWM 2PHASE BUCK 40TQFN |

| ISL62882HRTZ-T | IC REG PWM 2PHASE BUCK 40TQFN |

| 2512-123K | INDUCTOR POWER 12UH MOLDED SMD |

| RBM40DTMS-S189 | CONN EDGECARD 80POS R/A .156 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6324ACRZ | 功能描述:IC HYBRID CTRLR PWM DUAL 48QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 标准包装:43 系列:- 应用:控制器,Intel VR11 输入电压:5 V ~ 12 V 输出数:1 输出电压:0.5 V ~ 1.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-VFQFN 裸露焊盘 供应商设备封装:48-QFN(7x7) 包装:管件 |

| ISL6324ACRZR5381 | 制造商:Intersil Corporation 功能描述:4+1 PHASE CONTROLLER, CORE+NORTHBRIDGE, PROG PSI, 3.4MHZ SVI - Rail/Tube 制造商:Intersil Corporation 功能描述:IC HYBRID CTRLR PWM DUAL 48QFN |

| ISL6324ACRZ-T | 功能描述:IC HYBRID CTRLR PWM DUAL 48QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 标准包装:43 系列:- 应用:控制器,Intel VR11 输入电压:5 V ~ 12 V 输出数:1 输出电压:0.5 V ~ 1.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-VFQFN 裸露焊盘 供应商设备封装:48-QFN(7x7) 包装:管件 |

| ISL6324ACRZ-TR5381 | 制造商:Intersil Corporation 功能描述:4+1 PHASE CONT., CORE + NORTHBRIDGE, PROG PSI, 3.4MHZ SVI, 5 - Tape and Reel 制造商:Intersil Corporation 功能描述:IC HYBRID CTRLR PWM DUAL 48QFN |

| ISL6324AIRZ | 功能描述:IC HYBRID CTRLR PWM DUAL 48QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 标准包装:43 系列:- 应用:控制器,Intel VR11 输入电压:5 V ~ 12 V 输出数:1 输出电压:0.5 V ~ 1.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-VFQFN 裸露焊盘 供应商设备封装:48-QFN(7x7) 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。