- 您现在的位置:买卖IC网 > Datasheet目录334 > ISL6442EVAL1Z (Intersil)EVAL BOARD FOR ISL6442 Datasheet资料下载

参数资料

| 型号: | ISL6442EVAL1Z |

| 厂商: | Intersil |

| 文件页数: | 13/16页 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD FOR ISL6442 |

| 标准包装: | 1 |

| 主要目的: | DC/DC,LDO 步降 |

| 输出及类型: | 3,非隔离 |

| 输出电压: | 1.8V,3.3V,5V |

| 电流 - 输出: | 3A,3A,300mA |

| 输入电压: | 6V |

| 稳压器拓扑结构: | 降压 |

| 频率 - 开关: | 1.4MHz |

| 板类型: | 完全填充 |

| 已供物品: | 板 |

| 已用 IC / 零件: | ISL6442 |

�� �

�

�

�ISL6442�

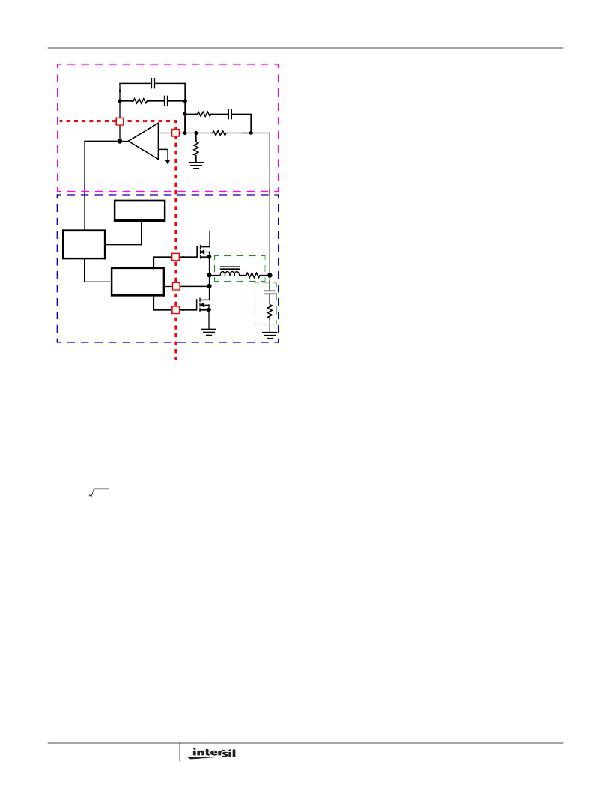

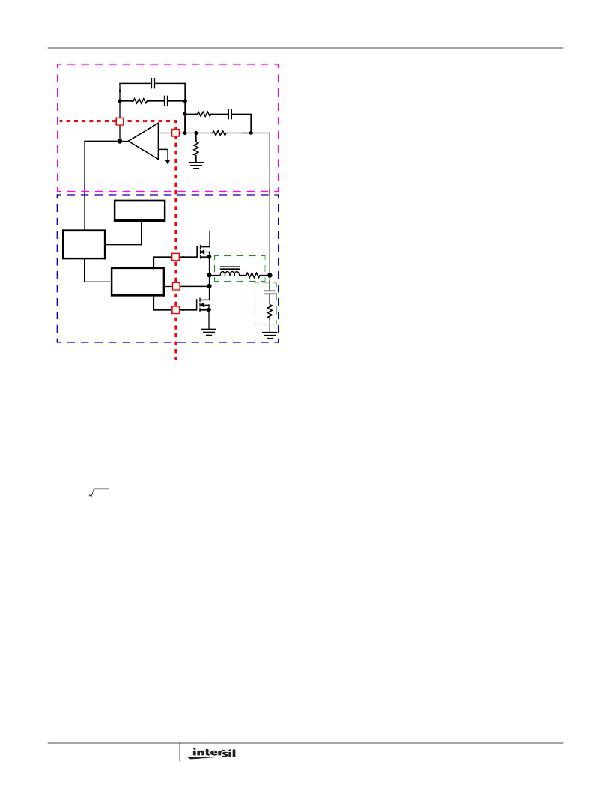

�to� the� FB� pin,� Ro� in� Figure� 14,� the� design� procedure� can�

�C2�

�be� followed� as� presented� in� Equation� 12.�

�V� OSC� ?� R1� ?� F� 0�

�d� MAX� ?� V� IN� ?� F� LC�

�COMP�

�R2�

�C1�

�R3�

�C3�

�R2� =� ---------------------------------------------�

�(EQ.� 12)�

�E/A�

�-�

�+�

�FB�

�Ro�

�R1�

�2.� Calculate� C1� such� that� F� Z1� is� placed� at� a� fraction� of� the� F� LC� ,�

�at� 0.1� to� 0.75� of� F� LC� (to� adjust,� change� the� 0.5� factor� to�

�desired� number).� The� higher� the� quality� factor� of� the� output�

�filter� and/or� the� higher� the� ratio� F� CE� /F� LC� ,� the� lower� the� F� Z1�

�VREF�

�frequency� (to� maximize� phase� boost� at� F� LC� ).�

�C1� =� ------------------------------------------------�

�1�

�2� π� ?� R2� ?� 0.5� ?� F� LC�

�(EQ.� 13)�

�C2� =� ---------------------------------------------------------�

�PWM�

�CIRCUIT�

�OSCILLATOR�

�V� OSC�

�V� IN�

�V� OUT�

�3.� Calculate� C2� such� that� F� P1� is� placed� at� F� CE� .�

�C1�

�2� π� ?� R2� ?� C1� ?� F� CE� –� 1�

�(EQ.� 14)�

�UGATE�

�L�

�D�

�4.� Calculate� R3� such� that� F� Z2� is� placed� at� F� LC� .� Calculate� C3�

�HALF-BRIDGE�

�DRIVE�

�PHASE�

�LGATE�

�C�

�E�

�such� that� F� P2� is� placed� below� F� SW� (typically,� 0.5� to� 1.0�

�times� F� SW� ).� F� SW� represents� the� switching� frequency.�

�Change� the� numerical� factor� to� reflect� desired� placement�

�of� this� pole.� Placement� of� F� P2� lower� in� frequency� helps�

�reduce� the� gain� of� the� compensation� network� at� high�

�frequency,� in� turn� reducing� the� HF� ripple� component� at�

�ISL6442�

�EXTERNAL� CIRCUIT�

�the� COMP� pin� and� minimizing� resultant� duty� cycle� jitter.�

�R3� =� ----------------------�

�F� SW�

�C3� =� -------------------------------------------------�

�FIGURE� 14.� VOLTAGE-MODE� BUCK� CONVERTER�

�COMPENSATION� DESIGN�

�R1�

�------------� –� 1�

�F� LC�

�1�

�2� π� ?� R3� ?� 0.7� ?� F� SW�

�(EQ.� 15)�

�The� modulator� transfer� function� is� the� small-signal� transfer�

�function� of� V� OUT� /V� COMP� .� This� function� is� dominated� by� a� DC�

�gain,� given� by� d� MAX� V� IN� /V� OSC� ,� and� shaped� by� the� output�

�filter,� with� a� double� pole� break� frequency� at� F� LC� and� a� zero� at�

�F� CE� .� For� the� purpose� of� this� analysis,� L� and� D� represent� the�

�channel� inductance� and� its� DCR,� while� C� and� E� represent� the�

�total� output� capacitance� and� its� equivalent� series� resistance.�

�It� is� recommended� a� mathematical� model� is� used� to� plot� the�

�loop� response.� Check� the� loop� gain� against� the� error�

�amplifier� ’s� open-loop� gain.� Verify� phase� margin� results� and�

�adjust� as� necessary.� The� following� equations� describe� the�

�frequency� response� of� the� modulator� (G� MOD� ),� feedback�

�compensation� (G� FB� )� and� closed-loop� response� (G� CL� ):�

�F� LC� =� ---------------------------�

�G� MOD� (� f� )� =� ------------------------------� ?� ----------------------------------------------------------------------------------------�

�V� OSC�

�1� +� s� (� f� )� ?� (� E� +� D� )� ?� C� +� s� (� f� )� ?� L� ?� C�

�F� CE� =� ------------------------�

�1�

�2� π� ?� L� ?� C�

�1�

�2� π� ?� C� ?� E�

�(EQ.� 10)�

�(EQ.� 11)�

�d� MAX� ?� V� IN� 1� +� s� (� f� )� ?� E� ?� C�

�2�

�(EQ.� 16)�

�G� FB� (� f� )� =� ------------------------------------------------------� ?�

�?� -----------------------------------------------------------------------------------------------------------------------------�

�(� 1� +� s� (� f� )� ?� R3� ?� C3� )� ?� ?� 1� +� s� (� f� )� ?� R2� ?� ?� ----------------------�

�The� compensation� network� consists� of� the� error� amplifier�

�(internal� to� the� ISL6442)� and� the� external� R1-R3,� C1-C3�

�components.� The� goal� of� the� compensation� network� is� to�

�provide� a� closed� loop� transfer� function� with� high� 0dB� crossing�

�frequency� (F� 0� ;� typically� 0.1� to� 0.3� of� F� SW� )� and� adequate� phase�

�margin� (better� than� 45°).� Phase� margin� is� the� difference�

�between� the� closed� loop� phase� at� F� 0dB� and� 180°.� The�

�equations� that� follow� relate� the� compensation� network’s� poles,�

�zeros� and� gain� to� the� components� (R1,� R2,� R3,� C1,� C2,� and�

�C3)� in� Figure� 14.� Use� the� following� guidelines� for� locating� the�

�poles� and� zeros� of� the� compensation� network:�

�1.� Select� a� value� for� R1� (1k� Ω� to� 5k� Ω� ,� typically).� Calculate�

�value� for� R2� for� desired� converter� bandwidth� (F� 0� ).� If�

�setting� the� output� voltage� via� an� offset� resistor� connected�

�1� +� s� (� f� )� ?� R2� ?� C1�

�s� (� f� )� ?� R1� ?� (� C1� +� C2� )�

�1� +� s� (� f� )� ?� (� R1� +� R3� )� ?� C3�

�?� ?� C1� +� C2� ?� ?�

�G� CL� (� f� )� =� G� MOD� (� f� )� ?� G� FB� (� f� )�

�where:�

�s� (� f� )� =� 2� π� ?� f� ?� j�

�C1� ?� C2� ?� ?�

�(EQ.� 17)�

�(EQ.� 18)�

�13�

�FN9204.2�

�October� 31,� 2008�

�相关PDF资料 |

PDF描述 |

|---|---|

| ISL6445EVAL3Z | EVALUATION BOARD FOR ISL6445 |

| ISL6524EVAL1 | EVALUATION BOARD VRM8.5 ISL6524 |

| ISL6527EVAL1 | EVALUATION BOARD SOIC ISL6527 |

| ISL6532AEVAL1 | EVALUATION BOARD 1 ISL6532A |

| ISL6553EVAL1 | EVALUATION BOARD ISL6553 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6442IA | 功能描述:IC REG TRPL BCK/LINEAR 24QSOP RoHS:否 类别:集成电路 (IC) >> PMIC - 稳压器 - 线性 + 切换式 系列:- 标准包装:2,500 系列:- 拓扑:降压(降压)同步(3),线性(LDO)(2) 功能:任何功能 输出数:5 频率 - 开关:300kHz 电压/电流 - 输出 1:控制器 电压/电流 - 输出 2:控制器 电压/电流 - 输出 3:控制器 带 LED 驱动器:无 带监控器:无 带序列发生器:是 电源电压:5.6 V ~ 24 V 工作温度:-40°C ~ 85°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

| ISL6442IA-TK | 功能描述:IC REG TRPL BCK/LINEAR 24QSOP RoHS:否 类别:集成电路 (IC) >> PMIC - 稳压器 - 线性 + 切换式 系列:- 标准包装:2,500 系列:- 拓扑:降压(降压)同步(3),线性(LDO)(2) 功能:任何功能 输出数:5 频率 - 开关:300kHz 电压/电流 - 输出 1:控制器 电压/电流 - 输出 2:控制器 电压/电流 - 输出 3:控制器 带 LED 驱动器:无 带监控器:无 带序列发生器:是 电源电压:5.6 V ~ 24 V 工作温度:-40°C ~ 85°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

| ISL6442IAZ | 功能描述:IC REG TRPL BCK/LINEAR 24QSOP RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 线性 + 切换式 系列:- 标准包装:2,500 系列:- 拓扑:降压(降压)同步(3),线性(LDO)(2) 功能:任何功能 输出数:5 频率 - 开关:300kHz 电压/电流 - 输出 1:控制器 电压/电流 - 输出 2:控制器 电压/电流 - 输出 3:控制器 带 LED 驱动器:无 带监控器:无 带序列发生器:是 电源电压:5.6 V ~ 24 V 工作温度:-40°C ~ 85°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

| ISL6442IAZ-TK | 功能描述:IC REG TRPL BCK/LINEAR 24QSOP RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 线性 + 切换式 系列:- 标准包装:2,500 系列:- 拓扑:降压(降压)同步(3),线性(LDO)(2) 功能:任何功能 输出数:5 频率 - 开关:300kHz 电压/电流 - 输出 1:控制器 电压/电流 - 输出 2:控制器 电压/电流 - 输出 3:控制器 带 LED 驱动器:无 带监控器:无 带序列发生器:是 电源电压:5.6 V ~ 24 V 工作温度:-40°C ~ 85°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

| ISL6442IAZ-TKS2715 | 制造商:Intersil Corporation 功能描述:BROADCOM, ISL6442IAZ-TK BUSINESS TRACKING REQUIREMENTS, SOLD - Tape and Reel |

发布紧急采购,3分钟左右您将得到回复。