参数资料

| 型号: | ISL6563IR-T |

| 厂商: | Intersil |

| 文件页数: | 12/19页 |

| 文件大小: | 0K |

| 描述: | IC CTRLR PWM MULTIPHASE 24-QFN |

| 标准包装: | 6,000 |

| 应用: | 控制器,Intel VRM9,VRM10,AMD Hammer 应用 |

| 输入电压: | 5 V ~ 12 V |

| 输出数: | 1 |

| 输出电压: | 0.8 V ~ 1.85 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 24-VFQFN 裸露焊盘 |

| 供应商设备封装: | 24-QFN(4x4) |

| 包装: | 带卷 (TR) |

�� �

�

�

�ISL6563�

�I� OUT� ?� r� DS� (� ON� )� LMOS�

�2� ?� R� ISEN�

�In� VRM10� setting,� the� ISL6563� checks� for� a� change� in� the� VID�

�code� six� times� each� switching� cycle.� If� a� new� code� is�

�established� and� it� stays� the� same� for� 3� consecutive� readings,�

�the� ISL6563� recognizes� the� change� and� increments� the�

�reference.� Specific� to� VRM10,� the� processor� controls� the� VID�

�transitions� and� is� responsible� for� incrementing� or� decrementing�

�one� VID� step� at� a� time.� In� VRM10� setting,� the� ISL6563� will�

�immediately� change� the� reference� to� the� new� requested� value�

�as� soon� as� the� request� is� validated;� in� cases� where� the�

�reference� step� is� too� large,� the� sudden� change� can� trigger�

�overcurrent� or� overvoltage� events.�

�In� non-VRM10� settings,� due� to� the� way� the� ISL6563�

�recognizes� VID� code� changes,� up� to� one� full� switching�

�period� may� pass� before� a� VID� change� registers.� Thus,� the�

�total� time� required� for� a� VID� change,� t� DVID� ,� is� dependent� on�

�the� switching� frequency� (f� S� ),� the� size� of� the� change� (� Δ� V� ID� ),�

�and� the� time� required� to� register� the� VID� change.� The�

�approximate� time� required� for� an� ISL6563-based� converter�

�in� VRM9� configuration� running� at� typical� f� S� (222kHz)� to�

�perform� a� 1.5V-to-1.7V� reference� voltage� change� is� about�

�196� μ� s,� as� calculated� using� Equation� 7� (this� example� is� also�

�illustrated� in� Figure� 5).�

�drops� below� the� OV� comparator� ’s� hysteretic� threshold.� The�

�OVP� process� repeats� if� the� voltage� rises� back� above� the�

�designated� threshold.� The� occurrence� of� an� OVP� event� does�

�not� latch� the� controller;� should� the� phenomenon� be�

�transitory,� the� controller� resumes� normal� operation� following�

�such� an� event.�

�LOAD-LINE� REGULATION�

�In� applications� with� high� transient� current� slew� rates,� the�

�lowest-cost� solution� for� maintaining� regulation� often� requires�

�some� kind� of� controlled� output� impedance.� The� FB� pin� of� the�

�ISL6563� carries� a� current� proportional� to� the� average� output�

�current� of� the� converter.� The� current� is� equivalent� to� I� FB� in�

�Figure� 1.� Forcing� I� FB� into� the� summing� node� of� the� error�

�amplifier� produces� a� voltage� drop� across� the� feedback� resistor,�

�R� FB� ,� proportional� to� the� output� current.� Assuming� the� current� is�

�shared� equally� by� both� phases,� the� steady-state� value� of�

�V� DROOP� is� simply:�

�V� DROOP� =� I� FB� ?� R� FB�

�(EQ.� 8)�

�V� DROOP� =� ---------------------------------------------------------� ?� R� FB�

�t� DVID� ?� -----� ?� ---------------------� +� 13� ?�

�1� ?� 4� Δ� V� VID� ?�

�f� S� ?� 0.025� ?�

�(EQ.� 7)�

�ON/OFF� CONTROL�

�The� internal� power-on� reset� circuit� (POR)� prevents� the�

�OVERVOLTAGE� PROTECTION�

�The� ISL6563� benefits� from� a� multi-tiered� approach� to�

�overvoltage� protection.�

�A� pre-POR� mechanism� is� at� work� while� the� chip� does� not�

�have� sufficient� bias� voltage� to� initiate� an� active� response� to�

�an� OV� situation.� Thus,� while� VCC� is� below� its� POR� level,� the�

�lower� drives� are� tristated� and� internal� 5k� Ω� (typically)�

�resistors� are� connected� from� PHASE� to� their� respective�

�LGATE� pins.� As� a� result,� output� voltage,� duplicated� at� the�

�PHASE� nodes� via� the� output� inductors,� is� effectively�

�clamped� at� the� lower� MOSFETs’� threshold� level.� This�

�ISL6563� from� starting� before� the� bias� voltage� at� VCC� and�

�PVCC� reach� the� rising� POR� thresholds,� as� defined� in�

�“Electrical� Specifications”� table� on� page� 4.� The� POR� levels�

�are� sufficiently� high� to� guarantee� that� all� parts� of� the� ISL6563�

�can� perform� their� functions� properly� once� bias� is� applied� to�

�the� part.� While� bias� is� below� the� rising� POR� thresholds,� the�

�controlled� MOSFETs� are� kept� in� an� off� state.�

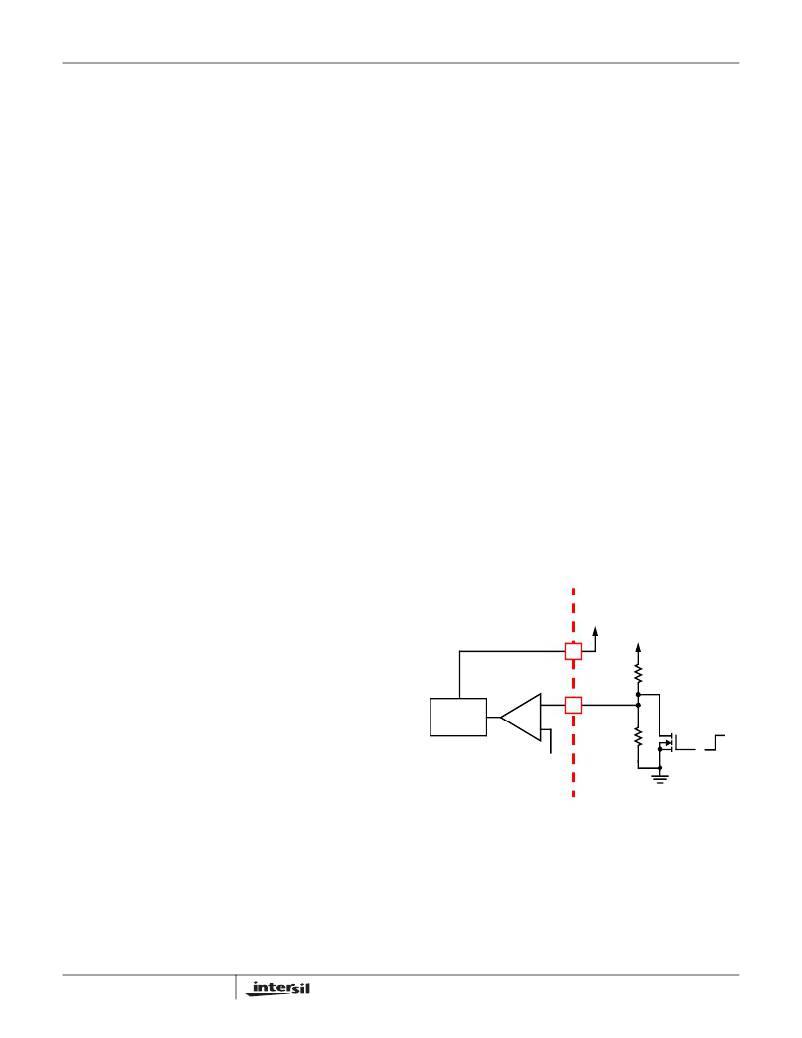

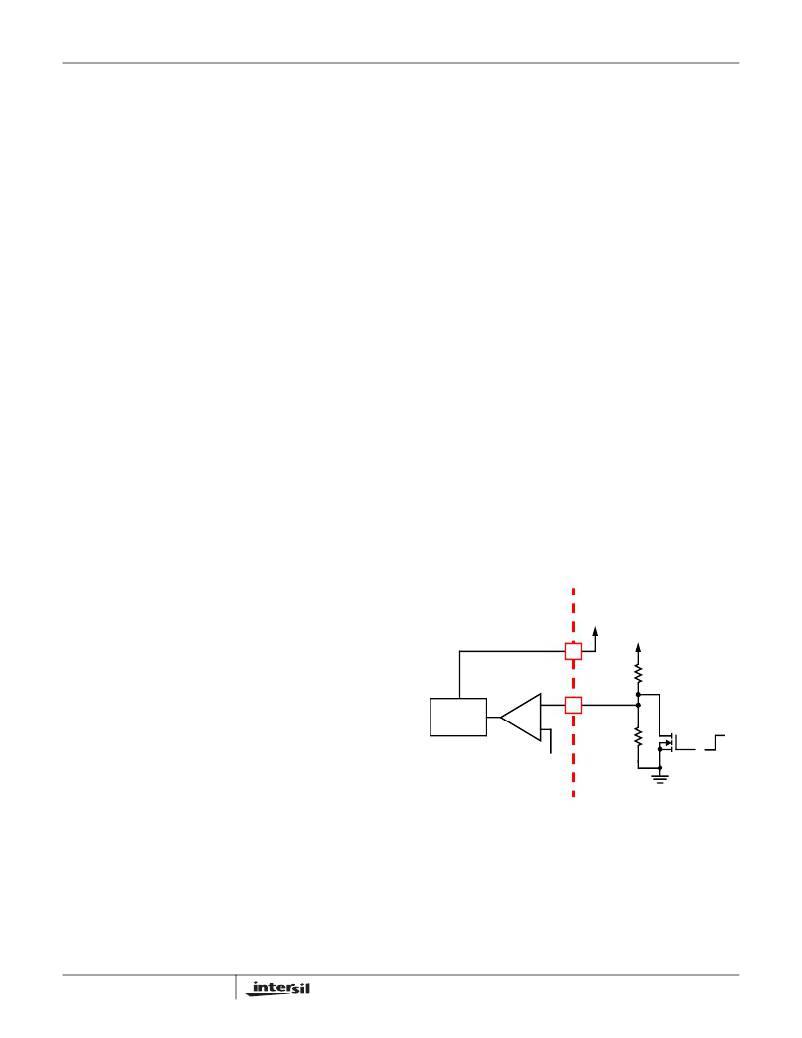

�ISL6563� EXTERNAL� CIRCUIT�

�+5V�

�+12V�

�approach� ensures� no� catastrophic� output� voltage� can� be�

�developed� at� the� output� of� an� ISL6563-based� regulator� (for�

�ENABLE�

�COMPARATOR�

�VCC�

�15k� Ω�

�most� typical� applications).�

�The� pre-POR� mechanism� is� removed� once� the� bias� is� above�

�the� POR� level,� and� a� fixed-threshold� OVP� goes� into� effect.�

�POR�

�CIRCUIT�

�+�

�-�

�ENLL�

�1k� Ω�

�OFF�

�Based� on� the� specific� chip� configuration,� the� OVP� goes� into�

�effect� once� the� voltage� sensed� at� the� FB� pin� exceeds� about�

�1.65V� (Hammer/VR10)� or� 1.95V� (VR9� configuration).� Should�

�0.61V�

�ON�

�the� output� voltage� exceed� these� thresholds,� the� lower�

�MOSFETs� are� turned� on.�

�During� soft-start,� the� OVP� threshold� changes� to� the� higher� of�

�the� fixed� threshold� (1.65V/1.95V)� or� the� DAC� setting� plus�

�200mV.� At� the� end� of� the� soft-start,� the� OVP� threshold�

�changes� to� the� DAC� setting� plus� 200mV.�

�In� any� of� the� described� post-POR� functionality,� OVP� results�

�in� the� turn-on� of� the� lower� MOSFETs.� Once� turned� on,� the�

�lower� MOSFETs� are� only� turned� off� when� the� output� voltage�

�12�

�FIGURE� 6.� START-UP� COORDINATION� USING� THRESHOLD-�

�SENSITIVE� ENABLE� (ENLL)� PIN�

�A� secondary� disablement� feature� is� available� via� the�

�threshold-sensitive� enable� input� (ENLL).� This� optional�

�feature� prevents� the� ISL6563� from� operating� until� a� certain�

�other� voltage� rail� is� available� and� above� some� selectable�

�threshold.� For� example,� when� down-converting� off� a� 12V�

�input,� it� may� be� desirable� the� ISL6563-based� converter� does�

�not� start� up� until� the� power� input� is� sufficiently� high.� The�

�FN9126.8�

�June� 10,� 2010�

�相关PDF资料 |

PDF描述 |

|---|---|

| ISL6564AIRZ | IC REG CTRLR BUCK PWM VM 40-QFN |

| ISL6564IR-T | IC REG CTRLR BUCK PWM VM 40-QFN |

| ISL6565BCV-T | IC REG CTRLR BUCK PWM VM 28TSSOP |

| ISL6566AIRZ | IC CTRLR PWM 3PHASE BUCK 40-QFN |

| ISL6566CRZ-T | IC CTLR PWM BUCK 3PHASE 40-QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6563IRZ | 功能描述:电流型 PWM 控制器 P6 TWO PHS CONT INTEGRTD DRVRS DESKT RoHS:否 制造商:Texas Instruments 开关频率:27 KHz 上升时间: 下降时间: 工作电源电压:6 V to 15 V 工作电源电流:1.5 mA 输出端数量:1 最大工作温度:+ 105 C 安装风格:SMD/SMT 封装 / 箱体:TSSOP-14 |

| ISL6563IRZ-T | 功能描述:电流型 PWM 控制器 P6 TWO PHS CONT INTEGRTD DRVRS DESKT RoHS:否 制造商:Texas Instruments 开关频率:27 KHz 上升时间: 下降时间: 工作电源电压:6 V to 15 V 工作电源电流:1.5 mA 输出端数量:1 最大工作温度:+ 105 C 安装风格:SMD/SMT 封装 / 箱体:TSSOP-14 |

| ISL6564ACRZ | 功能描述:IC REG CTRLR BUCK PWM VM 40-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

| ISL6564ACRZ-T | 功能描述:IC REG CTRLR BUCK PWM VM 40-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

| ISL6564AIRZ | 功能描述:IC REG CTRLR BUCK PWM VM 40-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。