参数资料

| 型号: | ISL6569ACR-T |

| 厂商: | Intersil |

| 文件页数: | 9/22页 |

| 文件大小: | 0K |

| 描述: | IC REG CTRLR BUCK PWM 32-QFN |

| 标准包装: | 6,000 |

| PWM 型: | 电流/电压模式 |

| 输出数: | 1 |

| 频率 - 最大: | 2MHz |

| 占空比: | 75% |

| 电源电压: | 4.75 V ~ 5.25 V |

| 降压: | 是 |

| 升压: | 无 |

| 回扫: | 无 |

| 反相: | 无 |

| 倍增器: | 无 |

| 除法器: | 无 |

| Cuk: | 无 |

| 隔离: | 无 |

| 工作温度: | 0°C ~ 85°C |

| 封装/外壳: | 32-VFQFN 裸露焊盘 |

| 包装: | 带卷 (TR) |

�� �

�

�

�ISL6569A�

�In� addition,� the� peak-to-peak� amplitude� of� the� combined�

�inductor� currents� is� reduced� in� proportion� to� the� number� of�

�phases.� To� understand� the� reduction� of� ripple� current�

�amplitude� in� the� multi-phase� circuit,� examine� the� equation�

�representing� an� individual� channel’s� peak-to-peak� inductor�

�current.�

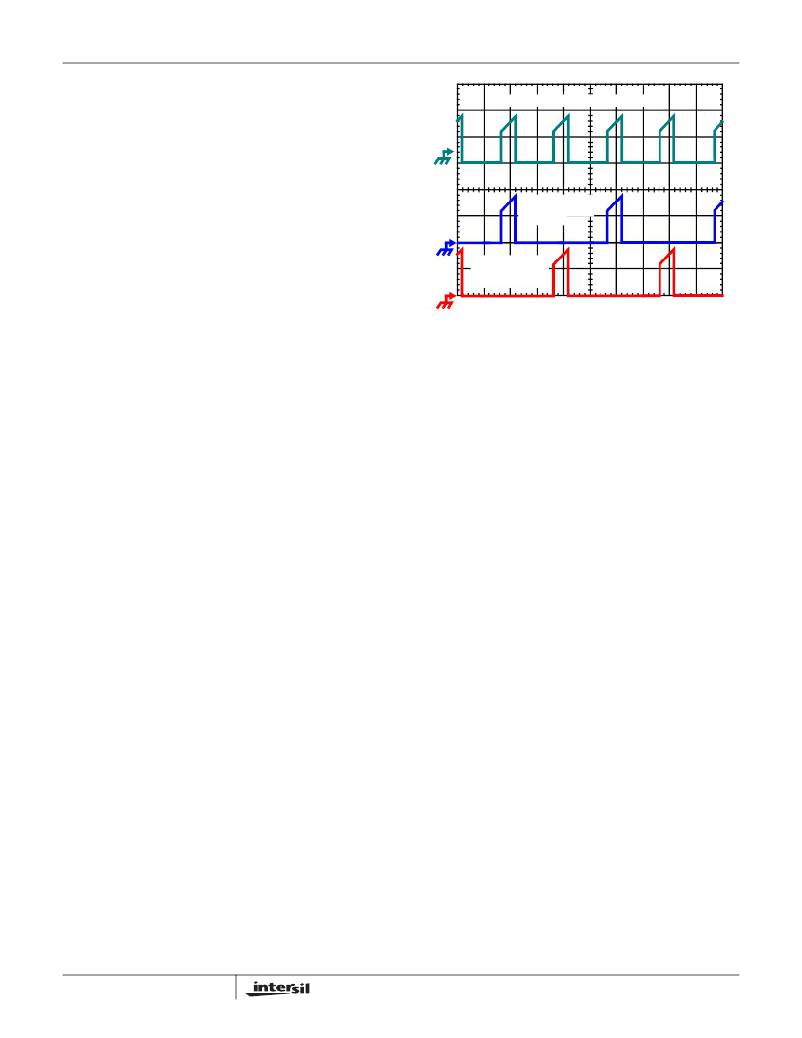

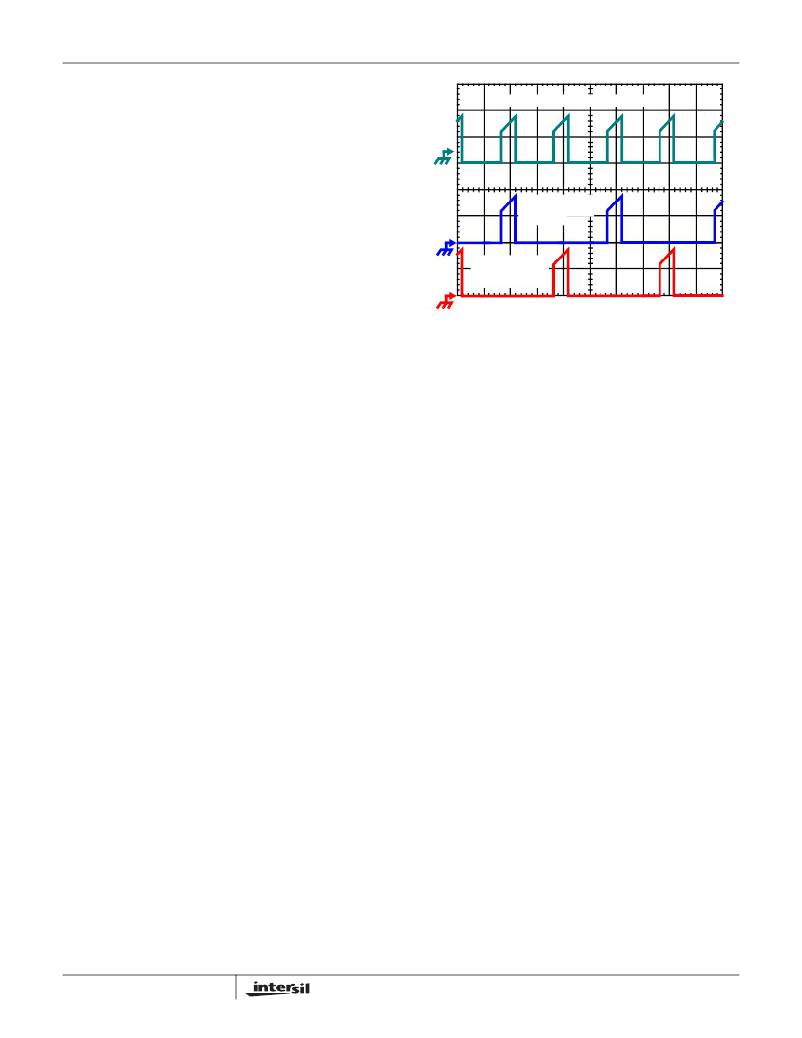

�INPUT-CAPACITOR CURRENT, 10A/DIV�

�(� V� IN� –� V� OUT� )� V� OUT�

�I� PP� =� ------------------------------------------------------�

�L� f� S� V� IN�

�In� Equation� 1,� V� IN� and� V� OUT� are� the� input� and� output�

�(EQ.� 1)�

�CHANNEL� 2�

�INPUT� CURRENT�

�10A/DIV�

�voltages� respectively,� L� is� the� single-channel� inductor� value,�

�and� f� S� is� the� switching� frequency.�

�The� output� capacitors� conduct� the� ripple� component� of� the�

�inductor� current.� In� the� case� of� multi-phase� converters,� the�

�capacitor� current� is� the� sum� of� the� ripple� currents� from� each�

�of� the� individual� channels.� Compare� Equation� 1� to� the�

�expression� for� the� peak-to-peak� current� after� the� summation�

�of� two� symmetrically� phase-shifted� inductor� currents� in�

�Equation� 2.�

�CHANNEL� 1�

�INPUT� CURRENT�

�10A/DIV�

�1� μ� s/DIV�

�FIGURE� 3.� CHANNEL� INPUT� CURRENTS� AND� INPUT-�

�CAPACITOR� RMS� CURRENT� FOR� 3-PHASE�

�CONVERTER�

�L� f� S� V�

�(� V� IN� –� 2� V� OUT� )� V� OUT�

�I� C� ,� PP� =� -----------------------------------------------------------�

�IN�

�(EQ.� 2)�

�PWM� Operation�

�One� switching� cycle� is� defined� as� the� time� between� PWM1�

�pulse� termination� signals.� The� pulse� termination� signal� is�

�Peak-to-peak� ripple� current� decreases� by� an� amount�

�proportional� to� the� number� of� channels.� Output-voltage�

�ripple� is� a� function� of� capacitance,� capacitor� equivalent�

�series� resistance� (ESR),� and� inductor� ripple� current.�

�Reducing� the� inductor� ripple� current� allows� the� designer� to�

�use� fewer� or� less� costly� output� capacitors.�

�Increased� ripple� frequency� and� lower� ripple� amplitude� mean�

�that� the� designer� can� use� less� per-channel� inductance� and�

�lower� total� output� capacitance� for� any� performance�

�an� internally� generated� clock� signal� which� triggers� the�

�falling� edge� of� PWM1.� The� cycle� time� of� the� pulse�

�termination� signal� is� the� inverse� of� the� switching� frequency�

�set� by� the� resistor� between� the� FS/DIS� pin� and� ground.�

�Each� cycle� begins� when� the� clock� signal� commands� the�

�channel-1� PWM� output� to� go� low.� The� PWM1� transition�

�signals� the� channel-1� MOSFET� driver� to� turn� off� the�

�channel-1� upper� MOSFET� and� turn� on� the� channel-1�

�synchronous� MOSFET.� The� PWM2� pulse� terminates� 1/2� of�

�a� cycle� after� PWM1.�

�specification.�

�Once� a� PWM� signal� transitions� low,� it� is� held� low� for� a�

�Another� benefit� of� interleaving� is� to� reduce� input� ripple�

�current.� Input� capacitance� is� determined� in� part� by� the�

�maximum� input� ripple� current.� Multi-phase� topologies� can�

�improve� overall� system� cost� and� size� by� lowering� input� ripple�

�current� and� allowing� the� designer� to� reduce� the� cost� of� input�

�capacitance.� The� example� in� Figure� 3� illustrates� input�

�currents� from� a� two-phase� converter� combining� to� reduce�

�the� total� input� ripple� current.�

�The� converter� depicted� in� Figure� 3� delivers� 36A� to� a� 1.5V�

�load� from� a� 12V� input.� The� RMS� input� capacitor� current� is�

�8.6A.� Compare� this� to� a� single-phase� converter� also�

�stepping� down� 12V� to� 1.5V� at� 36A.� The� single-phase�

�converter� has� 11.9A� RMS� input� capacitor� current.� The�

�single-phase� converter� input� capacitor� bank� must� support�

�38%� more� RMS� current� than� an� equivalent� 2-phase�

�converter.�

�Figure� 16� in� the� section� entitled� Input� Capacitor� Selection�

�can� be� used� to� determine� the� input-capacitor� RMS� current�

�based� on� load� current,� duty� cycle.� It� is� provided� as� an� aid� in�

�determining� the� optimal� input� capacitor� solution.�

�9�

�minimum� of� 1/4� cycle.� This� forced� off� time� is� required� to�

�ensure� an� accurate� current� sample.� Current� sensing� is�

�described� in� the� next� section.� After� the� forced� off� time�

�expires,� the� PWM� output� is� enabled.� The� PWM� output� state�

�is� driven� by� the� position� of� the� error� amplifier� output� signal,�

�V� COMP� ,� minus� the� current� correction� signal� relative� to� the�

�sawtooth� ramp� as� illustrated� in� Figure� 1.� When� the� modified�

�V� COMP� voltage� crosses� the� sawtooth� ramp,� the� PWM�

�output� transitions� high.� The� MOSFET� driver� detects� the�

�change� in� state� of� the� PWM� signal� and� turns� off� the�

�synchronous� MOSFET� and� turns� on� the� upper� MOSFET.�

�The� PWM� signal� will� remain� high� until� the� pulse� termination�

�signal� marks� the� beginning� of� the� next� cycle� by� triggering�

�the� PWM� signal� low.�

�FN9092.2�

�December� 29,� 2004�

�相关PDF资料 |

PDF描述 |

|---|---|

| ISL6569CR-T | IC REG CTRLR DIVIDER PWM 32-QFN |

| ISL6571CRZ | IC MOSF DRVR/SYNC SW COMPL 68QFN |

| ISL6611AIRZ | IC REG CTRLR DOUBLER PWM 16-QFN |

| ISL6617IRZ | IC PWM DOUBLER MONITOR 10DFN |

| ISL6627IRZ-T | IC CONTROLLER VR11.1 VR12 10DFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6569ACRZ | 功能描述:IC REG CTRLR BUCK PWM 32-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

| ISL6569ACRZ-T | 功能描述:IC REG CTRLR BUCK PWM 32-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

| ISL6569CB | 功能描述:IC REG CTRLR DIVIDER PWM 24-SOIC RoHS:否 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:500kHz 占空比:100% 电源电压:8.2 V ~ 30 V 降压:无 升压:无 回扫:是 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:0°C ~ 70°C 封装/外壳:8-DIP(0.300",7.62mm) 包装:管件 产品目录页面:1316 (CN2011-ZH PDF) |

| ISL6569CB-T | 功能描述:IC REG CTRLR DIVIDER PWM 24-SOIC RoHS:否 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:500kHz 占空比:100% 电源电压:8.2 V ~ 30 V 降压:无 升压:无 回扫:是 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:0°C ~ 70°C 封装/外壳:8-DIP(0.300",7.62mm) 包装:管件 产品目录页面:1316 (CN2011-ZH PDF) |

| ISL6569CBZ | 功能描述:IC REG CTRLR DIVIDER PWM 24-SOIC RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。